ECE 353 Introduction to Microprocessor Systems

Last (family) name: ______

First (given) name: ______

Student ID: ______

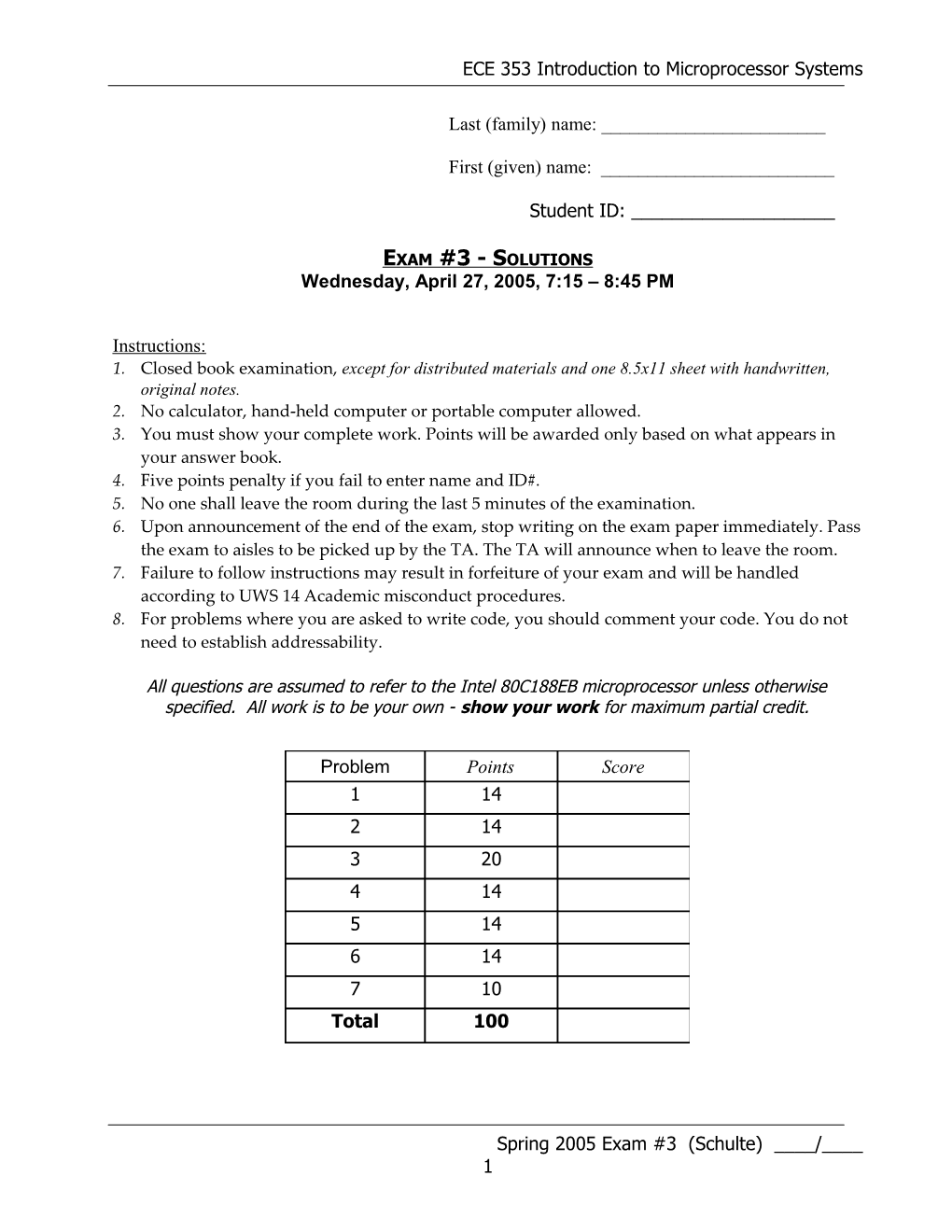

EXAM #3 - SOLUTIONS Wednesday, April 27, 2005, 7:15 – 8:45 PM

Instructions: 1. Closed book examination, except for distributed materials and one 8.5x11 sheet with handwritten, original notes. 2. No calculator, hand-held computer or portable computer allowed. 3. You must show your complete work. Points will be awarded only based on what appears in your answer book. 4. Five points penalty if you fail to enter name and ID#. 5. No one shall leave the room during the last 5 minutes of the examination. 6. Upon announcement of the end of the exam, stop writing on the exam paper immediately. Pass the exam to aisles to be picked up by the TA. The TA will announce when to leave the room. 7. Failure to follow instructions may result in forfeiture of your exam and will be handled according to UWS 14 Academic misconduct procedures. 8. For problems where you are asked to write code, you should comment your code. You do not need to establish addressability.

All questions are assumed to refer to the Intel 80C188EB microprocessor unless otherwise specified. All work is to be your own - show your work for maximum partial credit.

Problem Points Score 1 14 2 14 3 20 4 14 5 14 6 14 7 10 Total 100

Spring 2005 Exam #3 (Schulte) ____/____ 1 ECE 353 Introduction to Microprocessor Systems

Spring 2005 Exam #3 (Schulte) ____/____ 2 ECE 353 Introduction to Microprocessor Systems

1. (14 pts) Address Decoding: Given the decoding circuitry below, draw the memory map for the system. Label the starting and ending addresses of each region including unpopulated areas. If memory devices are not exhaustively decoded, show all images (with starting and ending addresses) in the memory map.

RAM 128KB

A0 Y0 CE A18 A1 Y1 74HC138 A19 A2 Y2 Y3 E1 Y4 E2 Y5 /S2 E3 Y6 Y7 ROM 64KB

CE

00000h RAM 1FFFFh 20000h RAM (image) 3FFFFh 40000h

Unpopulated

BFFFFh C0000h ROM CFFFFh D0000h ROM (image) DFFFFh E0000h ROM (image) EFFFFh F0000h ROM (image) FFFFFh

Note: Any of the above ROMs or RAMs could be designated as images.

What is the granularity of the decoder outputs? 256KB

Spring 2005 Exam #3 (Schulte) ____/____ 3 ECE 353 Introduction to Microprocessor Systems

2. (14 pts) Memory Systems: Select the proper number of memory devices (put an X through any unused ones) and show all required connections to an 80C188EB demultiplexed bus (including address and data lines) in order to create a 128K x 8 memory bank using the RAM devices shown. Then, design and draw exhaustive decoding circuitry for the required chip-select signal(s) so that the base address is 60000h. For decoding, use only NAND gates with any number of inverted/non-inverted inputs. (For simplicity, the SRAM’s /OE and /WE pins are not shown and are not required.)

What size is each RAM device shown below? (depth x width) 64Kx4 bits

A15 A15 D3 D7 A15 A15 D3 D7

D0 D4 D0 D4

A0 A0 A0 A0

CE CE

A15 A15 D3 D3 A15 A15 D3 D3

D0 D0 D0 D0

A0 A0 A0 A0

CE CE

A19 A19 A18 A18 A17 A17 A16 A16 /S2 /S2

Spring 2005 Exam #3 (Schulte) ____/____ 4 ECE 353 Introduction to Microprocessor Systems

3. (20 pts) Short Answers

(4 pts) Decoding: What advantage and disadvantage does exhaustive decoding have compared to partial decoding?

Advantage: With exhaustive decoding is no memory aliasing, in which multiple addresses mapping to the same location.

Disadvantage: The decode logic for exhaustive decoding is typically more complex than for partial decoding. If not done correctly, partial decoding can lead to bus contention.

(4 pts) I/O Decoding: What are two significant differences between using isolated I/O and memory-mapped I/O in the 80C188EB?

1. The address space for isolated I/O is 64KB, while for memory-mapped I/O it is 1MB. 2. Isolated I/O is accessed using IN and OUT instructions, while memory mapped I/O is accessed using memory addressing modes.

(4 pts) Peripheral Control Block: What is the purpose of the peripheral control block?

The peripheral control block allows various registers associated with the 80C188EB integrated peripherals to be read or written.

(4) 80C188EB I/O Unit: What are two limitations of the 80C188EB I/O Unit?

The 80C188EB I/O Unit only provides two I/O ports and the direction of most of the pins is fixed. Also, most of the pins for the 80C188EB I/O Unit are multiplexed with other pins.

(4) Memory Devices: What advantage and disadvantage does EPROM have compared to SRAM?

Advantage: An EPROM is non-volatile, so it does not lose its contents when power is turned off. Disadvantage: An EPROM can only be read while it is in the circuit. Writing to it requires taking it out of the circuit.

Spring 2005 Exam #3 (Schulte) ____/____ 5 ECE 353 Introduction to Microprocessor Systems

4. (14 pts) 80C188EB CSU: Write a code fragment below to program /GCS3 to use it as the chip-select for a 4KB ROM in memory space starting at addresses AA000h. Assume two wait states and that the READY line can be ignored. mov dx, GCS3ST mov ax, AA02h ;start address = AA000h, two wait states out dx, al mov dx, GCS3SP mov ax, AB0Ah ;stop address = AB000h, CSEN = 1, ISTOP = 0, MEM = 1, RDY = 0 out dx, al

Spring 2005 Exam #3 (Schulte) ____/____ 6 ____/10 ECE 353 Introduction to Microprocessor Systems

5. (14 pts) Conditional I/O: Assume that an output device is mapped to a single address (0064h) in isolated I/O space, with a status register (read-only), and a data register (write-only) at that address. The most significant bit in the status register is set when the device is ready to be written to and cleared otherwise. The other bits of the status register are undefined.

(Problem 10, From Exam2, Spring 2002, changed address, number of cycles, and test of most significant bit)

Write an efficient procedure that will poll the status register until the device indicates it is ready, then write the value in BL to the device and return with the carry flag (CF) cleared. If the device is not ready within 1,000 polling attempts, return with CF set. Your procedure does not have to preserve any registers.

; Name: WriteDevice ; Description: Writes byte to output device after polling status for ready ; Assumes: BL = data to write ; Returns: CF=1 if not ready, CF=0 otherwise ; Modifies: WriteDevice proc mov cx, 1000 ;load iteration count wait_loop: in al,64h ;read status port test al, 80h ;test MS bit jnz write_data ;if set, ready for write loop wait_loop ;if we get here, have timed out stc ;so set CF jmp write_exit ;and return write_data: mov al, bl ;device was ready, so out 64H, al ;write data in BL to the device clc ;and clear CF write_exit: ret WriteDevice endp

Spring 2005 Exam #3 (Schulte) ____/____ 7 ____/15 ECE 353 Introduction to Microprocessor Systems

6. (14 pts) I/O Port Decoding: Given the circuitry below, show the required connections to the 74HC138 (80C188EB system signals and connections to the port devices) to operate the latch and buffer so that they appear as output and input ports, respectively, at I/O address 4000h. Decoding does not have to be exhaustive, but there must be no images of the ports at address 8000h or above.

D7:0 IN7:0

BUFFER

/RD A0 Y0 A1 Y1 OE /WR 74HC138 A15 A2 Y2 Y3 /S2 E1 Y4 A13 E2 Y5 A14 E3 Y6 OUT7:0 Y7 LATCH

CLK OE

Other solutions exist. For example, the E2 pin could also be tied to ground.

Spring 2005 Exam #3 (Schulte) ____/____ 8 ECE 353 Introduction to Microprocessor Systems

7. (10 points) Memory subsystem – hardware debug

A 3-control line memory device has 11 address pins and 8 data pins. The device is connected to a microprocessor. The expected connections were that A10 -- A0 to be connected to the corresponding address pins of the memory and A11 was to be connected to the CS (active high) pin of the memory. But the technician connecting the device to the processor made a misconnection. He connected A10 to the CS pin and A11 to the pin where A10 was to be connected. All other connections are correct. Now answer the following questions.

b) (3 points) What is the address of the 0th byte (in hex) of the memory assuming that the connections were correctly made as expected? 800h

c) (3 points) What is the address of the 0th byte (in hex) of the memory when the incorrect connections are made by the technician? 400H

d) (4 points) The incorrect connection introduces a discontinuity in addressing space. The addresses of the memory will no longer be contiguous. Provide two addresses that will be contiguous (i followed by i+1) in the correct version but will be non-contiguous in the incorrect version. Give both the correct and the corresponding incorrect values below in hex.

address in the correct design corresponding address in the incorrect design

i = __BFFH______7FFH______

i+1 = __C00H______C00H______

Spring 2005 Exam #3 (Schulte) ____/____ 9