Xilinx ISE Schematic Entry Tutorial

1) Creating a New Project

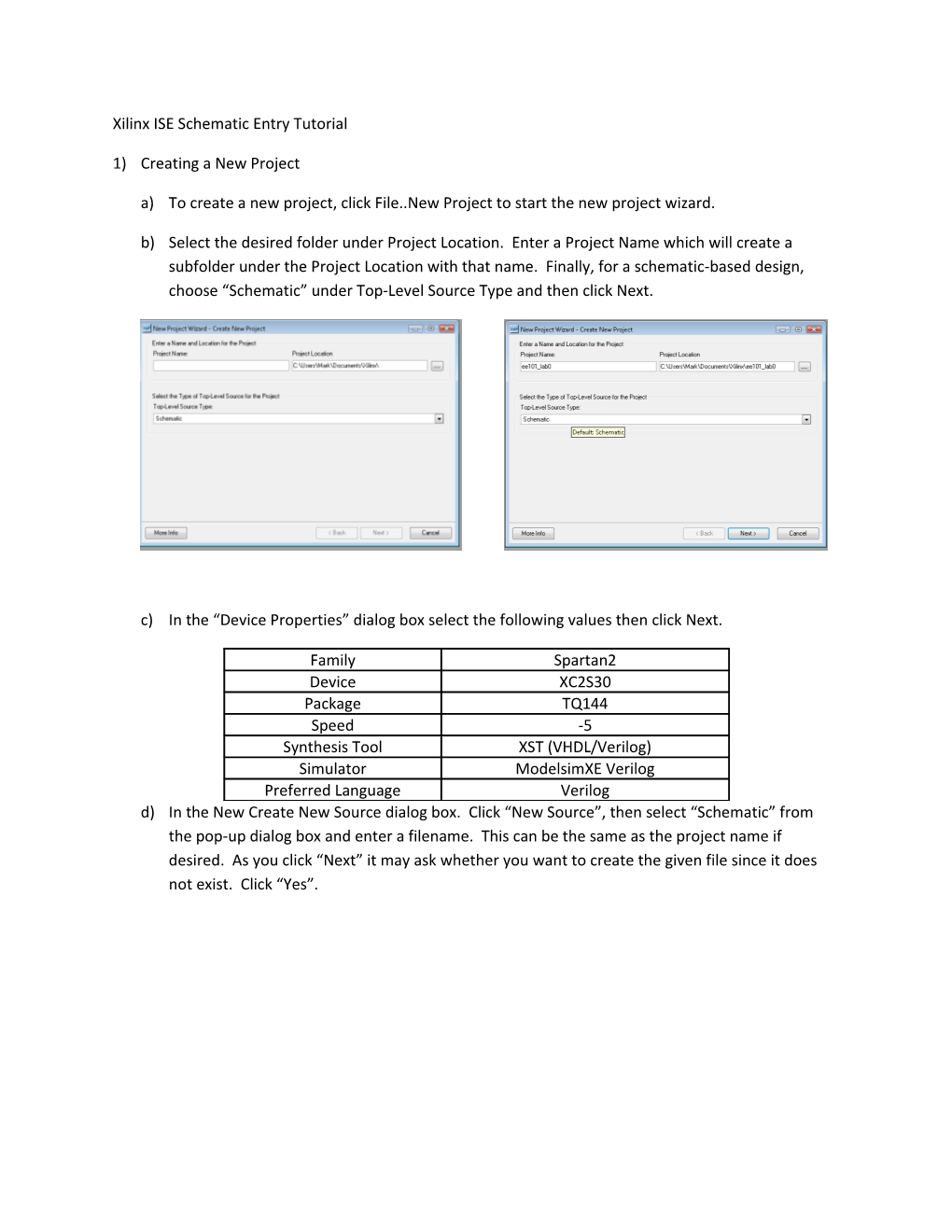

a) To create a new project, click File..New Project to start the new project wizard.

b) Select the desired folder under Project Location. Enter a Project Name which will create a subfolder under the Project Location with that name. Finally, for a schematic-based design, choose “Schematic” under Top-Level Source Type and then click Next.

c) In the “Device Properties” dialog box select the following values then click Next.

Family Spartan2 Device XC2S30 Package TQ144 Speed -5 Synthesis Tool XST (VHDL/Verilog) Simulator ModelsimXE Verilog Preferred Language Verilog d) In the New Create New Source dialog box. Click “New Source”, then select “Schematic” from the pop-up dialog box and enter a filename. This can be the same as the project name if desired. As you click “Next” it may ask whether you want to create the given file since it does not exist. Click “Yes”.

e) In the Add Existing Source, simply click Next. f) In the Project Summary Dialog Box, simply click Finish.

a) In the main window, a detailed project summary will appear. You may close this tabbed window or simply leave it alone. 2) Schematic Entry

a) To enter your design you will use the included schematic entry tool. Ensure that the “Sources for:” drop-down box is set to “Synthesis/Implementation”. Then double-click the .sch file that should appear under the part name (xc2s30-5tq144). A blank schematic page should appear in the main window.

b) Now select the “Symbols” tab from the “Sources” pane. You may want to increase the size of the “Sources” pane at this point to allow greater visibility of the component selection options. First scroll down in the “Category” selection box to the type of component to add. In this case, select “Logic” for basic gates. Then select the desired component in the “Symbols” selection box. Find the “and2” component, select it, and move the mouse cursor over the schematic window. Click anywhere on the schematic to add the AND gate. Continue clicking to add more AND gates. In this case, however, we only need two. You may add a 2-input OR gate (or2) and an inverter (inv) using this same method. c) In addition to adding components, you will need to connect them with wires, add signal names and input/output markers, etc. The toolbar provides the basic functions that you will need. Selection tool

Wire (bus) tool

Net name tool

Rename bus tool

Bus tap tool

Add I/O marker tool

d) Start by using the wiring tool (click the icon on the toolbar) to draw what will be the X bus as shown in Figure XX. Start by clicking on the schematic at the desired start point for the wire and then double-clicking at the end point.

e) Indicating that this will be a 3-bit bus (versus a single wire) is accomplished through the “Net Name” tool. Click the “Net Name” icon on the tool bar, then go to the “Processes” pane on the lower left. Ensure that the “Options” tab has been selected (vs. the “Processes” tab). In the “Name” textbox, enter the bus or wire name. In this case, enter “X(2:0)” which will indicate a 3- bit bus. Now position your pointer over the bus in the schematic window and you should see the label floating alongside your pointer. To complete the naming, click the bus at the point you want the label to appear (near the top to keep it out of the way when we add more wires.) The wire will appear thicker indicating a multiple wire bus and the label will be affixed. f) To connect individual bits of the bus to their respective gates, use the “Bus tap” tool. Click the icon on the toolbar. As you move the cursor over the schematic window it appears as a bus tap symbol. You must first indicate the bus to which you will connect. Do this by clicking the line end of the bus tap symbol anywhere along the X(2:0) bus. Then, position the line end of the bus tap symbol at the input of the inverter. Four tiny squares should appear indicating you are at a connection point. Now click and the bus tap wire will be drawn. g) More bus taps can now be added in succession by simply clicking at each connection point of the desired gates. Connect another bus tap to the bottom inputs of each AND gate (but leave the top input of the second AND gate free. (Notice in the “Processes” pane that you can select the bus tap’s orientation to any direction. If we were connecting bus tap’s to an output, we would change the orientation to the right-side.)

h) The input to the inverter will eventually be X(2). That input should also be connected to the top input of the second AND gate. We can connect an individual wire by selecting the “Wire” tool from the toolbar. First, click somewhere along the bus tap wire going into the inverter to create a junction point and then move the cursor to the top input of the AND gate. A line will be shown as you move the cursor. Click on the connection point of the top AND gate and the wire will be added.

i) Continue wiring the gates together (the inverter to the AND, the AND’s to the OR, and a dangling net from the output of the OR gate to some free space to the right) by using the wire tool and clicking on the start point and then the end point. j) Now name the individual nets to indicate which input is which. Click the “Net Name” tool on the toolbar. Go to the “Processes” pane, “Options” tab and scroll down to the “Name” textbox and the options below. You can enter one wire’s name each time, but the tool provides for an easy way to name the individual wires of a bus. In the “Name” textbox enter “X(2)” then click the “Decrease the name” option in the option buttons below. This will auto-decrement the number [to X(1) and X(0)] each time you add a label in top-down order. Now move the cursor over the top bus tap (the one connected to the inverter) and click on the wire somewhere. You should see the X(2) label affixed to the wire. The shadow label associated with the cursor should now read X(1) [and you should also see X(1) in the “Name” textbox to the left]. Now click on the next bus tap connected to the bottom input of the top AND gate. X(1) should be affixed to that wire. Finally, click on the bottom input to the bottom AND gate which should be X(0). If you experience problems, you can always just enter the individual names in the “Name” textbox and then affix that label to the wire. k) We will also give names to the intermediate signals connecting the AND gates to the OR gates. In the “Name” textbox, enter “T1” and also select “Keep the name” from the option buttons below the textbox since we don’t need to auto-increment/decrement these individual wire names. Now move your cursor over the wire connecting the top AND gate to the OR gate and click to attach the label. Name the bottom AND gate’s output “T2”.

l) The last step is to add input and output markers. For our designs, overall inputs and outputs must be marked and not just named. Click the “I/O marker” tool on the toolbar. In the “Processes” pane, Options tab you may select specific options for how the I/O marker should be created, but the tool is smart enough to figure out most of the necessary information automatically (such as whether this is an input or output, etc.). Position the cursor over the endpoint of the dangling wire coming out of the OR gate until the four tiny squares appear indicating you may make a connection. (Sometimes the tool is a bit buggy and doesn’t show the squares, in which case just try to be as near the endpoint as possible.) Click and the I/O marker will be added. Because we did not give the wire a label/name it will add a default name. Let us change it by double-clicking the I/O marker and entering the name “PRIME” in the “Name” option. Now, move the cursor over the top endpoint of the X(2:0) bus and click again. The I/O marker will be added for X(2:0). Because we had already named the bus/wire, the I/O marker uses that same name. m) Your schematic is now complete and should look similar to what is shown below.

n) With your schematic complete, you can now synthesize your design which will check for errors (if you connect two outputs together, or labeled the same signal with multiple names, etc.) report area and timing results, etc. To do this, be sure “Synthesis/Implementation” is still selected from the “Sources” pane, “Sources” tab, “Sources for:” drop-down box. Then in the “Processes” pane, “Processes” tab, double- click the “Synthesis – XST” process. The process will take a few seconds with report information scrolling by in the bottom pane. If the process is successful a green check will appear next to the Synthesis process. If errors occur you can view them by expanding the “Synthesis” process and double-clicking the “View Synthesis Report” subprocess.

3) Testbench Design & Simulation a) Now that we have entered our design we can verify its correct operation using a testbench and simulation software (Modelsim XE). To create the testbench choose “Behavioral Simulation” from the “Sources for:” drop-down in the “Sources” pane. b) Under the “Processes” pane and tab, double-click “Create New Source”. In the resulting dialog box select “Testbench Waveform”. Enter a file name (one method is to simply add the “_tb” suffix to the schematic name. Ensure the “Add to Project” box is checked and then click Next.

c) The next dialog box allows for setting up certain timing constraints. You can set the length of the simulation (default 1000 ns). A good rule of thumb is 50 ns per input combination. Thus, since we only have 3 inputs 1000 ns is plenty of time. Click “Finish”.

d) The testbench waveform editor appears allowing you to set the input combinations to test. Click the X(2:0) waveform around the 100 ns point. e) The “Set Value” dialog box appears and allows you to enter the input value (in the current radix). (Note: The radix can be changed by right clicking on anywhere on the waveform and selecting the desired system/radix. Also, the notation in the waveform of 3’h0 indicates that the input is 3-bits, the display radix is hex, and the value of the 3-bits in that radix is 0.) However, in this case let us exhaustively test the circuit with all 23=8 combinations quickly and easily using the pattern wizard. Click the “Pattern Wizard” button. Set the “Pattern Type” to “Count Up” and the “Initial” and “Terminal Value” to 0 and 7 respectively. (Hexadecimal is probably the current radix). Click OK and the waveform should be similar to Figure XX. f) Now run the simulation and view the PRIME output by using Modelsim. Select the “Processes” tab in the “Processes” pane. Expand the Modelsim Simulator icon and double-click the “Simulate Behavioral Model” process. This will launch Modelsim and run the input waveforms through the circuit showing the corresponding outputs. The Modelsim waveform viewer will appear in the right of the window. Zoom out using

the “Zoom Full” tool on the toolbar.

g) The eight input combinations should now appear with the PRIME output of your circuit. Ensure that it is high (logic ‘1’) for combinations 2 (010), 3(011), 5 (101), and 7 (111).

h) You may change the display radix by right- clicking the X label in the “Wave” window, selecting Radix… Hexadecimal (or any other desired system). i) The waveform should now look similar to Figure XX.

j) At this point, you would look for any mismatch between what you expect as output versus what is actually shown as the output in the waveform. If there are errors you will need to debug your design. Debugging can be facilitated by viewing internal signals (non I/O). Internal signals can be viewed provided they were named. In our design the outputs of the two AND gates were labeled T1 and T2. may change the display radix by right-clicking the X label in the “Wave” window, selecting Radix…Hexadecimal (or any other desired system). To add T1 and T2 to the waveform, click on “UUT” in the “Workspace” pane. By selecting “UUT” the signals T1 and T2 are shown in the “Objects” pane. Select T1 and T2 and drag them to the “Wave” window. Unfortunately, the simulator needs to rerun the simulation to find T1 and T2. In the bottom pane (“Transcript”) at the “VSIM” command prompt enter the command “restart –f” and hit enter. This will reset the simulation to time 0 and clear all the waveform data. Follow that by typing “run 1000 ns” at the VSIM prompt and hit enter. This will run the simulation for 1000 ns. Now T1 and T2 signals should appear with their corresponding output waveform. You may need to click Zoom Full again. In general, the process is to select the UUT instance in the “Workspace” pane, then find the desired signals in the “Object” pane and drag them to “Wave” window. Restart and rerun the simulation.