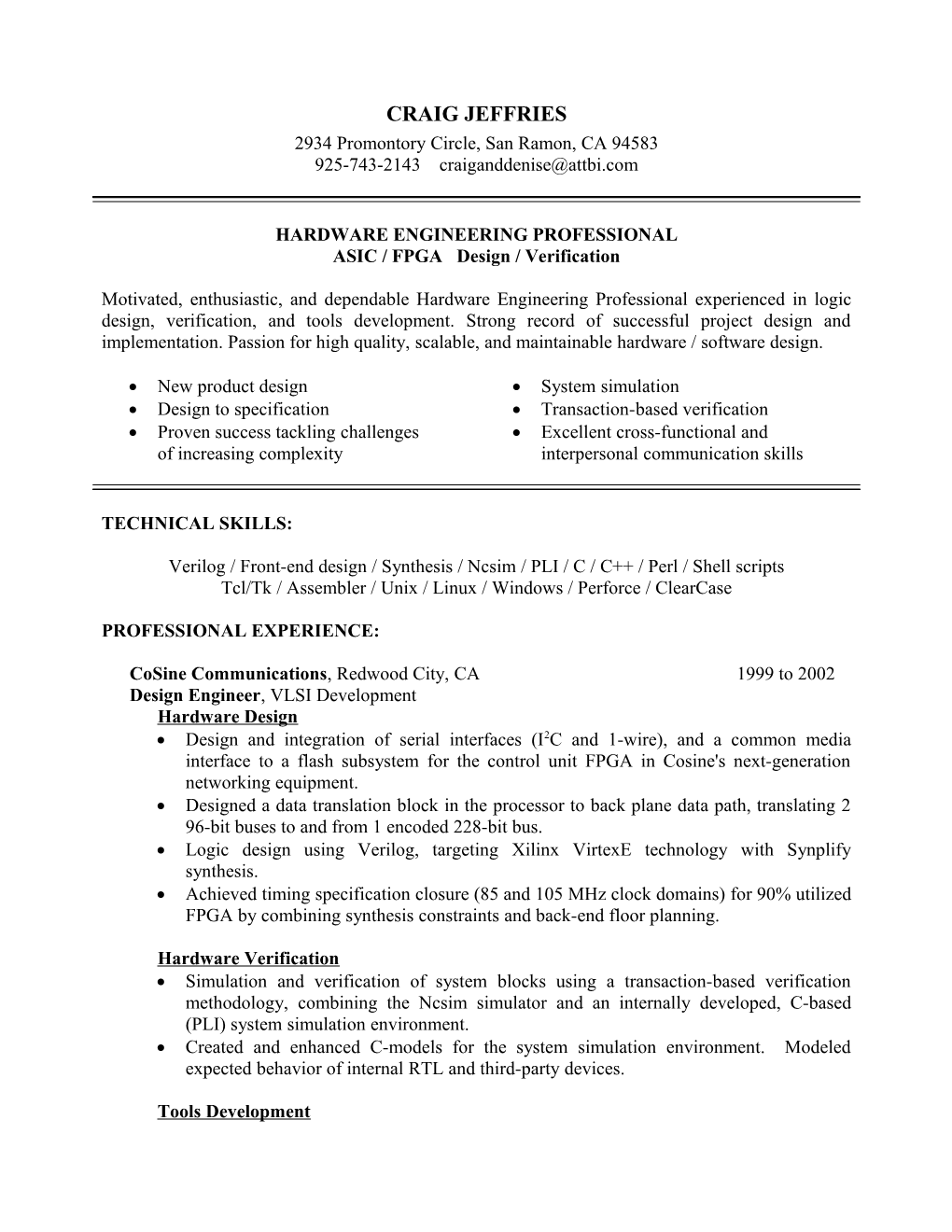

CRAIG JEFFRIES 2934 Promontory Circle, San Ramon, CA 94583 925-743-2143 [email protected]

HARDWARE ENGINEERING PROFESSIONAL ASIC / FPGA Design / Verification

Motivated, enthusiastic, and dependable Hardware Engineering Professional experienced in logic design, verification, and tools development. Strong record of successful project design and implementation. Passion for high quality, scalable, and maintainable hardware / software design.

New product design System simulation Design to specification Transaction-based verification Proven success tackling challenges Excellent cross-functional and of increasing complexity interpersonal communication skills

TECHNICAL SKILLS:

Verilog / Front-end design / Synthesis / Ncsim / PLI / C / C++ / Perl / Shell scripts Tcl/Tk / Assembler / Unix / Linux / Windows / Perforce / ClearCase

PROFESSIONAL EXPERIENCE:

CoSine Communications, Redwood City, CA 1999 to 2002 Design Engineer, VLSI Development Hardware Design Design and integration of serial interfaces (I2C and 1-wire), and a common media interface to a flash subsystem for the control unit FPGA in Cosine's next-generation networking equipment. Designed a data translation block in the processor to back plane data path, translating 2 96-bit buses to and from 1 encoded 228-bit bus. Logic design using Verilog, targeting Xilinx VirtexE technology with Synplify synthesis. Achieved timing specification closure (85 and 105 MHz clock domains) for 90% utilized FPGA by combining synthesis constraints and back-end floor planning.

Hardware Verification Simulation and verification of system blocks using a transaction-based verification methodology, combining the Ncsim simulator and an internally developed, C-based (PLI) system simulation environment. Created and enhanced C-models for the system simulation environment. Modeled expected behavior of internal RTL and third-party devices.

Tools Development CRAIG JEFFRIES – Page Two

Re-engineered and enhanced multi-platform (Win98 / WinNT / Win2000) flash hardware programming tool, supporting over 50 people across 3 functions, including engineering, manufacturing, and global customer support. Reduced hardware build process time from 2 hours to 15 minutes, and increased build accuracy from 70% to 100%, as Hardware Change Manager. Gains achieved by developing Perl programs to automate the build process.

Harris Communications Products Division, Novato, CA 1997 to 1999 Test Engineer, Test Engineering Test Development & Sustaining Designed and enhanced ATE tests for PBX board assemblies. Wrote tests in C, and included use of JTAG Boundary Scan Testing. Achieved 20% cost-reduction on power supply assembly by switching core power supply vendors, and implementing necessary circuit modifications.

ADTranz, Mannheim, Germany 1996 Prakticant, Software Development Firmware / Software Development Developed packet monitoring system for ADTranz's implementation of the Train Communication Network (TCN). Wrote firmware in C for 80C186 embedded micro system to monitor the bus, and created a GUI using Tcl/Tk to display bus activity to prospective customers and company executives.

EDUCATION:

University of the Pacific, Stockton, CA 1998 B.S., Electrical Engineering (Magna Cum Laude) Dean’s Honor Roll 7 of 8 Semesters National Merit and UOP Regents Scholarship Recipient