Lab #3: VGA Display Driver

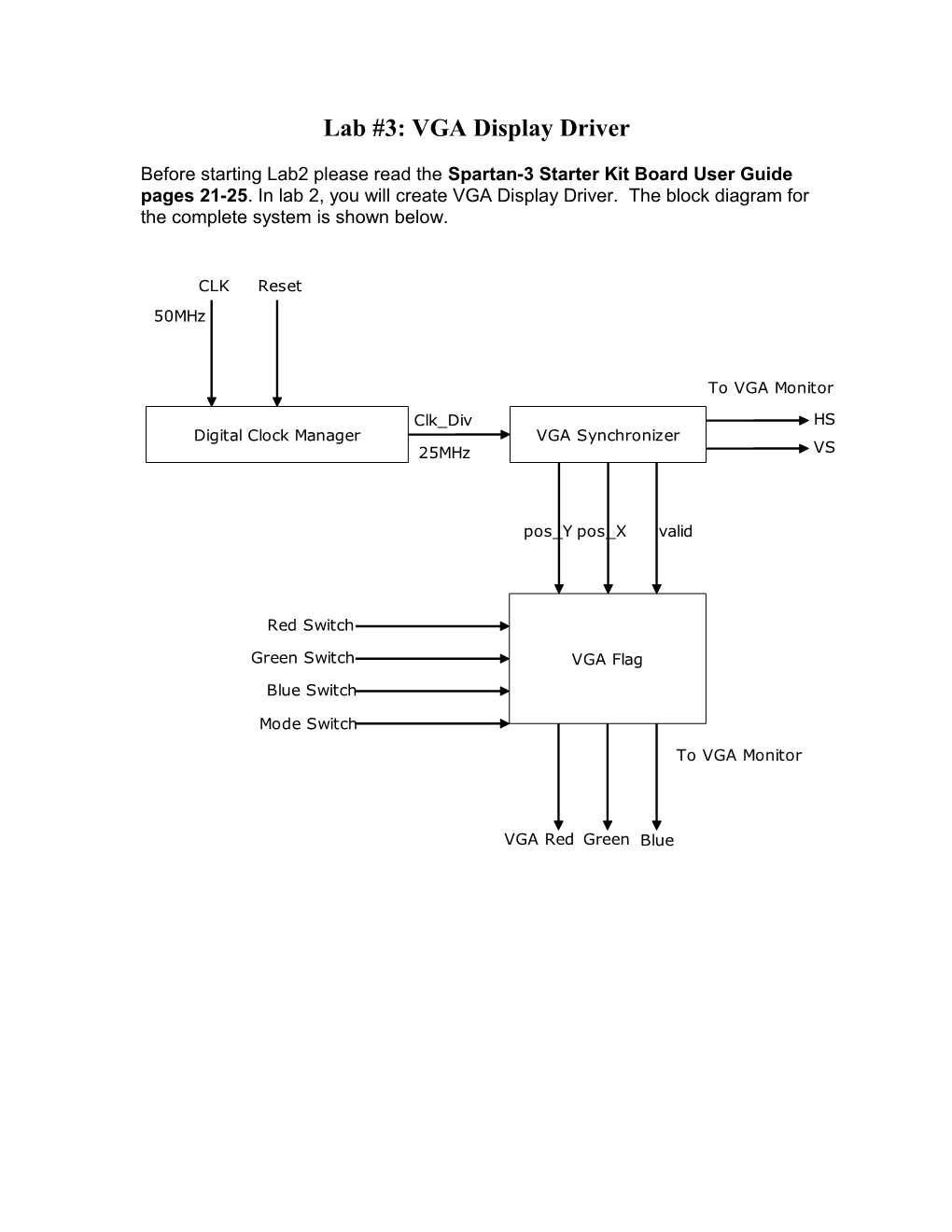

Before starting Lab2 please read the Spartan-3 Starter Kit Board User Guide pages 21-25. In lab 2, you will create VGA Display Driver. The block diagram for the complete system is shown below.

CLK Reset 50MHz

To VGA Monitor

Clk_Div HS Digital Clock Manager VGA Synchronizer 25MHz VS

pos_Y pos_X valid

Red Switch

Green Switch VGA Flag Blue Switch

Mode Switch

To VGA Monitor

VGA Red Green Blue Driving a VGA monitor

A VGA monitor requires 5 signals to display a picture:

R, G and B (red, green and blue signals). HS and VS (horizontal and vertical synchronization).

The R, G and B are analog signals, while HS and VS are digital signals.

Timing of a line

Each line of video begins with an active video region, in which RGB values are output for each pixel in the line. The active region is followed by a blanking region, in which black pixels are transmitted. In the middle of the blanking interval, a horizontal sync pulse is transmitted. The blanking interval before the sync pulse is known as the "front porch", and the blanking interval after the sync pulse is known as the "back porch". Timing of a Frame

Frames are constructed from lines in much the same way as lines are constructed from pixels. The beginning of a frame contains all of the lines that will actually be displayed on the screen, followed by a number of black lines that make up the front porch. Next is a vertical sync pulse that lasts for several lines, and then more black lines to make up a back porch. VGA Synchronizer Module

The VGA synchronizer module will be used to generate the Horizontal Synchronization (HS) and Vertical Synchronization (VS) signals to the monitor.

The inputs to the VGA Synchronizer Module are: clk_25 25 MHz clock. System clock divided by 2. reset Reset from button (BTN3) on the FPGA board

The outputs of the VGA Synchronizer Module are: pos_X [10:0] 11-bit counter current X-pixel position pos_Y [10:0] 11-bit counter current Y-pixel position valid Signal to VGA flag indicating pixel information can be displayed on the monitor. HS Horizontal Sync signal FPGA Pin: R9 VS Vertical Sync signal FPGA Pin: T10

Parameters for the VGA Synchronizer are: Horizontal Parameters Vertical Parameters active_video_H=640; active_video_V=480; front_porch_H=16; VS_pulse_width=2;

HS_pulse_width=96; front_porch_V=10; back_porch_H=48; back_porch_V=29; length_of_line_H =(active_video_H+front_porch_H+HS_pulse_width+back_porch_H); length_of_line_V =(active_video_V+front_porch_V+VS_pulse_width+back_porch_V);

The pos_X counter should count from 0 to length of line_H-1 and then reset back to 0.

The pos_Y counter should increment by 1 whenever the pos_X counter reaches length_of_line-1. Additionally, the pos_Y counter should also reset whenever it reaches length_of_line_V-1.

You will need to create the logic for the VS_pulse and the valid signal based on the pos_X and pos_Y counters. The logic for the HS pulse is shown below.

assign HS_pulse=((pos_X >=((active_video_H + front_porch_H)-1)) && (pos_X <=active_video_H + front_porch_H + HS_pulse_width-2)) ? 1'b1 : 1'b0;

//register output always @ (posedge clk) HS <= HS_pulse; VGA Flag Module

The inputs to the VGA Flag Module are: clk_25 25 MHz clock. System clock divided by 2. reset Reset from button (BTN3) on the FPGA board pos_X [10:0] 11-bit counter current X-pixel position pos_Y [10:0] 11-bit counter current Y-pixel position valid Signal to VGA flag indicating pixel information can be displayed on the monitor. mode Signal to indicate whether to display the test pattern or the input from the Red, Green, and Blue switches. SW0/FPGA pin F12 Red_switch SW7/FPGA pin K13 Green_switch SW6/FPGA pin K14 Blue_switch SW5/FPGA pin J13

The outputs of the VGA Flag Module are: VGA_red FPGA pin: R12 VGA_green FPGA pin: T12 VGA_blue FPGA pin: R11

If the mode signal is logic ’0’ display the test pattern shown below:

If the mode signal is logic ‘1’ display the color as determined by the three color input switches on the screen. The truth table for the output colors is shown below. Using a Digital Clock Manager DCM to divide the 50Mhz clock.

1. In the processes window double click the Create New Source

2. Select IP (Coregen & Architecture Wizard) and name the file clk_divider

3. Select the Single DCM. 4. When you select finish in the next window the DCM configuration window will appear

5. Set up your DCM with the same values and outputs, click next 2 times and then finish 6. You should now see an icon for your DCM in your ISE project Sources tab.

7. You should instantiate the DCM module in your top module and connect the CLKDV_OUT to your VGA synchronizer and VGA flag modules Example TOP Module module VGA_top ( input clk, input reset, input mode, input red_switch, input green_switch, input blue_switch, output red, output green, output blue, output HS, output VS );

wire CLKDV_OUT; wire valid; wire [10:0] pos_X; wire [10:0] pos_Y;

clk_divider CD ( .CLKIN_IN(clk), .RST_IN(reset), .CLKDV_OUT(CLKDV_OUT), .CLKIN_IBUFG_OUT(CLKIN_IBUFG_OUT), .CLK0_OUT(CLK0_OUT), .LOCKED_OUT(LOCKED_OUT) ); vga_synchronizer VSYN( .clk(CLKDV_OUT), .reset(reset), .valid(valid), .HS(HS), .VS(VS), .pos_X(pos_X), .pos_Y(pos_Y) ); VGA_flag VF( .clk(CLKDV_OUT), .reset(reset), .X(pos_X), .Y(pos_Y), .valid(valid), .mode(mode), .red_switch(red_switch), .green_switch(green_switch), .blue_switch(blue_switch), .vga_red(red), .vga_blue(blue), .vga_green(green) );

endmodule

UCF File

NET "blue" LOC = "R11" ; NET "blue_switch" LOC = "J13" ; NET "clk" LOC = "T9" ; NET "green" LOC = "T12" ; NET "green_switch" LOC = "K14" ; NET "HS" LOC = "R9" ; NET "mode" LOC = "F12" ; NET "red" LOC = "R12" ; NET "red_switch" LOC = "K13" ; NET "reset" LOC = "L14" ; NET "VS" LOC = "T10" ;