www.bookspar.com | Website for students | VTU NOTES 8086 Addressing Modes for accessing data

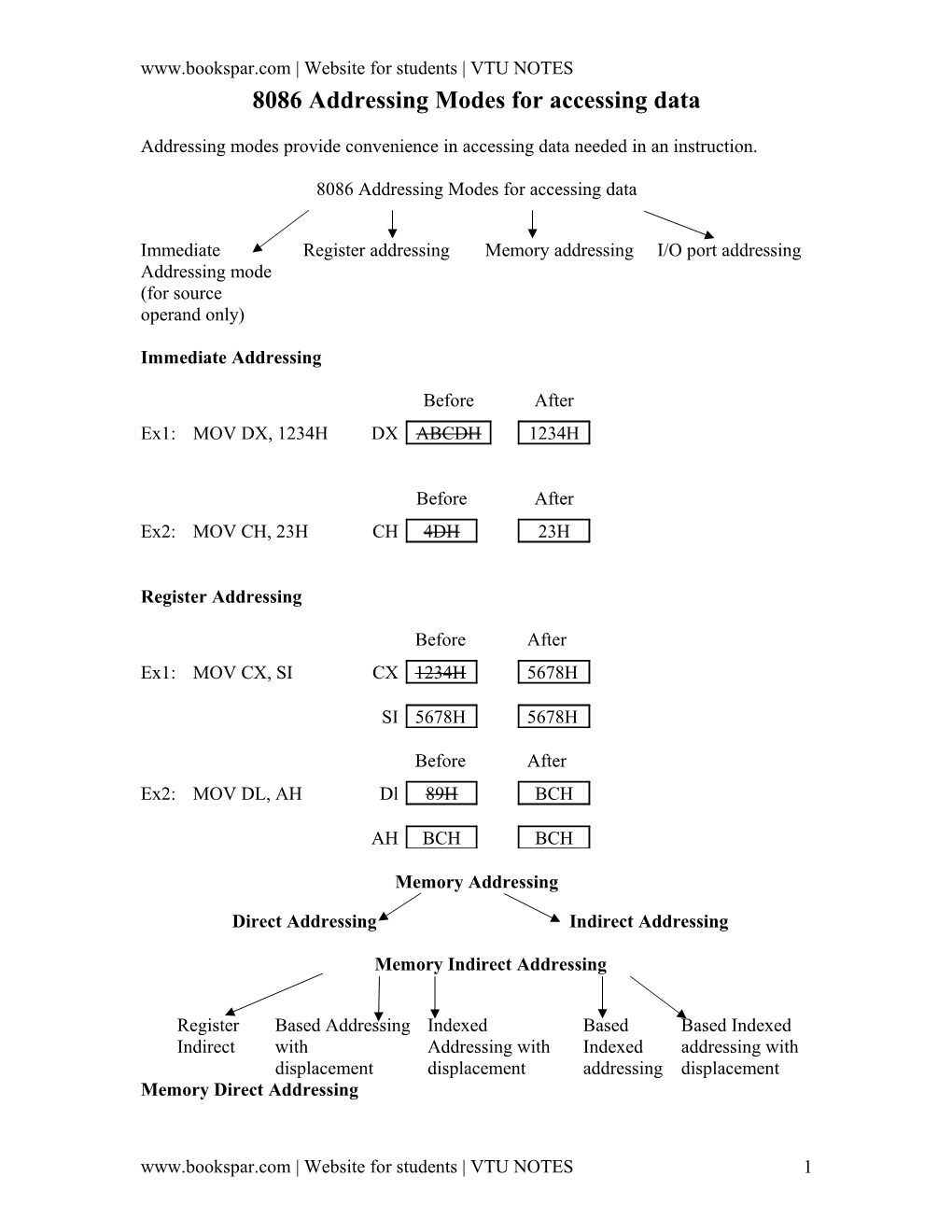

Addressing modes provide convenience in accessing data needed in an instruction.

8086 Addressing Modes for accessing data

Immediate Register addressing Memory addressing I/O port addressing Addressing mode (for source operand only)

Immediate Addressing

Before After Ex1: MOV DX, 1234H DX ABCDH 1234H

Before After Ex2: MOV CH, 23H CH 4DH 23H

Register Addressing

Before After Ex1: MOV CX, SI CX 1234H 5678H

SI 5678H 5678H

Before After Ex2: MOV DL, AH Dl 89H BCH

AH BCH BCH

Memory Addressing

Direct Addressing Indirect Addressing

Memory Indirect Addressing

Register Based Addressing Indexed Based Based Indexed Indirect with Addressing with Indexed addressing with displacement displacement addressing displacement Memory Direct Addressing

www.bookspar.com | Website for students | VTU NOTES 1 www.bookspar.com | Website for students | VTU NOTES

Before After Ex1: MOV BX, DS:5634H BX ABCDH 8645H

DS:5634H 45H LS byte DS:5635H 86H MS byte

Before After Ex2: MOV CL, DS:5634H CL F2H 45H

DS:5634H 45H DS:5635H 86H

Ex3: MOV BH, LOC Before After Program BH C5H 78H .DATA LOC DB 78H

Register Indirect Addressing

Before After Ex1: MOV CL, [SI] CL 20H 78H

SI 3456H

DS:3456H 78H

Before After Ex2: MOV DX, [BX] DX F232H 3567H

BX A2B2H

DS:A2B2H 67H LS byte DS:A2B3H 35H MS byte

Before After Ex3: MOV AH, [DI] AH 30H 86H

DI 3400H

DS:3400H 86H

www.bookspar.com | Website for students | VTU NOTES 2 www.bookspar.com | Website for students | VTU NOTES Only SI, DI and BX can be used inside [ ] from memory addressing point of view. From user point of view [BP] is also possible. This scheme provides 3 ways of addressing an operand in memory.

Based Addressing with displacement

Before After Ex1: MOV DH, 2345H[BX] DH 45H 67H

2345H is 16-bit displacement BX 4000H

4000 + 2345 = 6345H DS:6345H 67H

Before After Ex2: MOV AX, 45H[BP] AX 1000H CDABH

45H is 8-bit displacement BP 3000H

3000 + 45 = 3045H SS:3045H ABH LS byte It is SS when BP is used SS:3346H CDH MS byte

Base register can only be BX or BP. This scheme provides 4 ways of addressing an operand in memory.

Indexed Addressing with displacement

Before After Ex1: MOV CL, 2345H[SI] CL 60H 85H

2345H is 16-bit displacement SI 6000H

6000 + 2345 = 8345H DS:8345H 85H

Before After Ex2: MOV DX, 37H[DI] DX 7000H B2A2H

37H is 8-bit displacement DI 5000H

5000H+ 37H = 5037H DS:5037H A2H LS byte DS:5038H B2H MS byte

Index register can only be SI or DI. This scheme provides 4 ways of addressing an operand in memory. Based Indexed Addressing

www.bookspar.com | Website for students | VTU NOTES 3 www.bookspar.com | Website for students | VTU NOTES Before After Ex1: MOV CL, [SI][BX] CL 40H 67H

SI 2000H

BX 0300H

2000H + 0300H = 2300H DS:2300H 67H

Before After Ex2: MOV CX, [BP][DI] CX 6000H 6385H

BP 3000H

DI 0020H

2000H + 0300H = 2300H SS:3020H 85H LS byte It is SS when BP is used SS:3021H 63H MS byte

This scheme provides 4 ways of addressing an operand in memory. One register must be a Base register and the other must be an Index register. For ex. MOV CX, [BX][BP] is an invalid instruction.

Based Indexed Addressing with Displacement

Before After Ex1: MOV DL, 37H[BX+DI] DL 40H 12H 37H is 8-bit displacement BX 2000H DI 0050H 2000H + 0050H + 37H = 2300H DS:2087H 12H

Before After Ex2: MOV BX, 1234H[SI+BP] BX 3000H 3665H SI 4000H BP 0020H

4000H + 0020H +1234 = 5254H SS:5254H 65H LS byte It is SS when BP is used SS:5255H 36H MS byte This scheme provides 8 ways of addressing an operand in memory.

www.bookspar.com | Website for students | VTU NOTES 4 www.bookspar.com | Website for students | VTU NOTES Memory modes as derivatives of Based Indexed Addressing with Displacement

Instruction Base Index Displace Addressing mode Register Register ment MOV BX, DS:5634H No No Yes Direct Addressing MOV CL, [SI] No Yes No Register Indirect MOV DX, [BX] Yes No No MOV DH, 2345H[BX} Yes No Yes Based Addressing with Displacement MOV DX, 35H[DI] No Yes Yes Indexed Addressing with displacement MOV CL, 37H[SI+BX] Yes Yes No Based Indexed Addressing MOV DL, 37H[BX+DI] Yes Yes Yes Based Indexed Addressing with displacement

I/O port Addressing

I/O port Addressing

Fixed port addressing Variable port addressing Or Direct Port addressing Or Indirect port addressing

Fixed Port Addressing

Before After Ex. 1: IN AL, 83H AL 34H 78H Input port no. 83H 78H

Before After Ex. 2: IN AX, 83H AX 5634H F278H Input port no. 83H 78H Input port no. 84H F2H

Before After Ex. 3: OUT 83H, AL AL 50H Output port no. 83H 65H 50H

Before After Ex. 4: OUT 83H, AX AX 6050H Output port no. 83H 65H 50H Output port no. 84H 40H 60H IN and OUT instructions are allowed to use only AL or AX registers. Port address in the range 00 to FFH is provided in the instruction directly.

www.bookspar.com | Website for students | VTU NOTES 5 www.bookspar.com | Website for students | VTU NOTES Variable Port Addressing

I/O port address is provided in DX register. Port address ranges from 0000 to FFFFH. Data transfer with AL or AX only.

Before After Ex. 1: IN AL, DX AL 30H 60H

DX 1234H

Input port no. 1234H 60H

Before After Ex. 2: IN AX, DX AX 3040H 7060H

DX 4000H

Input port no. 4000H 60H Input port no. 4001H 70H

Before After Ex. 3: OUT DX, AL AL 65H

DX 5000H

Output port no. 5000H 80H 65H

Before After Ex. 4: OUT DX, AX AX 4567H

DX 5000H

Output port no. 5000H 25H 67H Output port no. 5001H 36H 45H

8086 Instruction Template

Need for Instruction Template 8085 has 246 opcodes. The opcodes can be printed on an A4 size paper. 8086 has about 13000 opcodes. A book of about 60 pages is needed for printing the opcodes.

Concept of Template In 8085, MOV r1, r2 (ex. MOV A, B) has the following template.

0 1 3-bit r1 code 3-bit r2 code

www.bookspar.com | Website for students | VTU NOTES 6 www.bookspar.com | Website for students | VTU NOTES

3-bit Register code Register 000 B 001 C 010 D 011 E 100 H 101 L 110 M 111 A

Ex. 1: Code for MOV A, B is 01 11 1 000 = 78H 7 8

Ex.2: Code for MOV M, D is 01 11 0 010 = 72H 7 2

Using the template for MOV r1, r2 we can generate opcodes of 26 = 64 opcodes.

8086 Template for data transfer between REG and R/M

1 0 0 0 1 0 D W MOD REG R/M 2 bits 3 bits 3 bits

REG = A register of 8086 (8-bit or 16-bits) (except Segment registers, IP, and Flags registers) Thus REG = AL/ BL/ CL/ DL/ AH/ BH/ CH/ DH/ AX/ BX/ CX/ DX/ SI/ DI/ BP/ SP

R/ M = Register (as defined above) or Memory contents (8-bits or 16-bits)

W = 1 means Word operation W = 0 means Byte operation

D = 1 means REG is Destination register D = 0 means REG is source register

MOD = 00 means R/M specifies Memory with no displacement MOD = 01 means R/M specifies Memory with 8-bit displacement MOD = 10 means R/M specifies Memory with 16-bit displacement MOD = 11 means R/M specifies a Register

3-bit Register name Register When W = 1 When W = 0 code

www.bookspar.com | Website for students | VTU NOTES 7 www.bookspar.com | Website for students | VTU NOTES 000 AX AL 001 CX CL 010 DX DL 011 BX BL 100 SP AH 101 BP CH 110 SI DH 111 DI BH

Aid to remember: ALl Children Drink Bournvita (AL, CL, DL, BL) SPecial Beverages SIamese DrInk (SP, BP, SI, DI)

Case of MOD = 11

Example: Code for MOV AX, BX treated as ‘Move from BX to destination register AX’

D W MOD REG R/M 1 0 0 0 1 0 1 1 11 00 0 011 = 8B C3H Word AX is BX operation destination 8 B C 3

Example: Alternative code for MOV AX, BX treating it as ‘Move from source register BX to register AX’

D W MOD REG R/M 1 0 0 0 1 0 0 1 11 01 1 000 = 89 D8H Word BX is AX operation source 8 9 D 8

There are 2 possible opcodes for MOV AX, BX as we can choose either AX or BX as REG.

Example: Code for MOV AL, BH treated as ‘Move from BL to destination register AL’

D W MOD REG R/M 1 0 0 0 1 0 1 0 11 00 0 111 = 8A C7H Byte AL is BH operation destination 8 A C 7

Example: Alternative code for MOV AL, BH treating it as ‘Move from source register BH to register AL’

D W MOD REG R/M

www.bookspar.com | Website for students | VTU NOTES 8 www.bookspar.com | Website for students | VTU NOTES 1 0 0 0 1 0 0 0 11 11 1 000 = 88 F8H Byte BH is AL operation source 8 8 F 8

There are 2 possible opcodes for MOV AL, BH as we can choose either AL or BH as REG.

Case of MOD = 00, 01 or 10

R/M MOD = 00 MOD = 01 MOD = 10 No 8-bit signed 16-bit signed Displacement displacement d8 displacement d16 000 [SI+BX] [SI+BX+d8] [SI+BX+d16] 001 [DI+BX] [DI+BX+d8] [DI+BX+d16] 010 [SI+BP] [SI+BP+d8] [SI+BP+d16] 011 [DI+BP] [DI+BP+d8] [DI+BP+d16] 100 [SI] [SI+d8] [SI+d16] 101 [DI] [DI+d8] [DI+d16] 110 [BP] Direct [BP+d8] [BP+d16] Addressing 111 [BX] [BX+d8] [BX+d16]

The table shows 24 memory addressing modes i.e. 24 different ways of accessing data stored in memory. Aid to remember: SubInspector DIxit is a BoXer ( [SI+BX] and [DI]+[BX] )

SubInspector DIxit knows to control BP ( [SI+BP] and [DI]+[BP] )

He says’ SImple DIet DIRECTs a BoXer' ( [SI], [DI], Direct addressing, [BX] )

Ex: Code for MOV CL, [SI]

D W MOD REG R/M 1 0 0 0 1 0 1 0 00 00 1 100 = 8A 0CH Byte No CL is [SI] operation Disp. destination 8 A 0 C

Note that there is a unique opcode for MOV CL, [SI] as CL only can be REG.

Ex: Code for MOV 46H[BP], DX

D W MO REG R/M d8

www.bookspar.com | Website for students | VTU NOTES 9 www.bookspar.com | Website for students | VTU NOTES D 1 0 0 0 1 0 0 1 01 01 0 110 46H = 89 56 46H Word 8-bit DX is [BP+d8] operation Disp. source 8 9 5 6

Note that there is a unique opcode for MOV 46H[BP], DX as DX only can be REG.

Ex: Code for MOV 0F246H[BP], DX

D W MOD REG R/M d16 1 0 0 0 1 0 0 1 10 01 0 110 F2 46H = 89 96 F2 46H Word 16-bit DX is [BP+d16] Stored as 89 96 operation Disp. source 46 F2H 8 9 9 6 in Little Endian

Note that there is a unique opcode for MOV 0F246H[BP], DX as DX only can be REG.

Ex: Code for MOV [BP], DX

D W MO REG R/M d8 D 1 0 0 0 1 0 0 1 01 01 0 110 00H = 89 56 00H Word 8-bit DX is [BP+d8] operation Disp. source 8 9 5 6

Note that MOV [BP], DX is treated as MOV 00H[BP], DX before coding.

Ex: Code for MOV BX, DS:1234H

D W MO REG R/M Direct D addr 1 0 0 0 1 0 1 1 00 01 1 110 12 = 8B 1E 12 34H 34H Word No BX is Direct Stored as 8B 1E operation Disp. Dest. addr. 34 12H 8 B 1 E In Little Endian

Note that when MOD = 00 and R/M = 110, it represents Direct Addressing.

www.bookspar.com | Website for students | VTU NOTES 10 www.bookspar.com | Website for students | VTU NOTES Prerequisite information 8086 is a 16-bit processor It has 20 address pins (16 of them multiplexed with data pins) It can address a maximum of 220 = 1 Million locations. Address ranges from 00000H to FFFFFH. Memory is byte addressable. Every byte has a separate address.

00000H 12H 34 12H is the contents of 00001H 34H Word 00000H 56 34H is the contents of 00002H 56H 78 56H is the contents of Word 00001H 00003H 78H Word 00002H 91 78H is the contents of 00004H 91H 91H is the contents of byte 00004H Word 00003H 00005H 23H 23H is the contents of byte 00005H

FFFFEH ABH CD ABH is the contents of FFFFFH CDH Word FFFFEH

Registers of 8086 Segment Registers: CS, DS, ES, SS each of 16 bits 8 bit data Registers: AH, AL, BH, BL, CH, CL, DH, DL 16 bit data Registers: AX, BX, CX, DX, SI, DI, BP, SP 16 bit Address registers: SI, DI, BP, BX Default combination of Segment and Address registers CS:IP SS:SP SS:BP DS:BX DS:DI DS:DI (For other than string operations) ES:DI (For string operations) Special purpose Registers IP and FLAGS Flag is a bit of special information. 9 Flags in the 16 bit FLAGS register 6 Status Flags and 3 Control Flags Status flags are: Cy, Ac, S, Z, P, Overflow Control flags are: IE, T, D Special roles of some registers BX can be used as Address register CX is used as default down counter register DX used to hold 16-bit I/O port address in variable port addressing DX used to hold MS 16 bits of 32 bit result after multiplication DX used to hold MS 16 bits of 32 bit numerator before division Accumulator: 8-bit is AL 16-bit is AX 32-bit is DX AX

www.bookspar.com | Website for students | VTU NOTES 11 www.bookspar.com | Website for students | VTU NOTES

8086 Instruction set

Abbreviations used

R8= AL/BL/CL/DL/ AH/BH/CH/DH R16=AX/BX/CX/DX/ SI/DI/BP/SP R=R8/R16 SR=CS/DS/ES/SS AR=SI/DI/BX/BP d16=16-bit data d8=8-bit data a8=8-bit I/O port address M8=contents of byte memory M16=contents of word memory M=M8/M16

Conventions used:

R MOV for MOV R, M and MOV M, R M

PUSH/POP R16 for PUSH R16 and POP R16

ROR R/M, 1/CL for ROR R,1 ROR M,1 ROR R,CL ROR M, CL

8086 Instruction set types

Instructions are normally discussed under:

Data Transfer instructions Ex. MOV BX, CX Arithmetic instructions Ex. ADD BX, CX Logical group of instructions Ex. AND BX, CX Stack group Ex. PUSH DX I/O group Ex. IN AL, 30H Branch group Ex. JNC LOCN String instructions Ex. MOVS Interrupt instructions Ex. INT 21H

Data Transfer group, Arithmetic group, Logical group, Stack group, and I/O group of instructions explained first. They occupy several chapters in books.

www.bookspar.com | Website for students | VTU NOTES 12 www.bookspar.com | Website for students | VTU NOTES Here, I explain them under: 2-operand instructions Ex. ADD BX, CX 1-operand instructions Ex. PUSH SI 0-operand instructions: Ex. DAA Branch group, String instructions, and Interrupt instructions are explained later.

2-Operand instructions

2-Operand instructions involving R and R/M

MOV/XCHG Data transfer ADD/ADC/SUB/SBB R Arithmetic AND/OR/XOR/TEST/CMP R/M Logical

11 instructions x 210= 11264 opcodes

MOV instruction already discussed- see Instruction template In data transfer instructions flags are not affected.

Exchange Instruction

Before After XCHG DX, [BX] DX 1234H ABCDH

BX 1000H

DS:1000H ABCDH 1234H

DS:1002H

Add instruction Unlike in 8085, result of add/subtract can be in any register or memory location

Before After ADD [BX], DX DX 1234H

BX 1000H

In 3234H, 34H has DS:1000H 2000H 3234H three 1’s. So P flag =0 DS:1002H

www.bookspar.com | Website for students | VTU NOTES 13 www.bookspar.com | Website for students | VTU NOTES Before After ADC DH ,[SI] DH 30H 81H

Add with Carry Carry flag 1 0 SI 2000H

81H DS:2000H 50H

1000 0001B(Two 1’s) DS:2001H 60H

New flag values: Ac=0, S=1, Z=0, V=1, P=1

Before After SUB DH, CL DH 30H 0BH

Subtract (without borrow)

CL 25H

0BH = 0000 1011B(Three 1’s) New flag values: Ac=1, S=0, Z=0, V=0, P=0, Cy=0

Before After SBB DH, CL DH 20H FAH

Subtract (with borrow) Cy flag 1 1 CL 25H

FAH =1111 1010(Six 1’s) 2’s complement of FAH=0000 0110 = +06 So, FAH = -06 New flag values: Ac=1, S=1, Z=0, V=0, P=1, Cy=1

Discussion about Overflow (V) flag V

23H (+ve) 43H (+ve)

+ 46H (+ve) + 54H (+ve)

= 69H (+ve) = 97H (-ve)

V= 0, Cy = 0 V = 1, Cy = 0 www.bookspar.com | Website for students | VTU NOTES 14 www.bookspar.com | Website for students | VTU NOTES

Correct answer Wrong answer

Overflow used with signed numbers only Carry flag used with unsigned numbers only

83H (-ve) F2H (-ve)

+ 94H (-ve) + F3H (-ve)

= 17H (+ve) = E5H (-ve)

V= 1, Cy = 1 V = 0, Cy = 1

Wrong answer Correct answer

94H (-ve) F6H (-ve)

- 83H (-ve) - 43H (+ve)

= 11H (+ve) = B3H (-ve)

V= 0, Cy = 0 V = 0, Cy = 0

Correct answer Correct answer

94H (-ve) 66H (+ve)

- 23H (+ve) - 83H (-ve)

= 71H (+ve) = E3H (-ve)

V= 1, Cy = 0 V = 1, Cy = 1

Wrong answer Wrong answer

AND instruction

Before After AND BH, CL BH 56H 06H

Subtract (with borrow) AND 1 1 www.bookspar.com | Website for students | VTU NOTES 15 www.bookspar.com | Website for students | VTU NOTES 0FH=0000 1111B CL 0FH

06H=0000 0110B Use: Selectively reset to 0 some bits of the destination Bits that are ANDed with 0’s are reset to 0 Bits that are ANDed with 1’s are not changed

OR instruction Before After OR BH, CL BH 56H 5FH

56H=0101 0110B OR 0FH=0000 1111B CL 0FH

5FH=0101 1111B Use: Selectively set to 1 some bits of the destination Bits that are ORed with 1’s are set to 1 Bits that are ORed with 0’s are not changed

Ex-OR instruction Before After XOR BH, CL BH 56H 59H

56H=0101 0110B XOR 0FH=0000 1111B CL 0FH

59H=0101 1001B Use: Selectively complement some bits of the destination. Bits that are XORed with 1’s are complemented Bits that are XORed with 0’s are not changed

TEST instruction Before After TEST BH, CL BH 56H 56H

56H=0101 0110B AND 0FH=0000 1111B CL 0FH 0FH

06H=0000 0110B Only flages are affected Temp 45H 06H

www.bookspar.com | Website for students | VTU NOTES 16 www.bookspar.com | Website for students | VTU NOTES TEST basically performs AND operation. Result of AND is not stored in destination. It is stored in Temp register. Temp is not accessible to programmer. There is no instruction like MOV Temp, 67H

Compare Instruction Before After CMP BH, CL BH 56H 56H 56H=0101 0110B

0FH=0000 1111B CL 0FH Only flags are affected Temp 45H 47H

CMP basically performs Subtract operation. Result of CMP is not stored in destination. It is stored in Temp register. Temp is not accessible to programmer.

2-Operand Instructions involving immediate data

MOV ADD/ADC/SUB/SBB R/M, d8/d16 AND/OR/XOR/TEST/CMP 8 byte registers + 8 word registers+ 24 byte memory + 24 word memory = 64 opcodes 10 instructions x 64 = 640 opcodes

Move Immediate data to a Register/ Memory location

Before After MOV DX, ABCDH DX 1234H ABCDH

Before After MOV BH, 12H BH 56H 12H

Add Immediate data to a Register/ Memory location

Before After

www.bookspar.com | Website for students | VTU NOTES 17 www.bookspar.com | Website for students | VTU NOTES ADD [BX], 12H BX 1000H

DS:1000H 20H 32H DS:1001H

Before After ADD [BX], 1234H BX 1000H

DS:1000H 2000H 3234H

DS:1002H

Add with Carry Immediate data to a Register/ Memory location

Before After ADC DH, 32H DH 30H 63H

Add with Carry Carry flag 1 0

63H= 0110 0011 It has four 1’s New flag values: Ac=0, S=0, Z=0, V=0, P=1

Subtract Immediate data from a Register/ Memory location

Before After SUB DH, 40H DH 30H F0H

Subtract (without borrow) F0H=1111 0000 B(Four 1’s) New flag values: Ac=0, S=1, Z=0, V=0, P=1, Cy=1

Subtract with borrow Immediate data from a Register/ Memory location

Before After SBB DH, 25H DH 20H 06H

Subtract (with borrow) Cy flag 1 1

06H= 0000 0110B(Two 1’s) New flag values: Ac=1, S=0, Z=0, V=0, P=1, Cy=1

AND Immediate data with a Register/ Memory location www.bookspar.com | Website for students | VTU NOTES 18 www.bookspar.com | Website for students | VTU NOTES

Before After AND BH, 0FH BH 56H 06H

56H = 0101 0110B AND

0FH = 0000 1111B Cy flag 1 1

06H = 0000 0110B(Two 1’s) Use: Selectively reset to 0 some bits of the destination Bits that are ANDed with 0’s are reset to 0 Bits that are ANDed with 1’s are not changed

OR Immediate data with a Register/ Memory location

Before After OR BH, 0FH BH 56H 5FH

56H = 0101 0110B OR

0FH = 0000 1111B CL 0FH

5FH = 0101 1111B Use: Selectively set to 1 some bits of the destination Bits that are ORed with 1’s are set to 1 Bits that are ORed with 0’s are not changed

Ex-OR Immediate data with a Register/ Memory location

Before After XOR BH, 0FH BH 56H 59H

56H = 0101 0110B XOR 0FH = 0000 1111B CL 0FH

59H = 0101 1001B Use: Selectively complement some bits of the destn. Bits that are XORed with 1’s are complemented Bits that are XORed with 0’s are not changed

Test Immediate data with a Register/ Memory location

www.bookspar.com | Website for students | VTU NOTES 19 www.bookspar.com | Website for students | VTU NOTES Before After TEST BH, 0FH BH 56H 56H

56H=0101 0110B AND

0FH=0000 1111B Temp 45H 06H

06H=0000 0110B TEST basically performs AND operation. Result of AND is not stored in destination. It is stored in Temp register. Temp is not accessible to programmer. There is no instruction like MOV Temp, 67H. Only flags are affected.

Compare Immediate data with a Register/ Memory location

Before After CMP BH, 0FH BH 56H 56H

56H=0101 0110B AND Temp 45H 47H

CMP basically performs Subtract operation. Result of CMP is not stored in destination. It is stored in Temp register. Temp is not accessible to programmer. Only Flags are affected based result of subtraction.

2-Operand Instructions involving SR and R16/M16

SR MOV R16/M16

Before After MOV DS, CX DS 1122H 2233H

CX 2233H

Note that there is no instruction to load an immediate data to a Segment register. No. of opcodes = 2 x 4 x (8+24) = 256

Before After MOV DS, [BX] DS 1122H 2233H

www.bookspar.com | Website for students | VTU NOTES 20 www.bookspar.com | Website for students | VTU NOTES BX 2000H

DS:2000H 2233H

2-Operand Instructions to perform Input operation

IN AL/AX, a8/DX 4 opcodes

Before After IN AL, DX AL 50H 45H

DX 2111H

Input port no. 2111H 45H

Before After IN AL, 30H AL 45H 50H Input port no. 30H 45H

Before After IN AX, DX AX 3050H 4045H

DX 1177H Input port no. 60H 45H

Input port no. 61H 40H

2-Operand Instructions to perform Output operation

OUT a8/DX, AL/AX 4 opcodes

Before After OUT 30H, AL AL 50H

Out port no. 30H 40H 50H

Before After OUT DX, AX AX 3050H

www.bookspar.com | Website for students | VTU NOTES 21 www.bookspar.com | Website for students | VTU NOTES DX 2177H Out port no. 2177H 45H 50H

Out port no. 2178H 40H 30H

Before After OUT 60H, AX AX 3050H

Out port no. 60H 45H 50H

Out port no. 61H 40H 30H

2-Operand Instructions to perform Shift/Rotate operation

ROR /ROL /RCR /RCL /SHR /SHL /SAR R/M, 1/CL

7 instructions x (16+48) x 2 = 896 opcodes

SHR and SHL: for shifting left / right unsigned numbers SAR used Shifting right a signed number SHL is also called as SAL, as method for shift left of signed or unsigned number is the same

ROR R/M, 1/CL Used for division by power of 2

CL has no. of times rotation is to be done

ROR BH, 1 R/M Cy

Rotate right without cy Before After

BH 0100 0010 0010 0001

Cy 1 0

RCR R/M, 1/CL

CL has no. of times rotation is to be done

RCR BH, 1 R/M Cy

www.bookspar.com | Website for students | VTU NOTES 22 www.bookspar.com | Website for students | VTU NOTES

Rotate right with cy Before After

BH 0100 0010 1010 0001

Cy 1 0

ROL R/M, 1/CL Used for multiplication by 2n

ROL BH, CL Cy R/M

Rotate left without cy Before After

BH 0010 0010 1000 1000

CL 02H

Cy 1 0

RCL R/M, 1/CL

RCL BH, CL Cy R/M

Rotate left with cy Before After

BH 0010 0010 1000 0010

CL 02H

Cy 1 0

SHL R/M, 1/CL Used for multiplication by 2n

SHL BH, CL Cy R/M

0

www.bookspar.com | Website for students | VTU NOTES 23 www.bookspar.com | Website for students | VTU NOTES Shift left without cy Before After

BH 0010 0010 1000 1000

CL 02H

Cy 1 0

SHR R/M, 1/CL Used for division by 2n of unsigned nos

SHR BH, CL R/M Cy

0

Shift right Before After

BH 0100 0100 0001 0001

CL 02H

Cy 1 0

SAR R/M, 1/CL Used for division by 2n of signed nos

SAR BH, CL R/M Cy

Shift right Before After

1100 0000 = -40H BH 1100 0000 1111 0000

1111 0000 = -10H CL 02H

Cy 1 0

2-Operand instruction to load an Effective address into an Address Register

LEA AR, a16 4 x 24 = 96 opcodes

Before After LEA BX, [SI] BX 1000H 2000H

www.bookspar.com | Website for students | VTU NOTES 24 www.bookspar.com | Website for students | VTU NOTES LEA BX, [SI] functionally same as SI 2000H

MOV BX,SI DS:2000H 3000H

2-Operand instruction to load DS and an Address Register from memory

LDS AR, M32 4 x 24 = 96 opcodes

Before After LDS SI, 3000H DS 2000H 7000H

Loads DS and SI using single instruction

SI 1000H 6000H

DS:3000H 6000H

DS:3002H 7000H

2-Operand instruction to load ES and an Address Register from memory LES AR, M32 4 x 24 = 96 opcodes

Before After LES DI, 3000H ES 2000H 7000H

Loads ES and DI using single DI 1000H 6000H instruction 2000:3000H 6000H

2000:3002H 7000H

www.bookspar.com | Website for students | VTU NOTES 25 www.bookspar.com | Website for students | VTU NOTES 1-Operand instruction types

1 INC/ DEC/ NOT/NEG R/M

4 x (16+48) = 256 opcodes

2 PUSH/ POP R16/M16/SR/F

2 x (8+24+4+1) = 74 opcodes

3 MUL/ IMUL/ DIV/ DIV R/M

4 x (16+48) = 256 opcodes

Increment R16

INC BX 8 opcodes Before After

Ex. 1 BX 1234H 1235H

Ex. 2 BX FFFFH 0000H

Increment R8

INC DH 8 opcodes Before After

Ex. 1 DH 12H 13H

Ex. 2 DH FFH 00H

Increment M8

INC byteptr [BX] Before After 24 opcodes BX 2000H DS:2000H FFH 00H DS:2001H 12H 12H

NOTE:- In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. Byteptr assembler directive announces to the assembler that it is a byte operation.

www.bookspar.com | Website for students | VTU NOTES 26 www.bookspar.com | Website for students | VTU NOTES Increment M16

INC wordptr [BX] Before After

24 opcodes BX 2000H

DS:2000H FFH 00H

DS:2001H 12H 13H

NOTE:- In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. wordptr assembler directive announces to the assembler that it is a word operation. Decrement R16

DEC BX 8 opcodes Before After

Ex. 1 BX 1234H 1233H

Ex. 2 BX 0000H FFFFH

Decrement R8 DEC DH 8 opcodes Before After

Ex. 1 DH 12H 11H Ex. 2 DH 00H FFH

Decrement M8

DEC byteptr [BX] Before After 24 opcodes BX 2000H DS:2000H 00H FFH DS:2001H 12H 12H

NOTE:-In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. Byteptr assembler directive announces to the assembler that it is a byte operation. Decrement M16 DEC wordptr [BX] Before After

24 opcodes BX 2000H

DS:2000H 00H FFH

DS:2001H 12H 11H

www.bookspar.com | Website for students | VTU NOTES 27 www.bookspar.com | Website for students | VTU NOTES NOTE:- In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. wordptr assembler directive announces to the assembler that it is a word operation. Perform 1’s complement of R16

NOT BX 8 opcodes Before After

1234H EDCBH BX

NOT operation performs 1’s complement. Easy way: Subtract each hex digit from F

Perform 1’s complement of R8

NOT DH 8 opcodes Before After

DH 12H EDH

Perform 1’s complement of M8 NOT byteptr [BX] Before After 24 opcodes BX 2000H DS:2000H 23H DCH DS:2001H 12H 12H

NOTE:- In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. Byteptr assembler directive announces to the assembler that it is a byte operation.

Perform 1’s complement of M16

NOT wordptr [BX] Before After

24 opcodes BX 2000H

DS:2000H 34H CBH

DS:2001H 12H EDH

NOTE:- In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. wordptr assembler directive announces to the assembler that it is a word operation.

Perform 2’s complement of R16

www.bookspar.com | Website for students | VTU NOTES 28 www.bookspar.com | Website for students | VTU NOTES NEG BX 8 opcodes Before After

1234H EDCCH BX

NEG operation performs 2’s complement. Easy way: Subtract each hex digit from F and add 1

Perform 2’s complement of R8

NEG DH 8 opcodes Before After

DH 12H EEH

Perform 2’s complement of M8

NEG byteptr [BX] Before After 24 opcodes BX 2000H DS:2000H 23H DDH DS:2001H 12H 12H

NOTE:- In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. Byteptr assembler directive announces to the assembler that it is a byte operation.

Perform 2’s complement of M16

NEG wordptr [BX] Before After

24 opcodes BX 2000H

DS:2000H 34H CBH

DS:2001H 12H EDH

NOTE:- In this instruction there is a single operand, [BX]. It is not clear whether it is byte or word operand. wordptr assembler directive announces to the assembler that it is a word operation.

PUSH R16

Ex. PUSH CX Before After CX 1234H SP 5678H 5676H Empty www.bookspar.com | Website for students | VTU NOTES 29 www.bookspar.com | Website for students | VTU NOTES Empty SS: 5676H 1122H Full 1234H Full SS:5678H 3344H 3344H

Suppose SP content is 5678H. It means locations 5678, 567A, 567C … in stack segment are full. Locations 5676, 5674, … are empty. Information pushed to location 5676 and SP value changes to 5676H. Push operation is always on 16 bit data.

PUSH M16

Ex. PUSH [BX] Before After BX 1234H SP 3366H 3364H DS:1234H 5678H Empty Empty SP: 5676H 1122H Full 5678H Full SP: 5678H 3344H 3344H

PUSH SR

Ex. PUSH CS Before After CS 1234H SP 5678H 5676H Empty Empty SS: 5676H 1122H Full 1234H Full SS: 5678H 3344H 3344H

PUSH Flags

Ex. PUSHF Before After Flags 1234H SP 5678H 5676H Empty Empty SS: 5676H 1122H Full 1234H Full SS: 5678H 3344H 3344H

POP R16

Ex. POP CX Before After CX 1234H 1122H SP 5678H 567AH Empty Full SS: 5678H 1122H Empty 1122H SS: 567AH 3344H Full 3344H

www.bookspar.com | Website for students | VTU NOTES 30 www.bookspar.com | Website for students | VTU NOTES NOTE:- Suppose SP content is 5678H. It means locations 5678, 567A, 567C … in stack segment are full. Locations 5676, 5674, … are empty. Information poped from location 5678 and SP value changes to 567AH. Pop operation is always on 16 bit data.

POP M16

Ex. POP [BX] Before After BX 1234H SP 3366H 3368H DS:1234H 5678H 1122H Empty Full SS: 3366H 1122H Empty 1122H SS: 3368H 3344H Full 3344H

POP SR

Ex. POP CS Before After CS 1234H 1122H SP 5678H 567AH Empty Full SS: 5678H 1122H Empty 1122H SS: 567AH 3344H Full 3344H

POP Flags

Ex. POPF Before After Flags 1234H 1122H SP 5678H 567AH Empty Full SS: 5678H 1122H Empty 1122H SS: 567AH 3344H Full 3344H

Unsigned Multiply R8 with AL and store product in AX

MUL CH Before After CH FEH FEH AL 02H FCH 01FCH = 508 AH 34H 01H

Unsigned Multiply R16 with AX and store product in DX AX

MUL CX Before After

www.bookspar.com | Website for students | VTU NOTES 31 www.bookspar.com | Website for students | VTU NOTES CX 00FEH 00FEH AX 0002H 01FC 01FCH = 508 H DX 1234H 0000H

Signed Multiply R8 with AL and store product in AX

IMUL CH Before After

FEH = -02 CH FEH AL 02H FCH FFFCH = -04 AH 34H FFH

NOTE:- IMUL CH instruction multiplies AL and CH treating them as signed numbers. The 16-bit product is stored in AX.

Unsigned Division of AX by R8 and store quotient in AL and remainder in AH

DIV CH Before After CH F0H AL 25H 01H Quotient AH 01H 35H Remainder

NOTE:- DIV CH instruction divides AX by CH treating them as unsigned numbers. The 8-bit quotient is stored in AL and the 8-bit remainder stored in AH.

Unsigned Division of DX AX by R16 and store quotient in AX and remainder in DX

DIV CX Before After CX 00F0H AX 0125H 0001H Quotient DX 0000H 0035H Remainder

NOTE:- DIV CX instruction divides DX AX by CX treating them as unsigned numbers. The 16-bit quotient is stored in AX and the 16-bit remainder stored in DX. Signed Division of AX by R8 and store quotient in AL and remainder in AH

IDIV CH Before After F0H = -10H CH F0H EE = -12H AL 25H EEH Quotient AH 01H 05H Remainder

NOTE:-IDIV CH instruction divides AX by CH treating them as signed numbers. The 8- bit quotient is stored in AL and the 8-bit remainder stored in AH.

www.bookspar.com | Website for students | VTU NOTES 32 www.bookspar.com | Website for students | VTU NOTES Branch group of instructions

Branch instructions provide lot of convenience to the programmer to perform operations selectively, repetitively etc.

Branch group of instructions

Conditional Uncondi-tional Iteration CALL Return jumps jump instructions instructions instructions

Conditional Jump instructions

Conditional Jump instructions in 8086 are just 2 bytes long. 1-byte opcode followed by 1-byte signed displacement (range of –128 to +127).

Conditional Jump Instructions

Jumps based on a single flag Jumps based on more than one flag

Jumps Based on a single flag

ExamplesJZ r8 for;Jump JE or if JZ zero instruction flag set (if result is 0). JE also means same. JNZ r8 ;Jump if Not Zero. JNE also means same. JS r8 ;Jump if Sign flag set to 1 (if result is negative) JNS r8 ;Jump if Not Sign (if result is positive) JC r8 ;Jump if Carry flag set to 1. JB and JNAE also mean same. JNC r8 ;Jump if No Carry. JAE and JNB also mean same. JP r8 ;Jump if Parity flag set to 1. JPE (Jump if Parity Even) also means same. JNP r8 ;Jump if No Parity. JPO (Jump if Parity Odd) also means same. JO r8 ;Jump if Overflow flag set to 1 (if result is wrong) JNO r8 ;Jump if No Overflow (if result is correct)

JE is abbreviation for Jump if Equal. JNE is abbreviation for Jump if Not Equal. JB is abbreviation for Jump if Below. JNAE is for Jump if Not Above or Equal. JAE for Jump if Above or Equal. JNB for Jump if Not Above.

JZ, JNZ, JC and JNC used after arithmetic operation

JE,www.bookspar.com JNE, JB, JNAE, JAE | Website and JNB for arestudents used after| VTU a compareNOTES operation. 33 www.bookspar.com | Website for students | VTU NOTES

Ex. for forward jump Only examples using JE instruction given for forward and backward jumps.

CMP SI, DI

JE SAME

ADD CX, DX ;Executed if Z = 0

Should be<=127 bytes : (if SI not equal to DI)

:

SAME: SUB BX, AX ;Executed if Z = 1

(if SI = DI)

Ex. for backward jump

BACK: SUB BX,AX ;Executed if Z = 1 (if SI=DI)

:

Should be : <=127 bytes CMP SI, DI

JE BACK

ADD CX,DX ;Executed if Z = 0 (if SI <> DI)

Jumping beyond -128 to +127?

Requirement Then do this!

CMP SI, DI CMP SI, DI JE SAME JNE NEXT What if ADD CX, DX JMP SAME >127 bytes : NEXT: ADD CX, DX

www.bookspar.com | Website for students | VTU NOTES 34 www.bookspar.com | Website for students | VTU NOTES : : SAME: SUB BX, AX :

SAME: SUB BX, AX

Range for JMP (unconditional jump) can be +215 = + 32K. JMP instruction discussed in detail later

Terms used in comparison

Above and Below used for comparing Unsigned numbers. Greater than and less than used when comparing signed numbers. All Intel microprocessors use this convention. Accordingly, all the following statements are true. 95H is above 65H Unsigned comparison - True 95H is less than 65H Signed comparison – True (as 95H is negative, 65H is positive) 65H is below 95H Unsigned comparison - True 65H is greater than 95H Signed comparison - True

Jump based on multiple flags

Conditional Jumps based on multiple flags are used after a CMP (compare) instruction.

JBE / JNA instruction

‘Jump if Below or Equal’ or ‘Jump if Not Above’

Jump if No Jump if Ex.

Cy = 1 OR Z= 1 Cy = 0 AND Z = 0 CMP BX, CX

Below OR Equal Surely Above JBE BX_BE

BX_BE (BX is Below or Equal) is a symbolic location

JNBE / JA instruction

‘ Jump if Not (Below or Equal)’ or ‘Jump if Above’

www.bookspar.com | Website for students | VTU NOTES 35 www.bookspar.com | Website for students | VTU NOTES Jump if No Jump if Ex.

Cy = 0 AND Z= 0 Cy = 1 OR Z = 1 CMP BX, CX

Surely Above Below OR Equal JBE BX_BE

JLE / JNG instruction

‘Jump if Less than OR Equal’ or ‘Jump if Not Greater than’ Jump if No Jump if

[(S=1 AND V=0) OR (S=0 AND V=0)] [(S=0 AND V=0) OR (S=1 AND V=1)] OR Z=1 AND Z=0 [(surely negative) or (wrong answer [(surely positive) or (wrong answer positive!)] or Equal negative!)] and not equal i.e. [S XOR V=1] OR Z=1 i.e.[S XOR V=0] AND Z=0

JNLE / JG instruction

‘Jump if Not (Less than OR Equal)’ or ‘Jump if Greater than’ No Jump if Jump if [(S=0 AND V=0) OR (S=1 AND V=1)] [(S=1 AND V=0) OR (S=0 AND V=1)] AND Z=0 OR Z=1 [(surely positive) or (wrong answer [(surely negative) or (wrong answer negative!)] and not equal positive!)] or equal

i.e. S XOR V=0 AND Z=0 i.e.S XOR V=1 OR Z=1

JL / JNGE instruction

‘Jump if Less than’ or ‘Jump if NOT (Greater than or Equal)’

Jump if No Jump if [S=1 AND V=0] OR [S=0 AND V=1] [S=0 AND V=0] OR [S=1 AND V=1] (surely negative)or (wrong answer (surely positive) or (wrong answer positive!) negative!)

i.e. S XOR V=1 i.e.S XOR V=0 Note: When S=1, result cannot be 0

www.bookspar.com | Website for students | VTU NOTES 36 www.bookspar.com | Website for students | VTU NOTES JNL / JGE instruction

‘Jump if Not Less than’ or ‘Jump if Greater than OR Equal’

Jump if No Jump if [S=0 AND V=0] OR (S=1 AND V=1) [S=1 AND V=0] OR (S=1 AND V=1) (surely positive) or (wrong answer (surely negative) or (wrong answer negative!) positive!)

i.e. S XOR V=0 i.e.S XOR V=1 Note: When S=0, result can be >= 0

Unconditional Jump instruction

Unconditional Jump Instruction

Near Jump or Intra segment Jump Far Jump or Inter segment Jump

(Jump within the segment) (Jump to a different segment)

Near Unconditional Jump instruction

Near Jump

Direct Jump (common) Indirect Jump (uncommon)

2-bytes Short Jump (EB r8) 3-bytes Long Jump (E9 r16) 2 or more bytes Starting with FFH Range: + 27 Range: +215 Range: complete segment

Three Near Jump and two Far Jump instructions have the same mnemonic JMP, but they have different opcodes

Short Jump Instruction

2 byte (EB r8) instruction with Range: -128 to +127 bytes

For Backward jump: Assembler knows the quantum of jump. Generates Short Jump code if <=128 bytes is the required jump. Generates code for Long Jump if >128 bytes is the required jump.

For Forward jump: Assembler doesn’t know jump quantum in pass 1. Assembler www.bookspar.com | Website for students | VTU NOTES 37 www.bookspar.com | Website for students | VTU NOTES reserves 3 bytes for the forward jump instruction. If jump distance turns out to be >128 bytes, the instruction is coded as E9 r16 (E9H = Long jump code). If jump distance becomes <=128 bytes, the instruction is coded as EB r8 followed by code for NOP (E8H = Short jump code).

SHORT Assembler Directive

Assembler generates only 2 byte Short Jump code for forward jump, if the SHORT assembler directive is used.

JMP SHORT SAME

:

Programmer should ensure that : the Jump distance is <=127 bytes SAME: MOV CX, DX

Long Jump instruction

3-byte (E9 r16) instruction with Range: -32768 to +32767 bytes

Long Jump can cover entire 64K bytes of Code segment

CS:0000H :

: CS:8000H JMP FRWD

Long Jump can handle it as jump : quantum is <=32767 :

FRWD = CS:FFFFH :

Long Jump can handle it as jump BKWD= CS:0000H : quantum is <=32767 : CS:8000H JMP BKWD

:

FRWD = CS:FFFFH :

www.bookspar.com | Website for students | VTU NOTES 38 www.bookspar.com | Website for students | VTU NOTES Long Jump or Short Jump?

Can be treated as a CS:0000H : small (20H) Backward : Jump distance =FFE0H. Branch! CS:0010H JMP FRWD Too very long forward : jump.

FRWD = CS:FFF0H : : CS:FFFFH :

Can be treated as a CS:0000H : small (20H) : Jump distance =FFE0H. Forward Branch! BKWD = CS:0010H : Too very long : backward jump CS:FFF0H JMP BKWD : CS:FFFFH :

Intra segment indirect Jump

It is also called Near Indirect Jump. It is not commonly used. Instruction length: 2 or more bytes Range: complete segment

Ex.1: JMP DX If DX = 1234H, branches to CS:1234H. 1234H is not signed relative displacement.

Ex. 2: JMP wordptr 2000H[BX]

If BX contents is DS:3234H 5678H 1234H

Branches to CS:5678H DS:3236H AB22H

Far Jump instruction

Far Jump

Direct Jump (common) Indirect Jump (uncommon)

5 bytes, opcode EA, 2 byte offset, 2 or more bytes, 2 byte segment value starting with opcode FFH www.bookspar.com | Website for students | VTU NOTES 39 www.bookspar.com | Website for students | VTU NOTES

Range: anywhere in memory Range: anywhere in memory

As stated earlier, three Near Jump and two Far Jump instructions have the same mnemonic JMP but different opcodes.

Inter segment Direct Jump instruction

Also called Far Direct Jump. It is the common inter segment jump scheme

It is a 5 byte instruction. 1 byte opcode (EAH), 2 byte offset value, 2 byte segment value

Ex. JMP Far ptr LOC

Inter segment Indirect Jump instruction

Also called Far Indirect Jump. It is not commonly used. Instruction length depends on the way jump location is specified. It can be a minimum of 2 bytes.

Ex. JMP DWORD PTR 2000H[BX]

If BX contents is 1234H branch takes place to location ABCDH:5678H. It is a 4-byte instruction.

DS:3234H 5678H

DS:3236H ABCDH

Iteration Instructions

Iteration instructions provide a convenient way to implement loops in a program

Iteration instructions

LOOP LOOPZ or LOOPE LOOPNZ or LOOPNE JCXZ

LOOP Instruction

www.bookspar.com | Website for students | VTU NOTES 40 www.bookspar.com | Website for students | VTU NOTES Let us say, we want to repeat a set of instructions 5 times.

For 8085 processor For 8086processor

MVI C, 05H MOV CX, 0005H

AGAIN: MOV B, D AGAIN: MOV BX, DX

: :

DCR C LOOP AGAIN

JNZ AGAIN

General format: LOOP r8; r8 is 8-bit signed value. It is a 2 byte instruction. Used for backward jump only. Maximum distance for backward jump is only 128 bytes. LOOP AGAIN is almost same as: DEC CX JNZ AGAIN LOOP instruction does not affect any flags. If CX value before entering the iterative loop is: 0005, then the loop is executed 5 times till CX becomes 0 0001, then the loop is executed 1 time till CX becomes 0 0000, then the loop is executed FFFF+1 = 10000H times!

JCXZ Instruction

Jump if CX is Zero is useful for terminating the loop immediately if CX value is 0000H It is a 2 byte instruction. It is used for forward jump only. Maximum distance for forward jump is only 127 bytes.

Ex. MOV CX, SI

JCXZ SKIP

AGAIN: MOV BX, DX

:

:

LOOP AGAIN

SKIP: ADD SI, DI ; Executed after JCXZ if CX = 0

LOOPZ instruction www.bookspar.com | Website for students | VTU NOTES 41 www.bookspar.com | Website for students | VTU NOTES

LOOP while Zero is a 2-byte instruction. It is used for backward jump only. Backward jump takes place if after decrement of CX it is still not zero AND Z flag = 1. LOOPE is same as LOOPZ. LOOPE is abbreviation for LOOP while Equal. LOOPE is normally used after a compare instruction.

Ex. MOV CX, 04H

BACK: SUB BX, AX

MOV BX, DX

:

:

ADD SI, DI

LOOPZ BACK ; if SI+DI = 0 and CX not equal to 0, branch to BACK

CALL Instructions

CALL instruction is used to branch to a subroutine. There are no conditional Call instructions in 8086.

CALL instructions

Near CALL or Intra segment CALL Far CALL or Inter segment CALL

Near Direct CALL Near Indirect CALL Far Direct CALL Far Indirect CALL

Near Direct CALL instruction

It is a 3-byte instruction. It has the format CALL r16 and has the range + 32K bytes. Covers the entire Code segment. It is the m ost common CALL instruction.

It is functionally same as the combination of the instructions PUSH IP and ADD IP, r16.

Ex. CALL Compute

www.bookspar.com | Website for students | VTU NOTES 42 www.bookspar.com | Website for students | VTU NOTES Near Indirect CALL instruction

Not commonly used. Instruction length depends on the way the called location is specified.

Ex.1: CALL AX ; If (AX) = 1234H, branches to procedure at CS: 1234H. 1234H is not relative displacement.

Ex. 2: CALL word ptr 2000H[BX]

If BX contents is 1234H Branches to subroutine at CS:5678H

DS:3234H 5678H

DS:3236H ABCDH

Far Direct CALL instruction

It is a 5-byte instruction. 1-byte opcode, 2-byte offset, 2-byte segment value. Far direct CALL is functionally same as: PUSH CS PUSH IP IP = 2-byte offset value provided in CALL CS = 2-byte segment value provided in CALL

Ex. CALL far ptr Compute

Far Indirect CALL instruction

Not commonly used. Instruction length depends on the way the called location is specified.

Ex. CALL dword ptr 2000H[BX]

If BX contents is 1234H b Branches to subroutine at ABCDH:5678H

DS:3234H 5678H

DS:3236H ABCDH

www.bookspar.com | Website for students | VTU NOTES 43 www.bookspar.com | Website for students | VTU NOTES Conditional CALL?

What if we want to branch to subroutine COMPUTE only if Cy flag = 0?

Solution:

JC NEXT CALL COMPUTE ; execute only if Cy = 0

NEXT:

RETURN instructions

RET is abbreviation for Return from subroutine

RET instructions

Near RET or Intra segment RET Far RET or Inter segment RET

RET RET d16 RET RET d16

Near RET instruction

It is 1-byte instruction. Opcode is C3H. It is functionally same as : POP IP Ex:

Compute Proc Near ; indicates it is a NEAR procedure

: :

RET

Compute ENDP ; end of procedure Compute

In fact, default procedure type is NEAR

Near RET d16 instruction

www.bookspar.com | Website for students | VTU NOTES 44 www.bookspar.com | Website for students | VTU NOTES It is a 3-byte instruction. 1-byte opcode (C2H) and 2-byte data. It is functionally same as: POP IP SP = SP + d16

Ex. RET 0004H

RET d16 is useful for flushing out the parameters that were passed to the subroutine using the stack

Use of RET d16 instruction

Main Program : : SP after CALL Compute IP PUSH Var1 Var2 PUSH Var2 Var1 CALL Compute SP before PUSH Var1 : :

Subroutine COMPUTE PROC Near IP : SP if RET is executed Var2 : Var1 RET 0004H SP if RET 0004H is executed COMPUTE ENDP

Far RET instruction

It is 1-byte instruction. Opcode is CBH. It is functionally same as: POP IP + POP CS

Ex. SINX Proc Far ; indicates it is a FAR procedure

:

:

www.bookspar.com | Website for students | VTU NOTES 45 www.bookspar.com | Website for students | VTU NOTES RET

SINX ENDP ; end of procedure SINX

Default procedure type is NEAR

Far RET d16 instruction

It is a 3-byte instruction. 1-byte opcode (CAH) and 2-byte data.

It is functionally same as: POP IP + POP CS + ADD SP, d16

Ex. RET 0006H

RET d16 is useful for flushing out the parameters that were passed to the subroutine using the stack.

www.bookspar.com | Website for students | VTU NOTES 46 www.bookspar.com | Website for students | VTU NOTES Interrupts & related instructions

Types of data transfer

Simple I/O – used when timings of I/O device is known (Ex. Collect newspaper leisurely any time after 8 a.m.)

Status check I/O – Data transfer done anytime after I/O device says it is ready (Ex. Check newspaper box and collect newspaper if it is in the box)

Interrupt driven I/O – data transfer done immediately after I/O device interrupts (Ex. Collect newspaper when the door bell rings indicating delivery of newspaper)

In this section only Interrupt driven I/O is discussed.

Interrupt driven I/O

Interrupt types

Hardware interrupts Software interrupts Exceptions or Traps

Ex. NMI and INTR pins Ex. INT n, INT 3, INTO Ex. Divide by zero error, instructions Single step interrupt

Interrupt type numbers

Every interrupt type in 8086 has an 8-bit Interrupt type number (ITN) as shown below.

ITN Interrupt type ITN Interrupt type

0 Divide by 0 error 5 Out of bound(80286)

1 Single step interrupt 6 Invalid opcode

2 NMI 7 No Coprocessor

3 Break point interrupt 8 Double fault (during an

4 Overflow error instruction 2 interrupts)

5 -1F Reserved by Intel. 20-FF Available for user.

www.bookspar.com | Website for students | VTU NOTES 47 www.bookspar.com | Website for students | VTU NOTES 13H for Disk services INT 21H for DOS services.

Action when NMI is activated

NMI is positive edge triggered input

1. Complete the instruction in progress

2. Push Flags on the stack

3. Reset IE flag (to ensure no further interrupts)

4. Reset T flag (so that interrupt service subroutine, ISS, is not executed in single step)

5. PUSH CS

6. PUSH IP

7. IP loaded from word location 2 x 4 = 8 (2 is ITN)

8. CS loaded from next word location (0000AH)

Processor makes a branch to the subroutine!

Interrupt Vector table (IVT)

RAM locations 0 to 003FFH are used to store IVT. It contains 256 Interrupt Vectors (IV) each of 4 bytes.

00000H 1234H 5678:1234H is IV number 0 00002H 5678H

00004H 3344H 5566:3344H is IV number 1 00006H 5566H

: : :

003FCH 6677H 7788:6677H is IV number FF

www.bookspar.com | Website for students | VTU NOTES 48 www.bookspar.com | Website for students | VTU NOTES 003FEH 7788H

Execution of INT n (n=0 to FF)

1. Push Flags on the stack

2. Reset IE flag (to ensure no further interrupts)

3. Reset T flag (so that ISS is not executed in single step)

4. PUSH CS

5. PUSH IP

6. IP loaded from word location n x 4 = say, W

7. CS loaded from next word location W+2

In INT n, which is a 2-byte instruction, n is the ITN. INT n has the opcode CDH

Action when INT 3 is executed

1. Push Flags on the stack

2. Reset IE flag (to ensure no further interrupts)

3. Reset T flag (so that ISS is not executed in single step)

4. PUSH CS

5. PUSH IP

6. IP loaded from word location 3 x 4 = 0000CH

7. CS loaded from next word location 0000EH

INT 3 is a 1-byte instruction with opcode of CCH

What is divide by 0 error?

www.bookspar.com | Website for students | VTU NOTES 49 www.bookspar.com | Website for students | VTU NOTES Ex. DIV BL Before After

AH 40H 00H This is an example for divide by 0 error. It only means quotient is too large for the register! AL 60H 2030H

BL 02H

Action for divide by 0 error

For divide by 0 error the ITN is 0

1. Push Flags on the stack

2. Reset IE flag (to ensure no further interrupts)

3. Reset T flag (so that ISS is not executed in single step)

4. PUSH CS

5. PUSH IP

6. IP loaded from word location 0 x 4 = 00000H

7. CS loaded from next word location 00002H

Processor makes a branch to the subroutine at location 5678:1234H if the contents of IVT is as shown in the table above.

Action for Single step interrupt

For divide by 0 error the ITN is 1

1. Push Flags on the stack

2. Reset IE flag (to ensure no further interrupts)

3. Reset T flag (so that ISS is not executed in single step)

4. PUSH CS

5. PUSH IP

6. IP loaded from word location1 x 4 = 00004H www.bookspar.com | Website for students | VTU NOTES 50 www.bookspar.com | Website for students | VTU NOTES

7. CS loaded from next word location 00006H

Processor makes a branch to the subroutine at location 5566:3344H as per the IVT

Action for INTO instruction

INTO is a 1-byte instruction. For interrupt on overflow the ITN is 4.

1. Do steps 2 to 7 only if Overflow flag is set

2. Push Flags on the stack

3. Reset IE flag and T flag

4. PUSH CS

5. PUSH IP

6. IP loaded from word location 4 x 4 = 00010H

7. CS loaded from next word location 00012H

INTO is equivalent to: JNO Next INT 4 Next: ….

Action when INTR is activated

INTR is level triggered input.

1. Complete the instruction in progress

2. Activate INTA o/p twice. In response 8086 receives ITN n instruction from an external device like 8259 PIC

3. Push Flags on the stack. Reset IE and T flags

4. PUSH CS

5. PUSH IP

6. IP loaded from word location n x 4 = say, W

www.bookspar.com | Website for students | VTU NOTES 51 www.bookspar.com | Website for students | VTU NOTES 7. CS loaded from next word location W+2

Processor makes a branch to the subroutine!

IRET (Return from Interrupt) instruction

An ISS ends with the IRET instruction. IRET is same as POP IP + POP CS + POPF

SP after branch to ISS

IP

CS

SP before branch to ISS FLA G S

Make sure ISS does not end with RET!

Priority of 8086 Interrupts

If several interrupts occur during the execution of an instruction, in which order interrupts will be serviced? There will be priorities as indicated below.

Divide by 0 error, INT n Highest priority NMI INTR Single step interrupt Lowest priority

In reality NMI has highest priority! If NMI occurs during the servicing of INT n, processor branches to NMI routine as IE flag has no effect on NMI.

www.bookspar.com | Website for students | VTU NOTES 52 www.bookspar.com | Website for students | VTU NOTES Intel 8255 PPI

PPI is abbreviation for Programmable Peripheral Interface. It is an I/O port chip used for interfacing I/O devices with microprocessor. It is a v ery commonly used peripheral chip. Knowledge of 8255 essential for students in the Microprocessors lab for interfacing experiments.

8255 40 pin DIP A7 Vcc Gnd Port A PA7-0 A6 RD*

A5 WR* PC7-4

A4 PC3-0 CS* Port C A3 Control Port

D7-0 A2

A1 Port B PB7-0 NC A0

M/IO* Reset

There are 3 ports in 8255 from user’s point of view - Port A, Port B and Port C. Port C is composed of two independent 4-bit ports : PC7-4 (PC Upper) and PC3-0 (PC Lower)

Selection of Ports

A1 A0 Selected port

0 0 Port A

0 1 Port B

1 0 Port C

1 1 Control port

There is also a Control port from the Processor point of view. Its contents decides the working of 8255. www.bookspar.com | Website for students | VTU NOTES 53 www.bookspar.com | Website for students | VTU NOTES When CS (Chip select) is 0, 8255 is selected for communication by the processor. The chip select circuit connected to the CS pin assigns addresses to the ports of 8255.

For the chip select circuit shown, the chip is selected when A7=0, A6=1, A5=1, A4=1, A3=1, A2=1, and M/IO*= 0. Port A, Port B, Port C and Control port will have the addresses as 7CH, 7DH, 7EH, and 7FH respectively. There are 3 modes of operation for the ports of 8255. Mode 0, Mode 1, and Mode 2.

Mode 0 Operation It is Basic or Simple I/O. It does not use any handshake signals. It is used for interfacing an i/p device or an o/p device. It is used when timing characteristics of I/O devices is well known.

Mode 1 Operation It uses handshake I/O. 3 lines are used for handshaking. It is used for interfacing an i/p device or an o/p device. Mode 1 operation is used when timing characteristics of I/O devices is not well known, or used when I/O devices supply or receive data at irregular intervals.

Handshake signals of the port inform the processor that the data is available, data transfer complete etc. More details about mode 1 operation is provided later.

Mode 2 Operation It is bi-directional handshake I/O. Mode 2 operation uses 5 lines for handshaking. It is used with an I/O device that receives data some times and sends data sometimes. Ex. Hard disk drive. Mode 2 operation is useful when timing characteristics of I/O devices is not well known, or when I/O devices supply or receive data at irregular intervals.

Port A can work in Mode 0, Mode 1, or Mode 2 Port B can work in Mode 0, or Mode 1 Port C can work in Mode 0 only, if at all

Port A, Port B and Port C can work in Mode 0 Port A and Port B can work in Mode 1 Only Port A can work in Mode 2

Where are the Handshake signals? We have already listed all the 40 pins of 8255. Port C pins act as handshake signals, when Port A and Port B are configured for other than Mode 0. Port A in Mode 2 and Port B in Mode 1 is possible, as it needs only 5+3 = 8 handshake signals.

www.bookspar.com | Website for students | VTU NOTES 54 www.bookspar.com | Website for students | VTU NOTES After Reset of 8255, Port A, Port B, and Port C are configured for Mode 0 operation as input ports.

PC2-0 are used as handshake signals by Port B when configured in Mode 1. This is immaterial whether Port B is configured as input or output port. PC5-3 are used as handshake signals by Port A when configured as input port in Mode 1. PC7, 6, 3 are used as handshake signals by Port A when configured as output port in Mode 1. PC7-3 are used as handshake signals by Port A when configured in Mode 2.

There are 2 control words in 8255 Mode Definition (MD) Control word and Port C Bit Set / Reset (PCBSR) Control Word

8255 Mode Definition Control word

Mode definition control word is used to configure the ports of 8255 as input or output in Mode 0, Mode 1, or Mode 2.

Control port having Mode Definition (MD) control word

1 M2A M1A I/P A I/P CU M1B I/P B I/P CL

Means Mode Definition control 1 - PCU as input word 0 - PCU as output 1 -PCL as input

1 - PA as input 0 -PCL as output

M2A 0 - PA as output 1 - PB as input M1A

0 0 Port A in Mode 0 0 - PB as output

0 1 Port A in Mode 1 1 - PB in Mode 1

1 0/1 Port A in Mode 2 0 - PB in Mode 0

Ex. 1: Configure Port A as input in Mode 0, Port B as output in mode 0, Port C (Lower) as output and Port C (Upper) as input ports.

www.bookspar.com | Website for students | VTU NOTES 55 www.bookspar.com | Website for students | VTU NOTES Required MD control word:

1 0 0 1 1 0 0 0 = 98H

MD control word PC Lower as output

PA in Mode 0 PB as output

PA as input PB in Mode 0

PC Upper as input

Required program segment for the configuration: MOV AL, 98H OUT 7FH, AL

Ex. 2: Configure Port A as input in Mode 1, Port B as output in mode 1, Port C7-6 as input ports. (PC5-0 are handshake lines, some are input lines and others are output. So they are shown as X)

Required MD control word:

1 0 1 1 1 1 0 X = BCH or BDH

MD control PC3-0 as Don’t care

PA in Mode 1 PB as output

PA as input PB in Mode 1

PC Upper (C7-6) as input

Required program segment for the configuration: MOV AL, BCH OUT 7FH, AL

Ex. 3:Configure Port A in Mode 2, Port B as output in mode 1. (PC7-3 are handshake lines for Port A and PC2-0 are handshake signals for port B)

Required MD control word:

1 1 X X X 1 0 X = C4H / C5H.. www.bookspar.com | Website for students | VTU NOTES 56 www.bookspar.com | Website for students | VTU NOTES

MD control PC3-0 as handshake

PA in Mode 2 PB as output Reqd. instrns.

PA bidirectional PB in Mode 1 MOV AL, C4H

PC 7-4 as handshake OUT 7FH, AL

Required program segment for the configuration: MOV AL, C4H OUT 7FH, AL

8255 Port C Bit Set / Reset Control word

Port C Bit Set / Reset (PCBSR) control word is used for setting to 1 or resetting to 0 any one selected bit of Port C. It is useful for enabling or disabling Port A or Port B interrupts when they are in mode 1 or mode 2.

Control port having Port C Bit Set / Reset control word

0 X X X SB2 SB1 SB0 S/ R*

PC bit set / reset Don’t cares Select bit of PC to 1 - Set to 1 control word be set / reset 0 - Reset to 0

0 0 0 Bit 0 of Port C

0 0 1 Bit 1 of Port C

: : : : : : 1 1 1 Bit 7 of Port C

Ex. 1: Set to 1 bit 4 of Port C

0 X X X 1 0 0 1 = 09H

www.bookspar.com | Website for students | VTU NOTES 57 www.bookspar.com | Website for students | VTU NOTES

PC bit set / reset Set to 1 control word Don’t cares Bit 4 of Port C

Required program segment for setting bit 4 of Port C: MOV AL, 09H OUT 7FH, AL

Ex. 2: Reset to 0 bit 6 of Port C

0 X X X 1 1 0 0 = 0CH

PC bit set / reset Don’t cares Bit 6 of Port C Reset to 0 control word

Required program segment for resetting bit 6 of Port C: MOV AL, 09H OUT 7FH, AL

PCBSR command word is used for enabling / disabling interrupts from Ports A and B when they are configured for other than Mode 0.

PA interrupt is enabled if bit 4 of PC is set to 1, for input PA interrupt is enabled if bit 6 of PC is set to 1, for output

PA interrupt is disabled if bit 4 of PC is reset to 0, for input PA interrupt is disabled if bit 6 of PC is reset to 0, for output

PB interrupt is enabled if bit 2 of PC is set to 1, for input and output PB interrupt is disabled if bit 2 of PC is reset to 0, for input and output

8255 Mode1 operation

Mode 1 operation can be done in 2 ways: Handshake Interrupt driven I/O Handshake Status Check I/O

Handshake Interrupt driven I/O Interrupt is enabled for the port using PCBSR Processor is interrupted whenever - the input buffer is full (for i/p operation) - the o/p buffer is empty (for o/p operation)

www.bookspar.com | Website for students | VTU NOTES 58 www.bookspar.com | Website for students | VTU NOTES

Handshake Interrupt input port 8255 For Port A as handshake interrupt input port: INTA is PC3 STB*A is PC4 IBFA is PC5

PB7-0 Port B STB*B (PC2)

IBF INT B B (PC1) (PC0) Waveforms for Handshake Interrupt input port

STB*

IBF

INT RD*

Data from I/O dev. When input device has data to send it checks if IBF (input buffer full) signal is 0. If 0, it sends data on PB7-0 and activates STB* (Strobe) signal. STB* is active low. When STB* goes high, the data enters the port and IBF gets activated. If the Port interrupt is enabled, INT is activated. This interrupts the processor. Processor reads the port during the ISS. Then IBF and INT get deactivated.

Handshake interrupt output port

For Port A as handshake interrupt output port: INTA is PC3 ACK*A is PC6

www.bookspar.com | Website for students | VTU NOTES 59 www.bookspar.com | Website for students | VTU NOTES OBF*A is PC7

8255

Port B PB7-0

OBF* INT B B (PC1) (PC0)

Waveforms for Handshake interrupt output port

WR*

OBF*

INT

ACK*

When output device wants to receive data it checks if OBF* (output buffer full) signal is 0.Data If 0, sentit receives out data on PB7-0 and activates ACK* (Acknowledge) signal. ACK* is active low. When ACK* goes high, the data goes out of the port and OBF* is set to 1. If the on Port port interrupt pins is enabled, INT is activated. This interrupts the processor. Processor sends another byte to the port during the ISS. Then OBF* and INT are reset to 0.

Handshake Status Check I/O For this operation, i

www.bookspar.com | Website for students | VTU NOTES 60 www.bookspar.com | Website for students | VTU NOTES nterrupt is disabled for the port using PCBSR control word. Even if new data is entered into input buffer by I/O device INT output is not going to be activated for input operation. Then, how processor knows that the input buffer has new data?

Similarly, even if I/O device has emptied the output buffer, INT output is not going to be activated for output operation. Then, how the processor knows that the output buffer is empty?

This is solved by the p rocessor reading the status of the port for this purpose.

PC provides status information of PA and PB when they are not in Mode 0

PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

OBF* INTE IBF INTE INT INTE IBF/OBF* INT

PA status in Mode 1 PA status in mode1 PB status in Mode 1 output (along with INT) input Input or Output

PA status in Mode 2

Handshake status check input port

Suppose Port B is in mode 1 status check input. Processor reads bit 1 (IBF) of Port C repeatedly till it is set and then the processor reads Port B, as shown below.

AGAIN: IN AL, 7EH; Read Port C ROR AL, 1; ROR AL, 1; Check bit 1 of Port C JNC AGAIN; If it is 0, repeat checking IN AL, 7DH; Read from Port B

Handshake status check output port Suppose Port B is in mode 1 status check output. Processor reads bit 1 (OBF*) of Port C repeatedly till it is set and then the processor writes to Port B.

AGAIN: IN AL, 7EH; Read Port C ROR AL, 1; www.bookspar.com | Website for students | VTU NOTES 61 www.bookspar.com | Website for students | VTU NOTES ROR AL, 1; Check bit 1 of Port C JNC AGAIN; If it is 0, repeat checking MOV AL, data OUT 7DH, AL; Write to Port B

Applications of 8255 There are many applications for 8255. We discuss below only Analog to Digital conversion and Digital to Analog conversion.

Analog to Digital Conversion ADC 0808 is an 8-bit Analog to Digital Converter chip. It comes in a 28 pin DIP. It uses successive approximation technique. The conversion is quite fast. The conversion time is 100 micro seconds when the clock rate is 640 KHz. ADC 0808 has 8 analog inputs – i/p 0-7. An input is selected for conversion based on C B A inputs. Start of Conversion SOC) signal is needed to begin conversion. The end of conversion is indicated by activation of EOC signal. The digital output comes out on Out7-0

Interfacing ADC 0808

8255 ADC 0808 PA7-0 Out7-0

PC7 EOC D7-0 PC0 SOC i/p 2 PB0 A

PB1 B

PB2 C

Program for A/D Conversion

MOV AL, 98H; Configure 8255 OUT 7FH, AL; PA as input, PB as output, PCL as output, PCU as input MOV AL, 02H; Select i/p 2 as analog input OUT 7DH, AL; by sending 02 to Port B MOV AL, 00 OUT 7EH, AL; Send 0 on PC0

www.bookspar.com | Website for students | VTU NOTES 62 www.bookspar.com | Website for students | VTU NOTES MOV AL, 01 OUT 7EH, AL; Send 1 on PC0 MOV AL, 00; Send 0 on PC0 OUT 7EH, AL; i.e. send SOC on PC0

WAIT: INAL, 7EH; Read Port C ROL AL,1; Look at EOC by rotate left JNC WAIT; Remain in loop while EOC is 0

IN AL, 7CH; Read from Port A after EOC HLT

Digital to Analog Conversion

DAC 0800 is an 8-bit Digital to Analog Converter chip. It comes in a 16 pin DIP. It has 8 digital inputs. DAC 0808 generates analog current output.Current to voltage converter is used externally. Current output is generated in about 100 milli seconds.

Program for Triangular waveform generation using DAC

MOV AL, 80H; Configure Port A as output in Mode 0 OUT 7FH, AL

MOV AL, 00; Initialize AL with 0

UP: OUT 7CH, AL; Next 4 instructions generate rising portion of triangular waveform

INC AL;

CMP AL, FFH;

JB UP www.bookspar.com | Website for students | VTU NOTES 63 www.bookspar.com | Website for students | VTU NOTES

DOWN: OUT 7CH, AL; Next 4 instructions generate falling portion of triangular waveform

DEC AL;

CMP AL, 00;

JA DOWN

JMP UP; repeat generation of waveform

www.bookspar.com | Website for students | VTU NOTES 64 www.bookspar.com | Website for students | VTU NOTES String instructions

8086 has instructions that work on a character string also. The instruction mnemonics end with S.

String Instructions

MOVS CMPS STOS LODS SCAS

2-operand instructions 1-operand instructions

MOVS (MOVe String) instruction

Used for copying a string byte or word at a time. MOVSB for Move String Byte at a time. MOVSW for Move String Word at a time. MOVSB and MOVSW are more common than MOVS. Flags are not affected by the execution of MOVS/MOVSB/MOVSW instruction.

Instruction Source Destination If D = 0 If D = 1 pointed by pointed by

MOVSB DS:SI ES:DI incr. by 1 SI and DI decr. by 1 SI and DI

MOVSW DS:SI ES:DI incr. by 2 SI and DI decr. by 2 SI and DI

MOVSB is equivalent to (assuming D = 0) MOVSW is equivalent to (assuming D = 0)

MOV AL, [SI] MOV AX, [SI]

MOV ES:[DI], AL MOV ES:[DI], AX

PUSHF PUSHF

INC SI ADD SI, 2

INC DI ADD DI, 2

POPF; Flags not affected POPF; Flags not affected

www.bookspar.com | Website for students | VTU NOTES 65 www.bookspar.com | Website for students | VTU NOTES

It is usual to have REP (for REPeat) prefix for MOVSB / MOVSW instruction. The following code moves a 6-character string, as CX has 06. Without REP prefix, six MOVSB instructions are needed.

MOV CX, 06

REP MOVSB

EXIT: MOV DL, BL

Use of REP prefix with MOVSB

MOV CX, 06 MOV CX, 06

REP MOVSB JCXZ EXIT

EXIT: Next instrn. AGAIN: MOV AL, [SI]

MOV ES:[DI], AL

The above 3 instructions are PUSHF equivalent to the 10 instructions on the right INC SI (assuming D= 0) INC DI

POPF

LOOP AGAIN

EXIT: Next instrn.

CMPS (CoMPare Strings) Instruction

www.bookspar.com | Website for students | VTU NOTES 66 www.bookspar.com | Website for students | VTU NOTES CMPS Compares two strings (of equal size), say String1 and String2, a byte or word at a time. String values remain unaffected. Only flags affected. Basically it performs the subtraction DS:[SI] - ES:[DI] CMPSB for comparing Strings Byte at a time. CMPSW for comparing Strings Word at a time. CMPSB and CMPSW are more common than CMPS.

Instruction String1 String2 If D = 0 If D = 1 pointed by pointed by

CMPSB DS:SI ES:DI incr. by 1 SI and DI decr. by 1 SI and DI

CMPSW DS:SI ES:DI incr. by 2 SI and DI decr. by 2 SI and DI

CMPSB is equivalent to (assuming D = 0) CMPSW is equivalent to (assuming D = 0)

MOV AL, [SI] MOV AX, [SI]

CMP AL, ES:[DI] CMP AX, ES:[DI]

PUSHF PUSHF

INC SI ADD SI, 2

INC DI ADD DI, 2

POPF POPF

POPF used to ensure that flags are not again affected because of INC instructions

Normally CMPSB or CMPSW instructions are used to check if two given strings are same or not. To check for equality, REPE (Repeat while Equal) prefix is used.

REPE can also be written as REPZ (Repeat while Z flag is set) or REP (Repeat, ‘while equal’ is implied)

Use of REPE prefix with CMPSB

MOV CX, 08 MOV CX, 08

www.bookspar.com | Website for students | VTU NOTES 67 www.bookspar.com | Website for students | VTU NOTES REPE CMPSB JCXZ EXIT

EXIT: JE EQUAL AGAIN: MOV AL, [SI]

CMP AL, ES:[DI]

The above 3 instructions are equivalent to the PUSHF 10 instructions on the right (assuming D= 0). REPE CMPSB instruction causes CMPSB to INC SI be repeated as long as the compared bytes are equal and CX contents is not yet 0000. INC DI

POPF

LOOPE AGAIN

EXIT: JE EQUAL

REPNE (Repeat while not Equal) prefix is also present REPNE can also be written as REPNZ (Repeat while Zero flag is not set).

REPNE CMPSB causes CMPSB instruction to be repeated as long as the compared bytes are not equal and CX content is not yet 0000. REPNE prefix is not commonly used.

STOS (STOre String) instruction

STOS is used for creating a string in memory a byte or word at a time. AL/AX contents copied to memory pointed by ES:[DI]. It does not affect any flag. STOSB is used for storing string byte at a time. STOSW is used for storing string word at a time. STOSB and STOSW are more common than STOS. Flags are not affected by the execution of this instruction.

Instruction Source Destination If D = 0 If D = 1

STOSB AL ES:DI incr. DI by 1 decr. DI by 1

STOSW AX ES:DI incr. DI by 2 decr. DI by 2

www.bookspar.com | Website for students | VTU NOTES 68 www.bookspar.com | Website for students | VTU NOTES

STOSB is equivalent to (assuming D = 0) STOSW is equivalent to (assuming D = 0)

MOV ES:[DI], AL MOV ES:[DI], AX

PUSHF PUSHF

INC DI ADD DI, 2

POPF; Flags not affected POPF; Flags not affected

Suppose we want to initialize 6 consecutive memory locations with the same value 25H. The REP prefix for STOSB proves useful.

Use of REP prefix with STOSB

MOV AL, 25H

MOV CX, 06

MOV AL, 25H JCXZ EXIT

MOV CX, 06 AGAIN: MOV ES:[DI], AL

REP STOSB PUSHF

EXIT: Next instrn. INC DI

POPF Above 4 instructions are equivalent to the 9 instructions on the right (assuming D = 0) LOOP AGAIN

EXIT: Next instrn.

LODS (LOaD String) instruction www.bookspar.com | Website for students | VTU NOTES 69 www.bookspar.com | Website for students | VTU NOTES

LODS is used for processing a string in memory a byte or word at a time. It c opies contents of memory pointed by DS:[SI] into AL or AX. It does not affect any flag. LODSB is used for loading string byte at a time. LODSW is used for loading string word at a time. LODSB and LODSW are more common than LODS.

Instruction Source Destination If D = 0 If D = 1

LODSB DS: [SI] AL incr. SI by 1 decr. SI by 1

LODSW DS:[SI] AX incr. SI by 2 decr. SI by 2

LODSB is equivalent to (assuming D = 0) LODSW is equivalent to (assuming D = 0)

MOV AL, DS:[SI] MOV AX, DS:[SI]

PUSHF PUSHF

INC SI ADD SI, 2

POPF; Flags not affected POPF; Flags not affected

REP prefix for LODS has no practical value. However, no syntax error is generated by the assembler if REP prefix is used with LODSB or LODSW.

SCAS (SCAn String) instruction

SCAS is used for scanning a string in memory for a particular byte or word. It compares contents of byte in AL or word in AX with byte or word at memory pointed by ES:[DI]. SCAS performs AL/AX contents minus byte or word pointed by ES:[DI]. Operand values are not changed. Flags are affected based on result of subtraction. SCASB is used for scanning string byte at a time. SCASW is used for scanning string word at a time. SCASB and SCASW are more common than SCAS.

www.bookspar.com | Website for students | VTU NOTES 70 www.bookspar.com | Website for students | VTU NOTES Instruction Source Destination If D = 0 If D = 1

SCASB AL ES:[DI] incr. DI by 1 decr. DI by 1

SCASW AX ES:[DI] incr. DI by 2 decr. DI by 2

SCASB is equivalent to (assuming D = 0) SCASW is equivalent to (assuming D = 0)

CMP AL, ES:[DI] CMP AX, ES:[DI]

PUSHF PUSHF

INC DI ADD DI, 2

POPF POPF

Flags affected based on CMP instruction

Normally SCASB or SCASW instructions are used to check if a particular byte or word is present in the given string. In such a case, REPNE (Repeat while Not Equal) prefix is used. REPNZ (Repeat while Zero flag Not set) is same as REPNE

MOV CX, 08 MOV CX, 08

MOV AL, 35H MOV AL, 35H

REPNE SCASB JCXZ EXIT

JNE FAIL AGAIN: CMP AL, ES:[DI]

PUSHF Above 4 instructions used for Linear search are equivalent to the 9 instructions INC DI on the right (assuming D = 0) POPF

LOOPNE AGAIN

EXIT: JNE FAIL

NOTE: In case it is desired to check if all the bytes or words in a string are equal to a particular value, the REPE (Repeat while Equal) prefix is used. REPE can also be written as REPZ (Repeat while Zero flag is set) or REP.

www.bookspar.com | Website for students | VTU NOTES 71 www.bookspar.com | Website for students | VTU NOTES

www.bookspar.com | Website for students | VTU NOTES 72 www.bookspar.com | Website for students | VTU NOTES 0-Operand instructions

0-operand instructions make use of implied operands

STC Only Carry flag can be set to 1, cleared to 0, or Set Carry flag to 1 complemented

CLC Clear Carry flag to 0

CMC Complement Carry flag

CLD

Clear Direction flag to 0

STD Set direction flag to 1

CLI Clear Interrupt enable flag to 0

STI Set Interrupt enable flag to 1

There is no instruction to set or clear Trap flag !

Way to set or clear Trap flag

Trap flag position in Flags register is indicated below 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 X X X X V D IE T S Z X Ac X P X Cy

Program segment to:

Set Trap Flag to 1 Clear Trap flag to 0

PUSHF PUSHF

MOV BP, SP MOV BP, SP

www.bookspar.com | Website for students | VTU NOTES 73 www.bookspar.com | Website for students | VTU NOTES OR [BP], 0100H AND [BP], 0FEFFH

POPF POPF

DAA Instruction

DAA is identical to : ADD AL, 00H/06H/60H/66H

DAA for Decimal Adjust AL after Addition. DAA instruction execution results in addition of 00H, 06H, 60H or 66H to AL register based on the value present in AL, Carry flag, and Ac flag.

DAA instruction is very useful for performing decimal addition. Just add the decimal numbers as if they are hexadecimal numbers, and then execute DAA to get correct decimal answer !

Ex.1: Add decimal numbers 22 and 18

MOV AL, 22H ; (AL)= 22H

ADD AL, 18H ; (AL) = 3AH Illegal, incorrect answer!

DAA ; (AL) = 40H Just treat it as decimal with Cy = 0

3AH In this case, DAA same as ADD AL, 06H

+06H When LS hex digit in AL is >9, add 6 to it

=40H

Ex.2: Add decimal numbers 93 and 34

MOV AL, 93H ; (AL)= 93H

ADD AL, 34H ; (AL) = C7H, Cy=0 Illegal & Incorrect!

DAA ; (AL) = 27H Just treat it as decimal with Cy = 1

www.bookspar.com | Website for students | VTU NOTES 74 www.bookspar.com | Website for students | VTU NOTES C7H In this case, DAA same as ADD AL, 60H

+60H When MS hex digit in AL is >9, add 6 to it

=27H

Ex.3: Add decimal numbers 93 and 84

MOV AL, 93H ; (AL)= 93H

ADD AL, 84H ; (AL) = 17H, Cy = 1 Incorrect answer!

DAA ; (AL) = 77H Just treat it as decimal with Cy = 1 (carry generated?)

17H In this case, DAA same as ADD AL, 60H

+60H When Cy = 1, add 6 to MS hex digit of AL and treat

=77H Carry as 1 even though not generated in this addition

Ex.4: Add decimal numbers 65 and 57

MOV AL, 65H ; (AL)= 65H

ADD AL, 57H ; (AL) = BCH

DAA ; (AL) = 22H Just treat it as decimal with Cy = 1

BCH In this case, DAA same as ADD AL, 66H

+66H

=22H Cy = 1

Ex.5: Add decimal numbers 99 and 28

MOV AL, 99H ; (AL)= 99H

www.bookspar.com | Website for students | VTU NOTES 75 www.bookspar.com | Website for students | VTU NOTES ADD AL, 28H ; (AL) = C1H, Ac = 1

DAA ; (AL) = 27H Just treat it as decimal with Cy = 1

C1H In this case, DAA same as ADD AL, 66H

+66H 6 added to LS hex digit of AL, as Ac = 1

=27H Cy = 1 6 added to MS hex digit of AL, as it is >9

Ex.6: Add decimal numbers 36 and 42

MOV AL, 36H ; (AL)= 36H

ADD AL, 42H ; (AL) = 78H