64-Bit ELF V2 ABI Specification June 25, 2020 Revision 1.5 Prd

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Wind Rose Data Comes in the Form >200,000 Wind Rose Images

Making Wind Speed and Direction Maps Rich Stromberg Alaska Energy Authority [email protected]/907-771-3053 6/30/2011 Wind Direction Maps 1 Wind rose data comes in the form of >200,000 wind rose images across Alaska 6/30/2011 Wind Direction Maps 2 Wind rose data is quantified in very large Excel™ spreadsheets for each region of the state • Fields: X Y X_1 Y_1 FILE FREQ1 FREQ2 FREQ3 FREQ4 FREQ5 FREQ6 FREQ7 FREQ8 FREQ9 FREQ10 FREQ11 FREQ12 FREQ13 FREQ14 FREQ15 FREQ16 SPEED1 SPEED2 SPEED3 SPEED4 SPEED5 SPEED6 SPEED7 SPEED8 SPEED9 SPEED10 SPEED11 SPEED12 SPEED13 SPEED14 SPEED15 SPEED16 POWER1 POWER2 POWER3 POWER4 POWER5 POWER6 POWER7 POWER8 POWER9 POWER10 POWER11 POWER12 POWER13 POWER14 POWER15 POWER16 WEIBC1 WEIBC2 WEIBC3 WEIBC4 WEIBC5 WEIBC6 WEIBC7 WEIBC8 WEIBC9 WEIBC10 WEIBC11 WEIBC12 WEIBC13 WEIBC14 WEIBC15 WEIBC16 WEIBK1 WEIBK2 WEIBK3 WEIBK4 WEIBK5 WEIBK6 WEIBK7 WEIBK8 WEIBK9 WEIBK10 WEIBK11 WEIBK12 WEIBK13 WEIBK14 WEIBK15 WEIBK16 6/30/2011 Wind Direction Maps 3 Data set is thinned down to wind power density • Fields: X Y • POWER1 POWER2 POWER3 POWER4 POWER5 POWER6 POWER7 POWER8 POWER9 POWER10 POWER11 POWER12 POWER13 POWER14 POWER15 POWER16 • Power1 is the wind power density coming from the north (0 degrees). Power 2 is wind power from 22.5 deg.,…Power 9 is south (180 deg.), etc… 6/30/2011 Wind Direction Maps 4 Spreadsheet calculations X Y POWER1 POWER2 POWER3 POWER4 POWER5 POWER6 POWER7 POWER8 POWER9 POWER10 POWER11 POWER12 POWER13 POWER14 POWER15 POWER16 Max Wind Dir Prim 2nd Wind Dir Sec -132.7365 54.4833 0.643 0.767 1.911 4.083 -

Red Hat Enterprise Linux 6 Developer Guide

Red Hat Enterprise Linux 6 Developer Guide An introduction to application development tools in Red Hat Enterprise Linux 6 Dave Brolley William Cohen Roland Grunberg Aldy Hernandez Karsten Hopp Jakub Jelinek Developer Guide Jeff Johnston Benjamin Kosnik Aleksander Kurtakov Chris Moller Phil Muldoon Andrew Overholt Charley Wang Kent Sebastian Red Hat Enterprise Linux 6 Developer Guide An introduction to application development tools in Red Hat Enterprise Linux 6 Edition 0 Author Dave Brolley [email protected] Author William Cohen [email protected] Author Roland Grunberg [email protected] Author Aldy Hernandez [email protected] Author Karsten Hopp [email protected] Author Jakub Jelinek [email protected] Author Jeff Johnston [email protected] Author Benjamin Kosnik [email protected] Author Aleksander Kurtakov [email protected] Author Chris Moller [email protected] Author Phil Muldoon [email protected] Author Andrew Overholt [email protected] Author Charley Wang [email protected] Author Kent Sebastian [email protected] Editor Don Domingo [email protected] Editor Jacquelynn East [email protected] Copyright © 2010 Red Hat, Inc. and others. The text of and illustrations in this document are licensed by Red Hat under a Creative Commons Attribution–Share Alike 3.0 Unported license ("CC-BY-SA"). An explanation of CC-BY-SA is available at http://creativecommons.org/licenses/by-sa/3.0/. In accordance with CC-BY-SA, if you distribute this document or an adaptation of it, you must provide the URL for the original version. Red Hat, as the licensor of this document, waives the right to enforce, and agrees not to assert, Section 4d of CC-BY-SA to the fullest extent permitted by applicable law. -

Openpower AI CERN V1.Pdf

Moore’s Law Processor Technology Firmware / OS Linux Accelerator sSoftware OpenStack Storage Network ... Price/Performance POWER8 2000 2020 DRAM Memory Chips Buffer Power8: Up to 12 Cores, up to 96 Threads L1, L2, L3 + L4 Caches Up to 1 TB per socket https://www.ibm.com/blogs/syst Up to 230 GB/s sustained memory ems/power-systems- openpower-enable- bandwidth acceleration/ System System Memory Memory 115 GB/s 115 GB/s POWER8 POWER8 CPU CPU NVLink NVLink 80 GB/s 80 GB/s P100 P100 P100 P100 GPU GPU GPU GPU GPU GPU GPU GPU Memory Memory Memory Memory GPU PCIe CPU 16 GB/s System bottleneck Graphics System Memory Memory IBM aDVantage: data communication and GPU performance POWER8 + 78 ms Tesla P100+NVLink x86 baseD 170 ms GPU system ImageNet / Alexnet: Minibatch size = 128 ADD: Coherent Accelerator Processor Interface (CAPI) FPGA CAPP PCIe POWER8 Processor ...FPGAs, networking, memory... Typical I/O MoDel Flow Copy or Pin MMIO Notify Poll / Int Copy or Unpin Ret. From DD DD Call Acceleration Source Data Accelerator Completion Result Data Completion Flow with a Coherent MoDel ShareD Mem. ShareD Memory Acceleration Notify Accelerator Completion Focus on Enterprise Scale-Up Focus on Scale-Out and Enterprise Future Technology and Performance DriVen Cost and Acceleration DriVen Partner Chip POWER6 Architecture POWER7 Architecture POWER8 Architecture POWER9 Architecture POWER10 POWER8/9 2007 2008 2010 2012 2014 2016 2017 TBD 2018 - 20 2020+ POWER6 POWER6+ POWER7 POWER7+ POWER8 POWER8 P9 SO P9 SU P9 SO 2 cores 2 cores 8 cores 8 cores 12 cores w/ NVLink -

Titans and Trolls of the Open Source Arena

Titans and Trolls Enter the Open-Source Arena * by DEBRA BRUBAKER BURNS I. Introduction .................................................................................... 34 II. Legal Theories for Open Source Software License Enforcement ................................................................................... 38 A. OSS Licensing .......................................................................... 38 B. Legal Theories and Remedies for OSS Claims .................... 40 1. Legal Protections for OSS under Copyright and Contract Law ..................................................................... 40 Stronger Protections for OSS License under Copyright Law ................................................................... 40 2. Copyright-Ownership Challenges in OSS ....................... 42 3. Potential Legal Minefields for OSS under Patent Law ...................................................................................... 45 4. Added Legal Protection for OSS under Trademark Law ...................................................................................... 46 5. ITC 337 Action as Uncommon Legal Protection for OSS ..................................................................................... 49 III. Enforcement Within the OSS Community .................................. 49 A. Software Freedom Law Center Enforces OSS Licenses .... 50 B. Federal Circuit Finds OSS License Enforceable Under Copyright Law ......................................................................... 53 C. Commercial OSS -

IBM Energyscale for POWER8 Processor-Based Systems

IBM EnergyScale for POWER8 Processor-Based Systems November 2015 Martha Broyles Christopher J. Cain Todd Rosedahl Guillermo J. Silva Table of Contents Executive Overview...................................................................................................................................4 EnergyScale Features.................................................................................................................................5 Power Trending................................................................................................................................................................5 Thermal Reporting...........................................................................................................................................................5 Fixed Maximum Frequency Mode...................................................................................................................................6 Static Power Saver Mode.................................................................................................................................................6 Fixed Frequency Override...............................................................................................................................................6 Dynamic Power Saver Mode...........................................................................................................................................7 Power Management's Effect on System Performance................................................................................................7 -

IBM POWER8 High-Performance Computing Guide: IBM Power System S822LC (8335-GTB) Edition

Front cover IBM POWER8 High-Performance Computing Guide IBM Power System S822LC (8335-GTB) Edition Dino Quintero Joseph Apuzzo John Dunham Mauricio Faria de Oliveira Markus Hilger Desnes Augusto Nunes Rosario Wainer dos Santos Moschetta Alexander Pozdneev Redbooks International Technical Support Organization IBM POWER8 High-Performance Computing Guide: IBM Power System S822LC (8335-GTB) Edition May 2017 SG24-8371-00 Note: Before using this information and the product it supports, read the information in “Notices” on page ix. First Edition (May 2017) This edition applies to: IBM Platform LSF Standard 10.1.0.1 IBM XL Fortran v15.1.4 and v15.1.5 compilers IBM XLC/C++ v13.1.2 and v13.1.5 compilers IBM PE Developer Edition version 2.3 Red Hat Enterprise Linux (RHEL) 7.2 and 7.3 in little-endian mode © Copyright International Business Machines Corporation 2017. All rights reserved. Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp. Contents Notices . ix Trademarks . .x Preface . xi Authors. xi Now you can become a published author, too! . xiii Comments welcome. xiv Stay connected to IBM Redbooks . xiv Chapter 1. IBM Power System S822LC for HPC server overview . 1 1.1 IBM Power System S822LC for HPC server. 2 1.1.1 IBM POWER8 processor . 3 1.1.2 NVLink . 4 1.2 HPC system hardware components . 5 1.2.1 Login nodes . 6 1.2.2 Management nodes . 6 1.2.3 Compute nodes. 7 1.2.4 Compute racks . 7 1.2.5 High-performance interconnect. -

Safeguarding the Future of Linux Through Standards

Safeguarding the Future of Linux Through Standards “ Through the defi nition and testing of operating system interfaces, the LSB creates a stable platform that benefi ts Safeguarding Key Facts the Future of bo th developers and users.” - Linus Torvalds Linux Through Standards • The FSG is a non-profi t organization devoted to the ongoing success of Linux The Free Standards Group is an independent nonprofi t organization dedicated to accelerating the use and acceptance of free and open source • Growing membership includes all leading Linux vendors software by developing and promoting standards. Supported by leaders and many infl uential non-profi ts in the IT industry as well as the open source development community, the in the Linux community Free Standards Group fulfi lls a critical need to have common behavioral • Workgroups cover key specifi cations, tools and ABIs across Linux platforms. The Linux Standard Base Linux standards issues such as a binary standard and offers an answer to the most pressing issue facing Linux today: fragmentation. internationalization • Board members include an A well supported standard for Linux is the neccesary component to Linux’s assortment of Linux experts continued success. Without a commonly adopted standard, Linux will fragment, and senior representatives of the Linux community thus proving costly for ISVs to port their applications to the operating system and making it diffi cult for end users and Linux vendors alike. By adopting the • Headquartered in San Francisco Linux Standard Base, the Linux community provides this crucial portability so that applications can be used on more than one distribution of Linux with little or no change. -

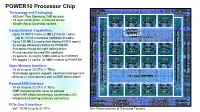

POWER10 Processor Chip

POWER10 Processor Chip Technology and Packaging: PowerAXON PowerAXON - 602mm2 7nm Samsung (18B devices) x x 3 SMT8 SMT8 SMT8 SMT8 3 - 18 layer metal stack, enhanced device 2 Core Core Core Core 2 - Single-chip or Dual-chip sockets + 2MB L2 2MB L2 2MB L2 2MB L2 + 4 4 SMP, Memory, Accel, Cluster, PCI Interconnect Cluster,Accel, Memory, SMP, Computational Capabilities: PCI Interconnect Cluster,Accel, Memory, SMP, Local 8MB - Up to 15 SMT8 Cores (2 MB L2 Cache / core) L3 region (Up to 120 simultaneous hardware threads) 64 MB L3 Hemisphere Memory Signaling (8x8 OMI) (8x8 Signaling Memory - Up to 120 MB L3 cache (low latency NUCA mgmt) OMI) (8x8 Signaling Memory - 3x energy efficiency relative to POWER9 SMT8 SMT8 SMT8 SMT8 - Enterprise thread strength optimizations Core Core Core Core - AI and security focused ISA additions 2MB L2 2MB L2 2MB L2 2MB L2 - 2x general, 4x matrix SIMD relative to POWER9 - EA-tagged L1 cache, 4x MMU relative to POWER9 SMT8 SMT8 SMT8 SMT8 Core Core Core Core Open Memory Interface: 2MB L2 2MB L2 2MB L2 2MB L2 - 16 x8 at up to 32 GT/s (1 TB/s) - Technology agnostic support: near/main/storage tiers - Minimal (< 10ns latency) add vs DDR direct attach 64 MB L3 Hemisphere PowerAXON Interface: - 16 x8 at up to 32 GT/s (1 TB/s) SMT8 SMT8 SMT8 SMT8 x Core Core Core Core x - SMP interconnect for up to 16 sockets 3 2MB L2 2MB L2 2MB L2 2MB L2 3 - OpenCAPI attach for memory, accelerators, I/O 2 2 + + - Integrated clustering (memory semantics) 4 4 PCIe Gen 5 PCIe Gen 5 PowerAXON PowerAXON PCIe Gen 5 Interface: Signaling (x16) Signaling -

Carrier Grade Linux Requirements Definition

Carrier Grade Linux Requirements Definition The Linux Foundation Version 5.0 1796 18th Street S u i t e C Prepared by the Carrier Grade Linux Working Group San Francisco CA 94107, USA Copyright (c) 2005, 2006, 2007, 2011 by The Linux +1 (415) 723 - 9 7 0 9 Foundation. This material may be distributed only subject to the terms and conditions set forth in the Open Publication License, v1.0 or later (the latest version is available at http://www.opencontent.org/opl.shtml/). Distribution of substantively modified versions of this document is prohibited without the explicit permission of the copyright holder. Linux is a Registered Trademark of Linus Torvalds. Other company, product, or service names may be the trademarks of others. CONTRIBUTORS TO THE CGL 5.0 REQUIREMENTS DEFINITION INCLUDE (IN ALPHABETICAL ORDER): Last Name First Name Company Anderson Matt HP Anderson Tim MontaVista Software Awad Majid Intel Aziz Khalid HP Badovinatz Peter IBM Bozarth Brad Cisco Cauchy Dan MontaVista Software Chacron Eric Alcatel Chen Terence Intel Cherry John OSDL Christopher Johnson Sun Microsystems Cihula Jospeh Intel Cress Andrew Intel Dague Sean IBM Dake Steven MontaVista Software Flaxa Ralf Novell Fleischer Julie Intel Fleischer Julie OSDL Fox Kevin Sun Microsystems Gross Mark Intel Haddad Ibrahim Ericsson Heber Troy HP Howell David P. Intel Hu Michael Radisys Ikebe Takashi NTT Ishitsuka Seiichi NEC Jagana Venkata IBM Johnson Christopher P. Sun Microsystems Kevin Fox Sun Microsystems Kimura Masato NTT Comware Krauska Joel Cisco Kukkonen Mika Nokia La Monte.H.P Yarrol Timesys Lavonius Ville Nokia Liu Bing Wei Intel Lynch Rusty Intel * MacDonald Joe Wind River Systems Manas Saksena Timesys Nakayama Mitsuo NEC Peter-Gonzalez Inaky Intel Pourzandi Makan Ericsson Rossi Frederic Eicsson Saksena Manas Timesys Sakuma Junichi OSDL Saskena Manas Timesys Seiler Glenn Wind River Systems Smarduch Mario Motorola Takamiya Noriaki NTT Software Weijers Gé Witham Timothy D. -

Power8 Quser Mspl Nov 2015 Handout

IBM Power Systems Power Systems Hardware: Today and Tomorrow November 2015 Mark Olson [email protected] © 2015 IBM Corporation IBM Power Systems POWER8 Chip © 2015 IBM Corporation IBM Power Systems Processor Technology Roadmap POWER11 Or whatever it is POWER10 named Or whatever it is POWER9 named Or whatever it is named POWER7 POWER8 POWER6 45 nm 22 nm POWER5 65 nm 130 nm POWER4 90 nm 180 nm 130 nm 2001 2004 2007 2010 2014 Future 3 © 2015 IBM Corporation IBM Power Systems Processor Chip Comparisons POWER5 POWER6 POWER7 POWER7+ POWER8 2004 2007 2010 2012 45nm SOI 32nm SOI 22nm SOI Technology 130nm SOI 65nm SOI eDRAM eDRAM eDRAM Compute Cores 2 2 8 8 12 Threads SMT2 SMT2 SMT4 SMT4 SMT8 Caching On-chip 1.9MB (L2) 8MB (L2) 2 + 32MB (L2+3) 2 + 80MB (L2+3) 6 + 96MB (L2+3) Off-chip 36MB (L3) 32MB (L3) None None 128MB (L4) Bandwidth Sust. Mem. 15GB/s 30GB/s 100GB/s 100GB/s 230GB/s Peak I/O 6GB/s 20GB/s 40GB/s 40GB/s 96GB/s 4 © 2015 IBM Corporation IBM Power Systems Processor Designs POWER5+ POWER6 POWER7 POWER7+ POWER8 Max cores 4 2 8 8 12 Technology 90nm 65nm 45nm 32nm 22nm Size 245 mm2 341 mm2 567 mm2 567 mm2 650 mm2 * Transistors 276 M 790 M 1.2 B 2.1 B 4.2 B * 1.9 4 - 5 3 – 4 Up to 4.4 Up to 4.1 Frequencies GHz GHz GHz GHz GHz ** SMT (threads) 2 2 4 4 8 L2 Cache 1.9MB Shared 4MB / Core 256KB / core 256KB / core 512KB/core 4MB / Core 10MB / Core 8MB / Core L3 Cache 36MB 32MB On chip On chip On chip L4 Cache -- -- -- -- Up to 128MB Bandwidth Sust memory 15GB/s 30GB/s 100GB/s 100GB/s 230GB/s Peak I/O 6GB/s 20GB/s 40GB/s 40GB/s 96GB/s * with 12-core -

IBM Power System S824L Technical Overview and Introduction

Front cover IBM Power System S824L Technical Overview and Introduction Linux server built on OpenPOWER technologies Ready for scientific, Java, and Big Data & Analytics workloads Dual NVIDIA GPU accelerators supported Alexandre Bicas Caldeira YoungHoon Cho James Cruickshank Bartłomiej Grabowski Volker Haug Andrew Laidlaw Seulgi Yoppy Sung ibm.com/redbooks Redpaper International Technical Support Organization IBM Power System S824L Technical Overview and Introduction December 2014 REDP-5139-00 Note: Before using this information and the product it supports, read the information in “Notices” on page vii. First Edition (December 2014) This edition applies to IBM Power System S824L (8247-42L) servers. © Copyright International Business Machines Corporation 2014. All rights reserved. Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp. Contents Notices . vii Trademarks . viii Preface . ix Authors. ix Now you can become a published author, too! . .x Comments welcome. xi Stay connected to IBM Redbooks . xi Chapter 1. General description . 1 1.1 Power S824L server . 2 1.2 NVIDIA Tesla GPU Accelerators. 3 1.2.1 NVIDIA CUDA. 5 1.3 Operating environment . 5 1.4 Physical package . 6 1.5 Server features . 7 1.5.1 Server features for a Power S824L with a NVIDIA GPU. 7 1.5.2 Server features for a Power S824L without a GPU. 8 1.5.3 Minimum features . 8 1.5.4 Power supply features . 8 1.5.5 Processor module features . 9 1.5.6 Memory features . 9 1.6 PCIe slots . 10 1.7 Disk and media features . -

Open Source Software: Risks and Rewards V2.0, 03 August 2005

Open Source Software: Risks and Rewards v2.0, 03 August 2005 Author(s)Gary Hein Conclusion Open source software (OSS) brings new opportunities and risks to information technology (IT) vendors and customers. Software commoditization is being profoundly affected from the infrastructure layer and moving up to the application layer. As a result, OSS is changing the strategies and business models of hardware and software vendors and system integrators. Customers should understand the risks and rewards of OSS, and should formulate strategies that bring OSS benefits to their IT departments while mitigating the business and legal risks. Synopsis Open source software (OSS) is more than just free software. It’s a development process, a distribution model, and a set of new software licenses. And, as characterized by OSS proponents, it’s a movement. OSS projects, such as Linux and Apache HTTP server, are commoditizing enterprise and Internet infrastructure, and thus pose threats for some vendors while creating new market opportunities for others. OSS brings more to information technology (IT) than just free software. It grants freedom from vendor lock-in and application churn, freedom to inspect, modify, and improve source code, and the freedom to influence or contribute to projects key to a company’s survival. But these freedoms come at a price. Although OSS is free, it isn’t always less expensive to implement due to migration, support, training, and maintenance costs. OSS projects add new twists to business risks such as vendor viability and stability, and legal issues remain uncertain as many popular licenses have yet to be tested in a court of law.