SW Test 2018 Wafer Test Technology Conference and EXPO

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2018 Hall of Fame Program

Message from the President Dear Honorees, Families, and Friends, It is my distinct pleasure to welcome you to our annual Hall of Fame Dinner and Awards Ceremony. The Hall of Fame was established to recognize those individuals and corporations who have made outstanding contributions to the excellence of Cerritos College. Thousands of students have benefited from our honorees’ leadership, dedication, and philanthropy. It is an honor to welcome these individuals and celebrate their achievements as we induct them into our highest honor, our Hall of Fame. This is a very special night for honorees, families, and friends. Thank you for attending tonight’s ceremony, and giving generously so we can help future students achieve fame! Jose Fierro, D.V.M., Ph.D. President/Superintendent Cerritos College Cerritos College President Dr. Jose Fierro and the Board of Trustees Board of Trustees Administration Zurich Lewis Dr. Jose Fierro welcome you to the President President/Superintendent 2018 Hall of Fame Dr. Shin Liu Rick Miranda Vice President Vice President of Visits The Waldorf Astoria Academic Affairs/ Martha Camacho-Rodriguez Assistant Superintendent Clerk Awards Dinner Dr. Adriana Flores-Church Carmen Avalos Vice President of a celebration of excellence and generosity Member Human Resources/ Assistant Superintendent inspired by 1940’s New York James Cody Birkey Member Felipe Lopez Vice President of Sponsored by the Cerritos College Foundation Marisa Perez Business Services/ Member Assistant Superintendent Thursday, March 8, 2018 Dr. Sandra Salazar -

Julyissuesingle.Pdf

The Independent Journal ofCreative Improvised Music cadence Vol 38 No3 JUL AUG SEP 2012 The New York City Jazz Record EXCLUSIVE CONTENT ON JAZZ & IMPROVISED MUSIC IN NEW YORK CITY COMPETITIVE & EFFECTIVE ADVERTISING: [email protected] SUBSCRIPTIONS AND GENERAL INFO: [email protected] FOLLOW US ON TWITTER: @NYCJAZZRECORD www.nycjazzrecord.com Cadence The Independent Journal of Creative Improvised Music July - August - September 2012 ABBREVIATIONS USED Vol. 38 No. 3 (401) IN CADENCE Cadence ISSN01626973 is published quarterly online acc: accordion and annually in print by as: alto sax Cadence Media LLC, bari s : baritone sax P.O. Box 282, Richland, OR 97870 b cl: bass clarinet bs: bass sax PH 315-289-1444 bsn: bassoon cel: cello Email: [email protected] cl: clarinet cga: conga www.cadencejazzmagazine.com cnt: cornet d: drums Subscriptions: 1 year: el: electric First Class USA: $65 elec: electronics Outside USA : $70 Eng hn: English horn PDF Link and Annual Print Edition: $50, Outside USA $55 euph: euphonium Coordinating Editor: David Haney flgh: flugelhorn Copy Editors: Kara D. Rusch, Jeffrey D. Todd flt: flute Transcriptions: Colin Haney, Paul Rogers, Rogers Word Fr hn: French horn Services g: guitar Art Director: Alex Haney hca: harmonica Crosswords: Ava Haney Martin kybd: keyboards Promotion and Publicity: Tiffany Rozee ldr: leader Advisory Committee: ob: oboe Jeanette Stewart org: organ Colin Haney perc: percussion Robert D. Rusch p: piano Abe Goldstein pic: piccolo rds: reeds ALL FOREIGN PAYMENTS: Visa, Mastercard, Pay Pal, and ss: soprano sax Discover accepted. sop: sopranino sax POSTMASTER: Send address change to Cadence Magazine, P.O. synth: synthesizer Box 282, Richland, OR 97870 ts: tenor sax © Copyright 2012 Cadence Magazine tbn: trombone Published by Cadence Media, LLC. -

Listening Context and Listening Mode: Towards a Unified Approach for Examining the Connection Between Music, Emotion, and Mood

Listening Context and Listening Mode: Towards a Unified Approach for Examining the Connection between Music, Emotion, and Mood. 音楽聴取の背景と様式 ―音楽、情動、気分の関係を分析するための統合的方法をめざして― DI STASIO, Michael J.* マイケル・ディスタシオ 目次 Abstract 1.Introduction 2.Organized Sound - The Elements of Music 3.Listening Diet - Music Genres 4.Exploring the Music Genre “Trichotomy” 5.Extended Listening 6.Informed Listening 7.Tracking Listening 8.Music for the Screen 9.The Music Video Experience 10.Music Live 11.Sound Engineering 12.Defining Emotion & Mood 13.The Mind of the Listener 14.The Listener Context 15.Listening Mode 16.Music & Cognitive/Perceptual Enhancement Attempts 17.Music & Physiological/Psychological Triggers 18.Discussion 19.Conclusion References * Mukogawa Womenʼs University - Visiting Academic Researcher(嘱託研究員) アンフィオンスピーカー 極東総支配人 D12430-73001689_マイケル・ディスタシオ.indd 1 2021/06/29 9:05:25 Listening context and listening mode: Towards a unified approach for examining the connection between music, emotion, and mood. MICHAEL J. DI STASIO, Mukogawa Women’s University - Visiting Academic [email protected] September 29, 2020 ABSTRACT A comprehensive investigation into music and emotion/mood research models (Eerola & Vuoskoski, 2013)1 uncovered notable shortfalls in the selection of test instruments (primacy of classical recordings); limitations of testing conditions (clinical, theoretical, or self-reporting); opportunistic choice of test participants (selected out of convenience); and research practice following historical models (scientific or sociological methodologies). This paper sought to address these issues and presented a considered approach to sourcing music stimuli; identified a wider participant cross-section and testing options; and pinpointed the need for the application of a unified, interdisciplinary research method - a model that can integrate music’s disciplines, forms, and types of engagement (ie. -

Curriculum Vitae (Resume)

CURRICULUM VITAE David Enos Education: • Bachelor of Arts-with Distinction, Music (Jazz), San Jose State University (May 1987; 53 semester units completed) • Associate in Arts, Music, Chabot College (December 1984; 133 quarter units completed); Graduated with Highest Honors • High School Diploma, Castro Valley High School (June 1982) Teaching Experience: • Applied music instructor, Citrus College, Azusa, CA (February 2010-August 2014) • Various private lesson instruction at my home studio as well as music stores January 1987-present) • Music theory, advanced re-harmonization techniques, applied music instructor, California College of Music, Pasadena, CA (January 2011-April 2012) • Music theory, performance, improvisation, composition, and applied music instructor, Pasadena International Music Academy, Pasadena, CA (January 2001- July 2007) • Music theory, music performance ensembles, improvisation, composition, and applied music instructor, Arai Music Network, Inc., San Gabriel, CA (January 2002-July 2004) • Monthly instructional staff columnist, "Bass Frontiers" magazine (November 1995-July 2000) • Jazz combo class instructor, Chabot College, Hayward, CA (summer 1987) Guest Lecturer: • Bass Clinician, Kenshu program, Citrus College, December 2010 (Azusa, CA) • Bass Master Class Clinician, Music Center Spotlight Awards, Dorothy Chandler Pavilion, January 2007 (Los Angeles, CA) • Bass Master Class Clinician, Music Center Spotlight Awards, Dorothy Chandler Pavilion, January 2003 (Los Angeles, CA) • Bass Master Class Clinician, Music Center -

Fall 2018-2019 Season Tacoma Arts Live Encore Arts Seattle

2018– 2019 New Name. Same Passion. Broadway Center for the Performing Arts is now Tacoma Arts Live. 2018–19 Season · Tacoma’s Historic Theater District Pantages Theater · Rialto Theater · Theater on the Square · Tacoma Armory My legacy. My partner. You have dreams. Goals you want to achieve during your lifetime and a legacy you want to leave behind. The Private Bank can help. Our highly specialized and experienced wealth strategists can help you navigate the complexities of estate planning and deliver the customized solutions you need to ensure your wealth is transferred according to your wishes. Take the first step in ensuring the preservation of your wealth for your lifetime and future generations. To learn more, please visit unionbank.com/theprivatebank or contact: Lisa Roberts Managing Director, Private Wealth Management [email protected] 415-705-7159 Wills, trusts, foundations, and wealth planning strategies have legal, tax, accounting, and other implications. Clients should consult a legal or tax advisor. ©2018 MUFG Union Bank, N.A. All rights reserved. Member FDIC. Union Bank is a registered trademark and brand name of MUFG Union Bank, N.A. EAP full-page template.indd 1 7/25/18 1:30 PM Welcome to the 2018–19 Season The Broadway Center is now Tacoma Arts Live! For more information on our new identity, 2018–2019 see page 7. Tacoma Arts Live’s mission: energize community through live performance. The performing arts are the pulse of the city, and radiate a vital and joyful energy while engaging in the momentum of social change. Connect and discover remarkable and transformative experiences. -

Povijesni Razvoj Trube

Povijesni razvoj trube Mutvar, Nikola Undergraduate thesis / Završni rad 2016 Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Pula / Sveučilište Jurja Dobrile u Puli Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:137:366170 Rights / Prava: In copyright Download date / Datum preuzimanja: 2021-10-03 Repository / Repozitorij: Digital Repository Juraj Dobrila University of Pula SVEUČILIŠTE JURJA DO BRILE U PULI MUZIČKA AKADEMIJA U PULI Povijesni razvoj trube Završni rad Nikola Mutvar Pula, 2016. Sveučilište Jurja Dobrile u Puli Muzička akademija u Puli Povijesni razvoj trube ___________________________________________________________________________ Završni rad Nikola Mutvar JMBAG: 030303 2627 , redoviti student Studijski smjer: Glazbena pedagogija Predmet: Poznavanje glazbala Mentor: Bashkim Shehu, prof., mr. art. Pula, 2016. 2 IZJAVA O AKADEMSKOJ ČESTITOSTI Ja, dolje potpisan Nikola Mutvar , kandidat za prvostupnika glazbene pedagogije, ovime izjavljujem da je ovaj Završni rad rezultat isključivo mojega vlastitog ra da, da se temelji na mojim istraživanjima te da se oslanja na objavljenu literaturu kao što to pokazuju korištene bilješke i bibliografija. Izjavljujem da niti jedan dio Završnog rada nije napisan na nedozvoljen način, odnosno da je prepisan iz kojega neci tiranog rada, te da ikoji dio rada krši bilo čija autorska prava. Izjavljujem, također, da nijedan dio rada nije iskorišten za koji drugi rad pri bilo kojoj drugoj visokoškolskoj, znanstvenoj ili radnoj ustanovi. Student -

Department of Music Programs 2010 - 2011 Department of Music Olivet Nazarene University

Olivet Nazarene University Digital Commons @ Olivet School of Music: Performance Programs Music 2011 Department of Music Programs 2010 - 2011 Department of Music Olivet Nazarene University Follow this and additional works at: https://digitalcommons.olivet.edu/musi_prog Part of the Fine Arts Commons, and the Music Performance Commons Recommended Citation Department of Music, "Department of Music Programs 2010 - 2011" (2011). School of Music: Performance Programs. 44. https://digitalcommons.olivet.edu/musi_prog/44 This Book is brought to you for free and open access by the Music at Digital Commons @ Olivet. It has been accepted for inclusion in School of Music: Performance Programs by an authorized administrator of Digital Commons @ Olivet. For more information, please contact [email protected]. ' "K " # * ^ Department of Music t _ , A 2010-2011 Programs A OLIVET D e p a r t m e n t d f M u s i c Gpr NAZARENE WWW.DLtVET.EDU V UNIVERSITY Calendardf Events FALL 2D 1 □ SEPTEMBER 2010 1 2 3 4 Recital: Robert H a le . 5 6 © S 9 10 11 J u l i e DAvife. O vid Yoljng 12 13 (J) 15 16 1J7 13 Kresge Auditorium 7 p .m . 1 4 Fa c u l t y R e c i t a l : A n d e r s o n /B a l l 1 9 20 2 1 22 © 24 25 K r e s g e A u d i t o r i u m 7 p . m . 26 27 23 29 30 2 3 Piano Recital: C indy R o m a n o k r e s g e A u d ito r iu m 7 P.M. -

ARTIST INDEX(Continued)

ChartARTIST Codes: CJ (Contemporary Jazz) INDEXINT (Internet) RBC (R&B/Hip-Hop Catalog) –SINGLES– DC (Dance Club Songs) LR (Latin Rhythm) RP (Rap Airplay) –ALBUMS– CL (Traditional Classical) JZ (Traditional Jazz) RBL (R&B Albums) A40 (Adult Top 40) DES (Dance/Electronic Songs) MO (Alternative) RS (Rap Songs) B200 (The Billboard 200) CX (Classical Crossover) LA (Latin Albums) RE (Reggae) AC (Adult Contemporary) H100 (Hot 100) ODS (On-Demand Songs) STS (Streaming Songs) BG (Bluegrass) EA (Dance/Electronic) LPA (Latin Pop Albums) RLP (Rap Albums) ARB (Adult R&B) HA (Hot 100 Airplay) RB (R&B Songs) TSS (Tropical Songs) BL (Blues) GA (Gospel) LRS (Latin Rhythm Albums) RMA (Regional Mexican Albums) CA (Christian AC) HD (Hot Digital Songs) RBH (R&B Hip-Hop) XAS (Holiday Airplay) JAN CA (Country) HOL (Holiday) NA (New Age) TSA (Tropical Albums) CS (Country) HSS (Hot 100 Singles Sales) RKA (Rock Airplay) XMS (Holiday Songs) CC (Christian) HS (Heatseekers) PCA (Catalog) WM (World) CST (Christian Songs) LPS (Latin Pop Songs) RMS (Regional Mexican Songs) 2 CCA (Country Catalog) IND (Independent) RBA (R&B/Hip-Hop) DA (Dance/Mix Show Airplay) LT (Hot Latin Songs) RO (Hot Rock Songs) 2021 $NOT HS 16, 24 BENEDICTINES OF MARY, QUEEN OF MARSHMELLO EA 6; AK 7; DES 14, 24; RO 7 -E- -H- TORI KELLY B200 192; HOL 46; CST 46; GS 4 APOSTLES CL 10 21 SAVAGE B200 80; RBA 28; RLP 20; H100 72; ERIC CHURCH CS 26, 33 E-40 DLP 17 HAIM CS 20; H100 97 KEM ARB 1; RBS 25 HA 35; RBH 18, 49; RP 5; RS 16 TONY BENNETT JZ 11 CIARA GS 14 EAGLES B200 148, 193; CA 21; H100 45; STM J.J. -

All-Star, All

Volume 42 • Issue 7 July/August 2014 Journal of the New Jersey Jazz Society Dedicated to the performance, promotion and preservation of jazz. The Gotham SophistiCats — Molly Ryan, Dan Levinson, Bria Skonberg, Matt Musselman and Joel Forbes — let loose at the 2nd Annual New York Hot Jazz Festival on May 18. Photo by Lynn Redmile. All-Star, All Day 2nd Annual NYC Hot Jazz Festival Sizzles New York’s burgeoning trad jazz scene, with its enclaves of young players in Brooklyn and the Lower East Side, came together for a second annual 12-hour, star-studded jazz jamboree on May 18 at The Player’s Club, the New York Hot Jazz Festival’s elegant new venue in Gramercy Park. SEE STORY ON PAGE 28 New JerseyJazzSociety in this issue: New Jersey JAzz socIety Prez Sez. 2 Bulletin Board ......................2 NJJS Calendar ......................3 Jazz Trivia .........................4 Editor’s Pick/Deadlines/NJJS Info .......6 Crow’s Nest. 50 Prez Sez New Patron Level Benefits ...........51 Change of Address/Support NJJS/ By Mike Katz President, NJJS Volunteer/Join NJJS. 51 NJJS/Pee Wee T-shirts. 52 nce again, I’ve invited our Executive V.P. Stew Saturday night to dance to the bands of Duke New/Renewed Members ............53 OSchiffer to write this Month’s “Prez Sez” Ellington, Glenn Miller, Jimmy Dorsey, Benny storIes Goodman, Sammy Kaye, Gene Krupa. Frank 2nd NYC Hot Jazz Festival. .........cover column and Stew graciously agreed. Since the Big Band in the Sky ..................8 summer is upon us, I want to wish everyone a Sinatra was a regular at the Meadowbrook with Newark Museum Jazz in Garden ......10 wonderful, safe, and fun-filled summer. -

Sunset Jazz at Newport 11 AMAZING WEDNESDAY SUMMER NIGHTS!

Sunset Jazz at Newport 11 AMAZING WEDNESDAY SUMMER NIGHTS! Wednesday, July 11 | Grand Opening Night THE JAZZ CRUISE ALL-STARS with SHELLY BERG, KEN PEPLOWSKI, JEFF HAMILTON, CHRISTOPH LUTY, RICKEY WOODARD and CHUCK REDD This series Grand Opening night has been specially designed to give jazz lovers a sampling of The Jazz Cruise, the world’s only full ship charter cruise dedicated to “straight-ahead” jazz. We are delighted to have pianist Shelly Berg, Musical Director of The Jazz Cruise, join us this year, along with Jazz Cruise veterans Ken Peplowski, Jeff Hamilton, Christoph Luty, and Rickey Woodard. Just as last year, rounding out this truly all- star group will be our special guest – Vibist Chuck Redd! Although our entire 11 week series features many jazz stars who perform on the cruise, if there is even the slightest consideration for sailing on a jazz cruise and you can only attend one Wednesday night – our Grand Opening Night is the one not to miss! Wednesday, July 18 AKIKO-HAMILTON-DECHTER Organ Trio with AKIKO TSURUGA, JEFF HAMILTON and GRAHAM DECHTER The second Wednesday night of the series is sure to be a “fasten your seatbelt” night by one of the most exciting organ trios in jazz today. Akiko began playing the organ at the age of three and launched her career in jazz immediately after graduating from the Osaka College of Music. In addition to being a crowd favorite at Jazz at Lincoln Center in New York, Akiko tours Japan and Europe regularly and has released five albums in Japan and five in the U.S., with her newest – So Cute, So Bad featuring this great trio. -

Rri J I I ( ,,, 1-¡T

SALUTES BLACK MUSIC MONTH he 0 ISSUE 1860 JUNE 14, 1991 Ilk ' r-I , J_ 7-- (111,--) ' 7- J ; rrI J I I ( ,,, 1-¡t (Celine Dion ull 1- J11 JUqB, t Uv, und NNO ¿ERG: Shari to Style www.americanradiohistory.com electronic Bernard Sumner Johnny Marr "Get the Message" The follow -up single to the smash hit "Getting Away With It" As the voice of New Order and the musical force behind The Smiths, Bernard Sumner and Johnny Marr created some of the most compelling and talked about music of the 80's. Now, Sumner and Marr join forces on a labor of love -an album all their own. U.S. Representation: Second Vision © 1991 Warner Bros. Records Inc. ¡ . { . i _ - t - www.americanradiohistory.com the GAVIN REPORT GAVIN AT A GLANCE d . ,. MOST ADDED MOST ADDED MOST ADDED NELSON ARETHA FRANKLIN ED OG AND DA BULLDOGS Only Time Will Tell (DGC) Everyday People (Arista) Bug -A -Boo (PWL American) WARRANT BE BE & CE CE WINANS EPMD Blind Faith (Columbia) Addictive Love (Capitol) Give The People (Def Jam /RAUColumbia) 'SEAL LISA LISA AND CULT JAM SLICK RICK Crazy ( Sire/Warner Bros.) Let The Beat Hit 'Em (Columbia) I Shouldn't Have Done It (Def Jam /RAUColumbia) *DESMOND CHILD Love On A Rooftop (Elektra) TO RECORD TO WATCH RECORD WATCH RETAIL PC QUEST AL B. SURE! GRAND DADDY I.U. Can I Call You My Girl? (RCA) Had Enuf? (Warner Bros.) Sugarfree (Cold Chillin' /Reprise) RADIO D.J. JAllY JEFF & THE ICE -T AMY GRANT FRESH PRINCE 0.G. Original Gangster Every Heartbeat (A &M) Summertime (Jive /RCA) (Sire/Warner Bros.) MOST ADDED MOST ADDED MOST ADDED CHER TANYA TUCKER -

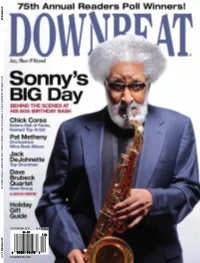

Downbeat.Com December 2010 U.K. £3.50

£3.50 £3.50 U.K. U.K. ember 2010 ember downbeat.com DEC DownBeat 75th Annual ReaDeRs Poll // sonny Rollins // ChiCk CoRea // Pat Metheny // FRed HeRsCh DeCember 2010 DECEMBER 2010 Volume 77 – Number 12 President Kevin Maher Publisher Frank Alkyer Editor Ed Enright Associate Editor Aaron Cohen Art Director Ara Tirado Production Associate Andy Williams Bookkeeper Margaret Stevens Circulation Manager Kelly Grosser AdVertisiNg Sales Record Companies & Schools Jennifer Ruban-Gentile 630-941-2030 [email protected] Musical Instruments & East Coast Schools Ritche Deraney 201-445-6260 [email protected] Classified Advertising Sales Sue Mahal 630-941-2030 [email protected] offices 102 N. Haven Road Elmhurst, IL 60126–2970 630-941-2030 Fax: 630-941-3210 http://downbeat.com [email protected] customer serVice 877-904-5299 [email protected] coNtributors Senior Contributors: Michael Bourne, John McDonough, Howard Mandel Atlanta: Jon Ross; Austin: Michael Point; Boston: Fred Bouchard, Frank-John Hadley; Chicago: John Corbett, Alain Drouot, Michael Jackson, Peter Margasak, Bill Meyer, Mitch Myers, Paul Natkin, How- ard Reich; Denver: Norman Provizer; Indiana: Mark Sheldon; Iowa: Will Smith; Los Angeles: Earl Gibson, Todd Jenkins, Kirk Silsbee, Chris Walker, Joe Woodard; Michigan: John Ephland; Minneapolis: Robin James; Nashville: Robert Doerschuk; New Orleans: Erika Goldring, David Kunian; New York: Alan Bergman, Herb Boyd, Bill Douthart, Ira Gitler, Eugene Gologursky, Norm Harris, D.D. Jackson, Jimmy Katz, Jim Macnie, Ken Micallef, Jennifer Odell,