A Nybble .On the Apple

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Apple2 Woz Sweet16info.Pdf

www.6502.org: Source: Porting Sweet 16 11/5/04 10:25 PM [Return to Main Page] Porting Sweet 16 by Carsten Strotmann ([email protected]) [Up to Source Code Repository] Sweet 16 is a metaprocessor or "pseudo microprocessor" implemented in 6502 assembly language. Originallywritten by Steve Wozniak and used in the Apple II, Sweet 16 can also be ported to other 6502-based systemsto provide useful 16-bit functionality. This article includes the source code for Sweet 16, along with a brief history,programming instructions, and notes to help port it. This material was provided by Carsten Strotmann, who has built a working Atari Port of Sweet 16. Porting Sweet 16 The Story of Sweet 16 Sweet 16 - Introduction Sweet 16: A Pseudo 16-bit Microprocessor Description Instruction Descriptions Sweet 16 Opcode Summary Register Instructions Theory of Operation When is an RTS really a JSR? Opcode Subroutines Memory Allocation User Modifications Notes from Apple II System Description Sweet 16 S-C Macro Assembler Text Programming Model Sweet 16 Opcodes Porting Sweet 16 Sweet 16 is not a teen-magazine, nor is it a brand name for candy. It is areally tricky und useful extension to a 6502 computer. It was originallywritten by Apple's Steve "Woz" Wozniak and can be found in the ROM of someAPPLE ][ Computers. Sweet 16 is a kind of virtual machine that gives the 6502programmer a 16 bit extension to the CPU. Sweet 16 creates sixteen 16-bitregisters/pointers (in zero page) and new opcodes to use this registers.Although Sweet 16 is not as fast as standard 6502 code, it can reduce the codesize of your programms and ease programming. -

Apple's Mac Team Gathers for Insanely Great Twiggy Mac Reunion

Apple's Mac team gathers for insanely great Twiggy Mac reunion SILICON BEAT By Mike Cassidy Mercury News Columnist ([email protected] / 408-920-5536 / Twitter.com/mikecassidy) POSTED: 09/12/2013 11:57:40 AM PDT MOUNTAIN VIEW -- In Silicon Valley, it's not a question of "What have you done for me lately?" -- the question is, "So, what are you going to do for me next?" And so, you have to wonder what it's like to be best known for something you did 30 years ago. Randy Wigginton, one of the freewheeling pirates who worked under Steve Jobs on Apple's (AAPL) dent-in-the-world, 1984 Macintosh, has an easy answer. "It's awesome," says Wigginton, who led the effort on the MacWrite word processor. "People don't get to change the world very often. How much luckier can a guy be? I've had a very blessed life." The blessings were very much on Wigginton's mind the other day as he and a long list of early Apple employees got together to check out the resurrection of a rare machine known as the Twiggy Mac. The prototype was a key chapter in the development of the original Mac, which of course was a key chapter in the development of the personal computer and by extension the personal music player, the smartphone, the smart tablet and a nearly ubiquitous digital lifestyle that has turned the world on its head. Some of the key players in that story, first immortalized in Steven Levy's "Insanely Great" and again in Walter Isaacson's "Steve Jobs" and most recently, docudrama fashion, in the movie "Jobs," gathered at the Computer History Museum to get a look at the Mac and at old friends who'd done so much together. -

The Apple-II, May 1977, BYTE Magazine

Photo 7: A color test chart showing the 75 shades of hue available fro m the Apple-II as presented on a typical commercial color set, using one of several RF modulators available on the mar/?et. Th e Apple BASIC program used to generate this color is shown in the text portion of this split screen (graphics and text) System Description display. Stephen Wozniak Apple Computer Co The Apple-II 20863 Stevens Creek Blvd B3-C Cupertino CA 95014 To me, a perso nal co mputer should be space for 8 K bytes of 4 K dynamic memory small, reli abl e, co nven ient to use an d in ex chips, and its shared video generation and pensive. dynami c memory refresh logi c. App le- I was Th e Apple-I, my first video oriented so ld as a completely asse mbl ed and tested single board computer, was des igned late in processor board with a price under $7 00 at 1975 and sold by word of mouth through the retail level. out California and later nationwid e through The latest result of my design activities is retail computer stores. I think that the the Apple-II which is the main subject of Apple-I co mputer was the first micropl"Oces th is system description article. The Apple-II sor system pl"Odu ct on the market to co m builds upon this idea by providing a co m pl etely integrate the display generation cir puter with more memory capability, a read cuitry, microprocessor, memory and power only memory (ROM) BASIC in terpreter, supply on the same board. -

Stories of Startups' Early Days

INTERVIEWS WITH THE FOUNDERS OF 37Signals Hotmail Adobe HotorNot Aliant Computer Hummer Winblad Apple Lycos Founders at Work Stories of Startups’ Early Days ArsDigita Marimba Blogger.com ONElist Bloglines PayPal Craigslist Research in Motion Del.icio.us Six Apart Excite Tickle Firefox TiVo Flickr TripAdvisor Fog Creek Software Viaweb Gmail WebTV Groove Networks Yahoo! Jessica Livingston 7141FM.qxd 12/18/06 11:06 AM Page i FOUNDERS AT WORK STORIES OF STARTUPS’ EARLY DAYS Jessica Livingston 7141FM.qxd 12/18/06 11:06 AM Page ii Founders at Work: Stories of Startups’ Early Days Copyright © 2007 by Jessica Livingston Lead Editor: Jim Sumser Editorial Board: Steve Anglin, Ewan Buckingham, Gary Cornell, Jason Gilmore, Jonathan Gennick, Jonathan Hassell, James Huddleston, Chris Mills, Matthew Moodie, Dominic Shakeshaft, Jim Sumser, Matt Wade Project Manager: Elizabeth Seymour Copy Edit Manager: Nicole Flores Copy Editor: Damon Larson Assistant Production Director: Kari Brooks-Copony Compositor: Dina Quan Proofreader: Linda Seifert Cover Designer: Kurt Krames Manufacturing Director: Tom Debolski Library of Congress Cataloging-in-Publication Data Livingston, Jessica. Founders at work : stories of startups’ early days / Jessica Livingston. p. cm. ISBN 1-59059-714-1 1. New business enterprises--United States--Case studies. 2. Electronic industries--United States--Case studies. I. Title. HD62.5.L59 2007 658.1'1--dc22 2006101542 All rights reserved. No part of this work may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage or retrieval system, without the prior written permission of the copyright owner and the publisher. -

Oral History of Taylor Pohlman

Oral History of Taylor Pohlman Interviewed by: David C. Brock Recorded: March 14, 2016 Mountain View, CA CHM Reference number: X7738.2016 © 2016 Computer History Museum Oral History of Taylor Pohlman David C. Brock: Well Taylor, thank you again for joining us and I thought we could begin at the beginning and just ask you about when and where you were born. Taylor Pohlman: Well born as they say at a very early age, actually back east in Fredericksburg [Virginia] and grew up around the Washington D.C. area. I went to high school there and when it came time to go to college, launched off to UT in Austin. I was convinced that nuclear fusion was the future and it was gonna happen. This was in-- what would it be, like early ‘60s right and it was gonna happen they said in about 20 years, which they say it’s still gonna happen in about 20 years. But UT at the time had imported a bunch of guys from Europe and they were working on a Tokamak I think it’s called. The torus - - twisted torus -- and so I was gonna be a physics major and I was gonna solve the problem and went to Texas and found out that I was not born to be a physicist. I couldn’t picture myself in a white lab coat. I think part of it was probably when I joined a fraternity and discovered that there were other things besides science. But the net is I wound up in math because that was the simplest major to graduate with, given all the courses I’d taken as a freshman and a sophomore and that’s what actually, historically, led me- led me into computers, sort of. -

Apple2 Woz Sweet16.Pdf

http://www.fadden.com/dl-apple2/sweet16.txt 31 October 2004 This is kind of old stuff, but I ran across the issue of Byte that had the Apple II system description by Steve Wozniak: 00 1 Return to 6502 mode 01 2 Branch Always 02 2 Branch no Carry 03 2 Branch on Carry 04 2 Branch on Positive 05 2 Branch on Negative 06 2 Branch if equal 07 2 Branch not equal 08 2 Branch on negative 1 09 2 Branch not negative 1 0A 1 Break to Monitor 0B-0F 1 No operation 1R 3 R<-2 byte constant (load register immediate) 2R 1 ACC<-R 3R 1 ACC->R 4R 1 ACC<-@R, R<-R+1 5R 1 ACC->@R, R<-R+1 6R 1 ACC<-@R double 7R 1 ACC->@R double 8R 1 R<-R-1, ACC<-@R (pop) 9R 1 R<-R-1, ACC->@R AR 1 ACC<-@R(pop) double BR 1 compare ACC to R CR 1 ACC<-ACC+R DR 1 ACC<-ACC-R ER 1 R<-R+1 FR 1 R<-R-1 notes 1. All braches are followed by a 1 byte relative displacement. Works identically to 6502 branches. 2. Only ADD,SUB, and COMPARE can set carry 3. Notation: R = a 16 bit "Register" operand designation, one of 16 labelled 0 to 15 (decimal), 0 to F (hexidecimal) ACC = register operand R0 @R = indicrect reference, using the register R as the pointer <-, -> = assignment of values 4. Length of instructions: Branches are always two bytes: opcodes followed by relative displacement. -

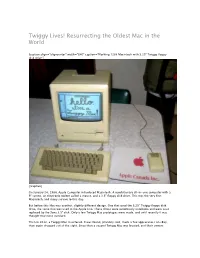

Twiggy Lives! Resurrecting the Oldest Mac in the World

Twiggy Lives! Resurrecting the Oldest Mac in the World [caption align="aligncenter" width="640" caption="Working 128k Macintosh with 5.25" Twiggy floppy disk drive"] [/caption] On January 24, 1984, Apple Computer introduced Macintosh. A revolutionary all-in-one computer with a 9" screen, an electronic rodent called a mouse, and a 3.5" floppy disk drive. This was the very first Macintosh, and many survive to this day. But before this Mac was another, slightly different design. One that used the 5.25" Twiggy floppy disk drive, the same that was used in the Apple Lisa. These drives were notoriously unreliable and were soon replaced by the Sony 3.5" disk. Only a few Twiggy Mac prototypes were made, and until recently it was thought that none survived. Then in 2012, a Twiggy Mac resurfaced. It was found, privately sold, made a few appearances on eBay, then again dropped out of the sight. Since then a second Twiggy Mac was located, and their owners embarked on an all out effort to resurrect these long lost pieces of Macintosh history. Now in 2013, with the premiere of the film Jobs, two Twiggy Macs return to life in full working glory. They are - without a doubt - The Oldest Macs in the World. Here is the story of their resurrection. The Twiggy Was Doomed, the Mac Was Not The Apple Lisa began shipping to customers in June 1983, even though there were major reliability problems with its two 5.25" Twiggy disk drives. Many of the drives didn't work and manufacturing yields were low. -

Apple Confidential 2.0 the Definitive History of the World's Most Colorful

vi Reviewers love Apple Confidential “The Apple story itself is here in all its drama.” New York Times Book Review “An excellent textbook for Apple historians.” San Francisco Chronicle “Written with humor, respect, and care, it absolutely is a must-read for every Apple fan.” InfoWorld “Pretty much irresistible is the only way to describe this quirky, highly detailed and illustrated look at the computer maker’s history.” The Business Reader Review “The book is full of basic facts anyone will appreciate. But it’s also full of interesting extras that Apple fanatics should love.” Arizona Republic “I must warn you. This 268-page book is hard to put down for a MacHead like me, and probably you too.” MacNEWS “You’ll love this book. It’s a wealth of information.” AppleInsider “Rife with gems that will appeal to Apple fanatics and followers of the computer industry.” Amazon.com “Mr. Linzmayer has managed to deliver, within the confines of a single book, just about every juicy little tidbit that was ever leaked from the company.” MacTimes “The most entertaining book about Apple yet to be published.” Booklist i …and readers love it too! “Congratulations! You should be very proud. I picked up Apple Confidential and had a hard time putting it down. Obviously, you invested a ton of time in this. I hope it zooms off the shelves.” David Lubar, Nazareth, PA “I just read Apple Confidentialfrom cover to cover…you have written a great book!” Jason Whong, Rochester, NY “There are few books out there that reveal so much about Apple and in such a fun and entertaining manner. -

Chapter 10 Apple Computer in the 1980'S

Chapter 10 Apple Computer in the 1980's As a dominant personal computer manufacturer in 1980, Apple Computer had distinct characteristics. It had developed in the Apple II and the related disk drive, technology and ease-of-use features that enabled it to make the transition from hobbyist or technical hacker user to the mass consumer market. These innovations and the release of VisiCalc spreadsheet software resulted in the commercial success of the company. It had espoused statements such as “Never build a computer you wouldn’t want to own” and “One person -- one computer.” The visit to the Xerox Palo Alto Research Center (PARC) in 1979 changed the course of product development. The new PARC human interface concepts suited the vision of Apple. It continued the innovative initiatives of Wozniak. The development of the Lisa computer and the Macintosh computer that would be the future of Apple in the 1980’s. 10.1 ... Corporate & Other Activities Public Stock Offering The initial founders Jobs, Wozniak, Markkula, Holt and the venture capitalists who provided the financing had a tight control of the Apple Computer shares. Markkula also kept a firm control on the later sale and award of Apple shares. Initial shares went through several splits that significantly increased their value. A share distributed before April 1979 was the equivalent of thirty-two shares on the day that Apple went public. During 1980 the market for new stock issues had improved. In August 1980 the Apple Computer board of directors decided to make a public offering of shares in the company. -

Steve Wozniak Interview Byte Magazine -- December 1984

_________________ Apple Computer Historical Information _________________ STEVE WOZNIAK INTERVIEW BYTE MAGAZINE -- DECEMBER 1984 http://apple2history.org/museum/articles/byte8412/byte8412.html 31 October 2004 BYTE Magazine ran a "Guide to the Apple" in December 1984. Part of that guide included the first of a two-part interview with Steve Wozniak. Here follows a reproduction of that article, reprinted with permission of Byte.com: The Apple Story, Part 1 Conducted by Gregg Williams and Rob Moore An Interview with Steve Wozniak ---------------------------------------------------------------------- Gregg Williams is a senior technical editor at BYTE. Rob Moore is a hardware designer and a frequent contributor to BYTE. They can be reached at POB 372, Hancock, NH 03449. ---------------------------------------------------------------------- Steve Wozniak is the designer of the original Apple computer and one of the cofounders of Apple Computer Inc. Here Steve speaks at length on a variety of topics that range from the hobby activities that led to his design of the Apple I to current issues at Apple Computer. His frank comments and criticisms provide a glimpse into the workings of Apple Computer from a true insiders point of view. This is the first part of a two-part article. ---------------------------------------------------------------------- Contents Pre-Apple Experiences Breakout The Apple I Apple I: RAM Apple Computer Apple Computer's name Hewlett-Packard Apple I: Specs The Apple II Apple II: Color Apple II: Text & Graphics The Apple II -

Bytecode Interpreters for Tiny Computers 10/28/08 8:17 AM

bytecode interpreters for tiny computers 10/28/08 8:17 AM bytecode interpreters for tiny computers Kragen Javier Sitaker kragen at pobox.com Fri Sep 28 04:30:05 EDT 2007 Previous message: non-chalantly paper napkin Messages sorted by: [ date ] [ thread ] [ subject ] [ author ] (I originally tried posting this in March, but it's 61K so it was rejected --- sorry about the size.) Contents -------- Introduction: Density Is King (With a Tiny VM) Indirect Threaded 16-bit FORTH: Not Great For Density Naive Lisp: Terrible For Density Lua's VM: Four-Byte Register-Based Instructions The MuP21 and F21 Instruction Sets Local Variables: Registers or Stacks? Adapting the MuP21 Instruction Set to a Smalltalk-Like System Speculative Case Study: An F21-like Squeak Steve Wozniak's SWEET 16 Dream Machine NanoVM: Java Bytecodes on the AVR Code-Compact Data Structures Library Design Other Existing Small Interpreters * S21 * Squeak? * pepsi/Albert/the golden box * The Basic STAMP * UCSD P-System * PICBIT * F-83 * Various combinator-graph-reduction machines Conclusions: Squeak Rules, We Should Be Able To Do Python In A Few K Introduction: Density Is King (With a Tiny VM) ---------------------------------------------- I've previously come to the conclusion that there's little reason for using bytecode in the modern world, except in order to get more compact code, for which it can be very effective. So, what kind of a bytecode engine will give you more compact code? Suppose I want a bytecode interpreter for a very small programming environment, specifically to minimize the memory needed for a program; say, on a 32-bit microcontroller with 40KiB of program flash, where the program flash size is very often the limiting factor on what the machine can do. -

Transcript of Steve Wozniak's Interview

The Henry Ford Collecting Innovation Today TRANSCRIPT OF A VIDEO ORAL HISTORY INTERVIEW WITH STEVE WOZNIAK CONDUCTED AUGUST 18, 2008 COMPUTER HISTORY MUSEUM, MOUNTAIN VIEW, CALIFORNIA ©The Henry Ford 2009 Interviewer: Barry Hurd Producer: Judith E. Endelman Wozniak cleanedup Final.doc MEDIA ID: WOZ1.MP3 Pg.2 MEDIA ID: WOZ1.MP3 STEVE WOZNIAK: 01:01:59;21 [We all had Segways and we] just went on and said, "Well, what could we try doin' with paddles and goals?" BARRY HURD: 01:02:04;06 Interesting. STEVE WOZNIAK: 01:02:04;11 And balls. And we figured out what kind of ball size works, how to make a paddle, then how to buy a paddle. BARRY HURD: 01:02:10;26 So this is, like, your latest invention, a new [game] STEVE WOZNIAK: 01:02:12;14 Oh, we've been doing it for years, about four years or so. BARRY HURD: 01:02:14;18 Is it catchin' on? STEVE WOZNIAK: 01:02:16;17 Yes, it is, actually. We used to have one team for quite a few years, and then there was a team in New Zealand that Wozniak cleanedup Final.doc MEDIA ID: WOZ1.MP3 Pg.3 we'd play. And now there's teams all over Europe, a bunch of places. And there's three teams in the Bay Area. BARRY HURD: 01:02:28;06 Is this like-- STEVE WOZNIAK: 01:02:28;19 But we don't really play team versus team. Usually just whoever shows up today, we'll break everybody into a bunch of teams that are about equal and we'll play for fun.