Optimize Uclinux for ARM Cortex-M4

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Atmel SMART | SAM V7: Cortex-M7 Tutorial Using the SAMV7 Xplained ULTRA Evaluation Board ARM Keil MDK 5 Toolkit Summer 2017 V 1.83 [email protected]

Atmel SMART | SAM V7: Cortex-M7 Tutorial Using the SAMV7 Xplained ULTRA evaluation board ARM Keil MDK 5 Toolkit Summer 2017 V 1.83 [email protected] Introduction: The latest version of this document is here: www.keil.com/appnotes/docs/apnt_274.asp The purpose of this lab is to introduce you to the Atmel Cortex®-M7 processor using the ARM® Keil® MDK toolkit featuring the IDE μVision®. We will demonstrate all debugging features available on this processer including Serial Wire Viewer and ETM instruction trace. At the end of this tutorial, you will be able to confidently work with these processors and Keil MDK. We recommend you obtain the new Getting Started MDK 5: from here: www.keil.com/gsg/. Keil Atmel Information Page: See www.keil.com/atmel. Keil MDK supports and has examples for most Atmel ARM processors and boards. Check the Keil Device Database® on www.keil.com/dd2 for the complete list. Additional information is listed in www.keil.com/Atmel/. Linux: Atmel ARM processors running Linux and Android are supported by ARM DS-5™. http://www.arm.com/ds5. Keil MDK-Lite™ is a free evaluation version that limits code size to 32 Kbytes. Nearly all Keil examples will compile within this 32K limit. The addition of a valid license number will turn it into a commercial version. Contact Keil Sales for details. Atmel 8051 Processors: Keil has development tools for many Atmel 8051 processors. See www.keil.com/Atmel/ for details. Atmel | Start: µVision is compatible with the Atmel | START configuration program. -

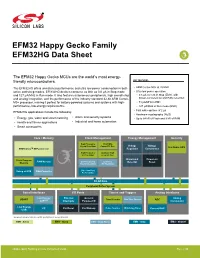

EFM32 Happy Gecko Family EFM32HG Data Sheet

EFM32 Happy Gecko Family EFM32HG Data Sheet The EFM32 Happy Gecko MCUs are the world’s most energy- friendly microcontrollers. KEY FEATURES The EFM32HG offers unmatched performance and ultra low power consumption in both • ARM Cortex-M0+ at 25 MHz active and sleep modes. EFM32HG devices consume as little as 0.6 μA in Stop mode • Ultra low power operation and 127 μA/MHz in Run mode. It also features autonomous peripherals, high overall chip • 0.6 μA current in Stop (EM3), with and analog integration, and the performance of the industry standard 32-bit ARM Cortex- brown-out detection and RAM retention M0+ processor, making it perfect for battery-powered systems and systems with high- • 51 μA/MHz in EM1 performance, low-energy requirements. • 127 μA/MHz in Run mode (EM0) • Fast wake-up time of 2 µs EFM32HG applications include the following: • Hardware cryptography (AES) • Energy, gas, water and smart metering • Alarm and security systems • Up to 64 kB of Flash and 8 kB of RAM • Health and fitness applications • Industrial and home automation • Smart accessories Core / Memory Clock Management Energy Management Security High Frequency 48/24 MHz Voltage Voltage Crystal Oscillator Comm. RC Osc. Hardware AES ARM CortexTM M0+ processor Regulator Comparator High Frequency Auxiliary High RC Oscillator Freq. RC Osc. Brown-out Power-on Flash Program RAM Memory Low Frequency Low Freq. Detector Reset Memory Crystal Oscillator RC Oscillator Debug w/ MTB DMA Controller Ultra Low Freq. RC Oscillator 32-bit bus Peripheral Reflex System Serial Interfaces I/O Ports Timers and Triggers Analog Interfaces Low Energy External General Analog USART Timer/Counter Real Time Counter ADC UARTTM Interrupts Purpose I/O Comparator Low Energy I2C Pin Reset Pin Wakeup Pulse Counter Watchdog Timer Current DAC USB Lowest power mode with peripheral operational: EM0 - Active EM1 - Sleep EM2 – Deep Sleep EM3 - Stop EM4 - Shutoff silabs.com | Building a more connected world. -

Insider's Guide STM32

The Insider’s Guide To The STM32 ARM®Based Microcontroller An Engineer’s Introduction To The STM32 Series www.hitex.com Published by Hitex (UK) Ltd. ISBN: 0-9549988 8 First Published February 2008 Hitex (UK) Ltd. Sir William Lyons Road University Of Warwick Science Park Coventry, CV4 7EZ United Kingdom Credits Author: Trevor Martin Illustrator: Sarah Latchford Editors: Michael Beach, Alison Wenlock Cover: Wolfgang Fuller Acknowledgements The author would like to thank M a t t Saunders and David Lamb of ST Microelectronics for their assistance in preparing this book. © Hitex (UK) Ltd., 21/04/2008 All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical or photocopying, recording or otherwise without the prior written permission of the Publisher. Contents Contents 1. Introduction 4 1.1 So What Is Cortex?..................................................................................... 4 1.2 A Look At The STM32 ................................................................................ 5 1.2.1 Sophistication ............................................................................................. 5 1.2.2 Safety ......................................................................................................... 6 1.2.3 Security ....................................................................................................... 6 1.2.4 Software Development .............................................................................. -

ARM Architecture

ARM Architecture Comppgzuter Organization and Assembly ygg Languages Yung-Yu Chuang with slides by Peng-Sheng Chen, Ville Pietikainen ARM history • 1983 developed by Acorn computers – To replace 6502 in BBC computers – 4-man VLSI design team – Its simp lic ity comes from the inexper ience team – Match the needs for generalized SoC for reasonable power, performance and die size – The first commercial RISC implemenation • 1990 ARM (Advanced RISC Mac hine ), owned by Acorn, Apple and VLSI ARM Ltd Design and license ARM core design but not fabricate Why ARM? • One of the most licensed and thus widespread processor cores in the world – Used in PDA, cell phones, multimedia players, handheld game console, digital TV and cameras – ARM7: GBA, iPod – ARM9: NDS, PSP, Sony Ericsson, BenQ – ARM11: Apple iPhone, Nokia N93, N800 – 90% of 32-bit embedded RISC processors till 2009 • Used especially in portable devices due to its low power consumption and reasonable performance ARM powered products ARM processors • A simple but powerful design • A whlhole filfamily of didesigns shiharing siilimilar didesign principles and a common instruction set Naming ARM •ARMxyzTDMIEJFS – x: series – y: MMU – z: cache – T: Thumb – D: debugger – M: Multiplier – I: EmbeddedICE (built-in debugger hardware) – E: Enhanced instruction – J: Jazell e (JVM) – F: Floating-point – S: SthiiblSynthesizible version (source code version for EDA tools) Popular ARM architectures •ARM7TDMI – 3 pipe line stages (ft(fetc h/deco de /execu te ) – High code density/low power consumption – One of the most used ARM-version (for low-end systems) – All ARM cores after ARM7TDMI include TDMI even if they do not include TDMI in their labels • ARM9TDMI – Compatible with ARM7 – 5 stages (fe tc h/deco de /execu te /memory /wr ite ) – Separate instruction and data cache •ARM11 ARM family comparison year 1995 1997 1999 2003 ARM is a RISC • RISC: simple but powerful instructions that execute within a single cycle at high clock speed. -

Silicon Labs to Acquire Energy Micro, a Leader in Low Power ARM Cortex-Based Microcontrollers and Radios

June 7, 2013 Silicon Labs to Acquire Energy Micro, a Leader in Low Power ARM Cortex-Based Microcontrollers and Radios Companies' Combined Portfolios Enable the Internet of Things, Smart Energy and Portable Electronics AUSTIN, Texas & OSLO, Norway--(BUSINESS WIRE)-- Silicon Labs (Nasdaq: SLAB), a leader in high-performance, analog- intensive, mixed-signal ICs, today announced that it has signed a definitive agreement to acquire Energy Micro AS. Based in Oslo, Norway, the late-stage privately held company offers the industry's most power-efficient portfolio of 32-bit microcontrollers (MCUs) and is developing multi-protocol wireless RF solutions based on the industry-leading ARM® Cortex-M architecture. Energy Micro's energy-friendly MCU and radio solutions are designed to enable a broad range of power-sensitive applications for the Internet of Things (IoT), smart energy, home automation, security and portable electronics markets. This strategic acquisition accelerates Silicon Labs' growth opportunities and positions the company as the foremost innovator in energy-friendly embedded solutions. The growth of the IoT market, coupled with continued deployment of smart grid and smart energy infrastructure, is driving strong demand for energy-efficient processing and wireless connectivity technology to enable connected devices in which low-power capabilities are increasingly important. Industry experts predict that the number of connected devices for the IoT will top 15 billion nodes by 2015 and reach 50 billion nodes by 2020. Energy Micro's portfolio complements Silicon Labs' 32-bit Precision32™ MCU, Ember® ZigBee® and sub-GHz wireless products and targets a growing embedded market. The acquisition greatly expands Silicon Labs' MCU portfolio, adding nearly 250 ARM- based EFM32 Gecko MCU products ranging from extreme-low-power, small-footprint MCUs based on the ARM Cortex-M0+ core to higher-performance, energy-friendly MCUs powered by the Cortex-M4 core capable of DSP and floating-point operations. -

Embedded Market Study, 2013

2013 EMBEDDED MARKET STUDY Essential to Engineers DATASHEETS.COM | DESIGNCON | DESIGN EAST & DESIGN WEST | EBN | EDN | EE TIMES | EMBEDDED | PLANET ANALOG | TECHONLINE | TEST & MEASUREMENT WORLD 2013 Embedded Market Study 2 UBM Tech Electronics’ Brands Unparalleled Reach & Experience UBM Tech Electronics is the media and marketing services solution for the design engineering and electronics industry. Our audience of over 2,358,928 (as of March 5, 2013) are the executives and engineers worldwide who design, develop, and commercialize technology. We provide them with the essentials they need to succeed: news and analysis, design and technology, product data, education, and fun. Copyright © 2013 by UBM. All rights reserved. 2013 Embedded Market Study 5 Purpose and Methodology • Purpose: To profile the findings of the 2013 results of EE Times Group annual comprehensive survey of the embedded systems markets worldwide. Findings include types of technology used, all aspects of the embedded development process, tools used, work environment, applications, methods and processes, operating systems used, reasons for using and not using chips and technology, and brands and chips currently used by or being considered by embedded developers. Many questions in this survey have been trended over two to five years. • Methodology: A web-based online survey instrument based on the previous year’s survey was developed and implemented by independent research company Wilson Research Group from January 18, 2013 to February 13, 2013 by email invitation • Sample: E-mail invitations were sent to subscribers to UBM/EE Times Group Embedded Brands with one reminder invitation. Each invitation included a link to the survey. • Returns: 2,098 valid respondents for an overall confidence of 95% +/- 2.13%. -

SEGGER Microcontroller Embedded Software Suite to Support Energy Micro’S Cortex-M3 Gecko Microcontrollers

Company news Reference: EM0063 SEGGER Microcontroller embedded software suite to support Energy Micro’s Cortex-M3 Gecko microcontrollers Hilden, Germany and Oslo, Norway, December 7 2011 – SEGGER Microcontroller, a leading provider of software solutions for embedded applications, and Energy Micro, the energy friendly microcontroller and radio company, have announced that SEGGER’s high-performance embedded middleware suite now supports Energy Micro’s range of ultra low energy ARM® Cortex™-M3 based EFM32 Gecko microcontrollers. The comprehensive feature-rich and high-performance software suite from SEGGER delivers an easy-to-use environment for embedded systems development, offering exceptionally low memory requirements, which minimizes Bill-of-Materials costs and enables significantly reduced power consumption overall. The middleware’s high performance also enables lower clock speed to further reduce system power consumption. Specific tools from SEGGER supporting the Energy Micro EFM32 Gecko MCUs include: the real-time operating system "embOS" which offers multitasking with minimal resources and true zero interrupt latency; the embedded file system "emFile" which is optimized for minimum RAM memory consumption supporting SD-card, NAND and NOR flash memory with wear levelling; and the efficient "emWin" user interface, an LCD controller-independent graphical user interface (GUI) for applications requiring a graphics display. The high-quality graphical software, which runs with any display or any MCU, delivers flicker-free animation, optimized drawing routines with optional anti-aliasing, and a GUI builder for Window Objects (Widgets). Thanks to the long-term partnership between the two companies, all Energy Micro development and starter kits are supplied with SEGGER’s J-Link emulation technology, and the latest Leopard and Giant Gecko development kits also include SEGGER´s advanced J-Trace. -

QSG166: WF200 Wi-Fi Development Kit Quick Start Guide

QSG166: WF200 Wi-Fi Development Kit Quick Start Guide The WF200 Wi-Fi Development Kit is an excellent way to get star- ted with WF200 Wi-Fi transceiver IC to achieve performance eval- KEY CONTENTS uation and software development. • Expansion Board with the WF200 Wi-Fi transceiver IC onboard. It supports various hardware and software use cases, as described below. • Direct connection to Silicon Labs EFM32 and EFR32 hosts (20 pin EXP) Two versions of devkits are available: • Direct connection to Raspberry Pi for the • SLEXP8022A contains WF200 development board (BRD8022A), that can be connec- Linux use case ted to Silicon Labs EFM32 or EFR32 Starter kits or to a Raspberry Pi for the Linux • Support of 3rd party MCUs case. It also contains a micro-SD card allowing fast startup with a Raspberry Pi. • Selectable SPI or SDIO host interface • SLEXP8022B is a superset of SLEXP8022A with a Raspberry Pi 2 model V1.2 inclu- ded. This document described the first steps to get a Wi-Fi connection for the Linux case (Raspberry Pi), Silicon Labs MCUs, as well as a case with a 3rd party MCU. Note: Refer to UG379 for more details about the board. silabs.com | Building a more connected world. Rev. 0.2 Table of Contents 1. Getting Started with Raspberry Pi and Linux ...................3 1.1 Requirements ..............................3 1.1.1 Hardware ..............................3 1.1.2 Software ..............................3 1.2 Hardware Setup .............................3 1.3 SSH Connection .............................4 1.4 Wi-Fi Demos...............................4 1.4.1 Station Demo .............................4 1.4.2 Access Point Demo ...........................5 1.5 Update SD Card .............................5 1.6 Software Repositories ...........................5 2. -

Μc/OS-II™ Real-Time Operating System

μC/OS-II™ Real-Time Operating System DESCRIPTION APPLICATIONS μC/OS-II is a portable, ROMable, scalable, preemptive, real-time ■ Avionics deterministic multitasking kernel for microprocessors, ■ Medical equipment/devices microcontrollers and DSPs. Offering unprecedented ease-of-use, ■ Data communications equipment μC/OS-II is delivered with complete 100% ANSI C source code and in-depth documentation. μC/OS-II runs on the largest number of ■ White goods (appliances) processor architectures, with ports available for download from the ■ Mobile Phones, PDAs, MIDs Micrium Web site. ■ Industrial controls μC/OS-II manages up to 250 application tasks. μC/OS-II includes: ■ Consumer electronics semaphores; event flags; mutual-exclusion semaphores that eliminate ■ Automotive unbounded priority inversions; message mailboxes and queues; task, time and timer management; and fixed sized memory block ■ A wide-range of embedded applications management. FEATURES μC/OS-II’s footprint can be scaled (between 5 Kbytes to 24 Kbytes) to only contain the features required for a specific application. The ■ Unprecedented ease-of-use combined with an extremely short execution time for most services provided by μC/OS-II is both learning curve enables rapid time-to-market advantage. constant and deterministic; execution times do not depend on the number of tasks running in the application. ■ Runs on the largest number of processor architectures with ports easily downloaded. A validation suite provides all documentation necessary to support the use of μC/OS-II in safety-critical systems. Specifically, μC/OS-II is ■ Scalability – Between 5 Kbytes to 24 Kbytes currently implemented in a wide array of high level of safety-critical ■ Max interrupt disable time: 200 clock cycles (typical devices, including: configuration, ARM9, no wait states). -

SEGGER — the Embedded Experts It Simply Works!

SEGGER — The Embedded Experts It simply works! Buyout licensing for Embedded Studio No license server, no hardware dongle Monheim, Germany – November 26 th, 2018 It only takes two minutes to install: With unlimited evaluaton and the freedom to use the sofware at no cost for non-commercial purposes, SEGGER has always made it easy to use Embedded Studio. In additon to this and by popular demand from developers in larger corporatons, SEGGER introduces a buyout licensing opton that makes things even easier. The new buyout opton allows usage by an unlimited number of users, without copy protecton, making it very easy to install and use the sofware anywhere: In the ofce, on the road, at customer's site or at home. No license server, no hardware dongle. Developers can fully concentrate on what they do and like best and what they are paid for: Develop sofware rather than deal with copy protecton issues. Being available for Windows, macOS and Linux, it reduces the dependencies on any third party. It is the perfect choice for mid-size to large corporatons with strict licensing policies. In additon to that, Embedded Studio's source code is available. "We are seeing more and more companies adoptng Embedded Studio as their Development Environment of choice throughout their entre organizaton. Listening to our customers, we found that this new opton helps to make Embedded Studio even more atractve. Easier is beter", says Rolf Segger, Founder of SEGGER. Get more informaton on the new SEGGER Embedded Studio at: www.segger.com/embedded-studio.html ### About Embedded Studio SEGGER — The Embedded Experts It simply works! Embedded Studio is a leading Integrated Development Environment (IDE) made by and for embedded sofware developers. -

J-Flash User Guide of the Stand-Alone Flash Programming Software

J-Flash User guide of the stand-alone flash programming software Document: UM08003 Software Version: 7.50 Date: July 1, 2021 A product of SEGGER Microcontroller GmbH www.segger.com 2 Disclaimer Specifications written in this document are believed to be accurate, but are not guaranteed to be entirely free of error. The information in this manual is subject to change for functional or performance improvements without notice. Please make sure your manual is the latest edition. While the information herein is assumed to be accurate, SEGGER Microcontroller GmbH (SEG- GER) assumes no responsibility for any errors or omissions. SEGGER makes and you receive no warranties or conditions, express, implied, statutory or in any communication with you. SEGGER specifically disclaims any implied warranty of merchantability or fitness for a particular purpose. Copyright notice You may not extract portions of this manual or modify the PDF file in any way without the prior written permission of SEGGER. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such a license. © 2004-2018 SEGGER Microcontroller GmbH, Monheim am Rhein / Germany Trademarks Names mentioned in this manual may be trademarks of their respective companies. Brand and product names are trademarks or registered trademarks of their respective holders. Contact address SEGGER Microcontroller GmbH Ecolab-Allee 5 D-40789 Monheim am Rhein Germany Tel. +49-2173-99312-0 Fax. +49-2173-99312-28 E-mail: [email protected] Internet: www.segger.com J-Flash User Guide (UM08003) © 2004-2018 SEGGER Microcontroller GmbH 3 Manual versions This manual describes the current software version. -

Developing Rust on Bare-Metal

RustyGecko - Developing Rust on Bare-Metal An experimental embedded software platform Håvard Wormdal Høiby Sondre Lefsaker Master of Science in Computer Science Submission date: June 2015 Supervisor: Magnus Lie Hetland, IDI Co-supervisor: Antonio Garcia Guirado, IDI Marius Grannæs, Silicon Labs Norwegian University of Science and Technology Department of Computer and Information Science Preface This report is submitted to the Norwegian University of Science and Technology in fulfillment of the requirements for master thesis. This work has been performed at the Department of Computer and Information Science, NTNU, with Prof. Magnus Lie Hetland as the supervisor, Antonio Garcia Guirado (ARM), and Marius Grannæs (Silicon Labs) as co-supervisors. The initial problem description was our own proposal and further developed in co-operation with our supervisors. Acknowledgements Thanks to Magnus Lie Hetland, Antonio Garcia Guirado, and Marius Grannæs for directions and guidance on technical issues and this report. Thanks to Silicon Labs for providing us with development platforms for us to develop and test our implementation on. Thanks to Antonio Garcia Guirado for the implementation of the CircleGame application for us to port to Rust and use in our benchmarks. Thanks to Itera w/Tommy Ryen for office space. A special thanks to Leslie Ho and Siri Aagedal for all the support and for proofreading the thesis. Sondre Lefsaker and H˚avard Wormdal Høiby 2015-06-14 i Project Description The Rust programming language is a new system language developed by Mozilla. With the language being statically compiled and built on the LLVM compiler infras- tructure, and because of features like low-level control and zero-cost abstractions, the language is a candidate for use in bare-metal systems.