Program Decision Logic Optimization Using Predication and Control Speculation Wen-Mei W

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

For Immediate Release

FOR IMMEDIATE RELEASE ACM - Association for Computing Machinery IEEE Computer Society Contacts: Virginia Gold Margo McCall 212-626-0505 714-816-2182 [email protected] [email protected] ACM, IEEE COMPUTER SOCIETY HONOR INNOVATOR OF HIGH-PERFORMANCE COMPUTER SYSTEMS DESIGNS University of Wisconsin’s Sohi Developed Advances Widely Adopted by Microprocessor Manufacturers to Increase the Power of Computing NEW YORK, MAY 4, 2011 -- ACM (the Association for Computing Machinery) and the IEEE Computer Society (IEEE-CS) will jointly present the Eckert-Mauchly Award to Gurindar S. (Guri) Sohi of the University of Wisconsin-Madison for pioneering widely used micro-architectural techniques in the design of high-performance microprocessors. These innovations increase the instruction-level parallelism, a measure of how many operations in a computer program can be performed simultaneously. They can be found in almost every commercial microprocessor used today in personal computers and high-end servers. The Eckert Mauchly Award http://awards.acm.org/eckert_mauchly www.computer.org/portal/web/awards/eckert is known as the computer architecture community’s most prestigious award. Sohi will receive the 2011 Eckert-Mauchly Award at the International Symposium on Computer Architecture (ISCA), held as part of the Federated Computing Research Conference (FCRC) http://www.acm.org/fcrc, June 7, 2011, in San Jose, CA. Early in his career, Sohi articulated a model for a dynamically scheduled processor supporting precise exceptions. This model has served as the basis for many commercial superscalar microprocessors that have been designed and built since the early 1990s. His group also proposed the idea of memory dependence prediction to further improve instruction-level parallelism, a technology that has been considered a key innovation in some recent microprocessors. -

Department of Computer Science

i cl i ck ! MAGAZINE click MAGAZINE 2014, VOLUME II FIVE DECADES AS A DEPARTMENT. THOUSANDS OF REMARKABLE GRADUATES. 50COUNTLESS INNOVATIONS. Department of Computer Science click! Magazine is produced twice yearly for the friends of got your CS swag? CS @ ILLINOIS to showcase the innovations of our faculty and Commemorative 50-10 Anniversary students, the accomplishments of our alumni, and to inspire our t-shirts are available! partners and peers in the field of computer science. Department Head: Editorial Board: Rob A. Rutenbar Tom Moone Colin Robertson Associate Department Heads: Rob A. Rutenbar shop now! my.cs.illinois.edu/buy Gerald DeJong Michelle Wellens Jeff Erickson David Forsyth Writers: David Cunningham CS Alumni Advisory Board: Elizabeth Innes Alex R. Bratton (BS CE ’93) Mike Koon Ira R. Cohen (BS CS ’81) Rick Kubetz Vilas S. Dhar (BS CS ’04, BS LAS BioE ’04) Leanne Lucas William M. Dunn (BS CS ‘86, MS ‘87) Tom Moone Mary Jane Irwin (MS CS ’75, PhD ’77) Michelle Rice Jennifer A. Mozen (MS CS ’97) Colin Robertson Daniel L. Peterson (BS CS ’05) Laura Schmitt Peter L. Tannenwald (BS LAS Math & CS ’85) Michelle Wellens Jill C. Zmaczinsky (BS CS ’00) Design: Contact us: SURFACE 51 [email protected] 217-333-3426 Machines take me by surprise with great frequency. Alan Turing 2 CS @ ILLINOIS Department of Computer Science College of Engineering, College of Liberal Arts & Sciences University of Illinois at Urbana-Champaign shop now! my.cs.illinois.edu/buy click i MAGAZINE 2014, VOLUME II 2 Letter from the Head 4 ALUMNI NEWS 4 Alumni -

SIGARCH FY'06 Annual Report July 2005- June 2006 Submitted By

SIGARCH FY’06 Annual Report July 2005- June 2006 Submitted by: Norm Jouppi, SIGARCH Chair Overview The primary mission of SIGARCH continues to be the forum where researchers and practitioners of computer architecture can exchange ideas. SIGARCH sponsors or cosponsors the premier conferences in the field as well as a number of workshops. It publishes a quarterly newsletter and the proceedings of several conferences. It is financially strong with a fund balance of over one million dollars. The SIGARCH bylaws are available online at http://www.acm.org/sigs/bylaws/arch_bylaws.html Officers and Directors The most recent SIGARCH election was held in the spring of 2003. Norm Jouppi of HP currently serves as SIGARCH Chair, with Margaret Martonosi of Princeton as Vice Chair and Matt Farrens of UC Davis as Secretary/Treasurer. SIGARCH has a four member Board of Directors, which currently consist of Alan Berenbaum, Joel Emer, Bill Dally, and Mark Hill. Alan Berenbaum also serves as Past Chair. In addition to these elected positions, Doug DeGroot serves as the Editor of the SIGARCH newsletter Computer Architecture News, and Doug Burger serves as Information Director, providing SIGARCH information online. The current slate of officers and directors has unanimously agreed to accept the optional 2-year term extension, as approved by the ACM SIG Governing Board Executive Committee. This means the term of the current officers and directors will expire in June 2007. Awards The Eckert-Mauchly Award, cosponsored by the IEEE Computer Society, is the most prestigious award in computer architecture. SIGARCH endows its half of the award, which is presented annually at the Awards Banquet of ISCA. -

SIGARCH Annual Report July 2009 - June 2010

SIGARCH Annual Report July 2009 - June 2010 Overview The primary mission of SIGARCH continues to be the forum where researchers and practitioners of computer architecture can exchange ideas. SIGARCH sponsors or cosponsors the premier conferences in the field as well as a number of workshops. It publishes a quarterly newsletter and the proceedings of several conferences. It is financially strong with a fund balance of over two million dollars. The SIGARCH bylaws are available online at http://www.acm.org/sigs/bylaws/arch_bylaws.html. Officers and Directors During the past fiscal year Doug Burger served as SIGARCH Chair, David Wood served as Vice Chair, and Kevin Skadron served as Secretary/Treasurer. Margaret Martonosi , Krste Asanovic, Bill Dally, and Sarita Adve served on the board of directors, and Norm Jouppi also served as Past Chair. In addition to these elected positions, Doug DeGroot continues to serve as the Editor of the SIGARCH newsletter Computer Architecture News, and Nathan Binkert was appointed as the new SIGARCH Information Director, providing SIGARCH information online. Rob Schreiber serves as SIGARCH’s liaison on the SC conference steering committee. The Eckert-Mauchly Award, cosponsored by the IEEE Computer Society, is the most prestigious award in computer architecture. SIGARCH endows its half of the award, which is presented annually at the Awards Banquet of ISCA. Bill Dally of NVidia and Stanford University received the award in 2010, "For outstanding contributions to the architecture of interconnection networks and parallel computers.” Last year, SIGARCH petitioned ACM to increase the ACM share of the award to $10,000, using an endowment taken from the SIGARCH fund balance, which ACM has approved. -

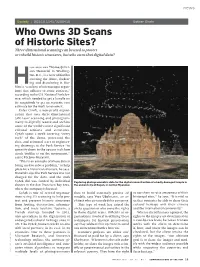

Who Owns 3D Scans of Historic Sites? Three-Dimensional Scanning Can Be Used to Protect Or Rebuild Historic Structures, but Who Owns That Digital Data?

news Society | DOI:10.1145/3290410 Esther Shein Who Owns 3D Scans of Historic Sites? Three-dimensional scanning can be used to protect or rebuild historic structures, but who owns that digital data? IGH ATOP THE Thomas Jeffer- son Memorial in Washing- ton, D.C., is a layer of biofilm covering the dome, darken- ing and discoloring it. Bio- Hfilm is “a colony of microscopic organ- isms that adheres to stone surfaces,” according to the U.S. National Park Ser- vice, which needed to get a handle on its magnitude to get an accurate cost estimate for the work to remove it. Enter CyArk, a non-profit organi- zation that uses three-dimensional (3D) laser scanning and photogram- metry to digitally record and archive some of the world’s most significant cultural artifacts and structures. CyArk spent a week covering “every inch” of the dome, processed the data, and returned a set of engineer- ing drawings to the Park Service “to quantify down to the square inch how much biofilm is on the monument,’’ says CEO John Ristevski. “This is an example of where data is being used to solve a problem,” to help preserve a historical structure, he says. Ristevski says the Park Service was not charged for the data, and the work CyArk did was funded by individual Capturing photogrammetric data for the digital reconstruction of a badly damaged temple in donors in the San Francisco Bay Area, the ancient city of Bagan, in central Myanmar. where the company is located. CyArk is one of several organiza- data to build extremely precise 3D to use them to raise awareness of their tions using 3D scanning to help pro- models, says Yves Ubelmann, an ar- historical sites,’’ he says. -

SIGARCH Annual Report July 2010 - June 2011

SIGARCH Annual Report July 2010 - June 2011 Overview The primary mission of SIGARCH continues to be the forum where researchers and practitioners of computer architecture can exchange ideas. SIGARCH sponsors or cosponsors the premier conferences in the field as well as a number of workshops. It publishes a quarterly newsletter and the proceedings of several conferences. It is financially strong with a fund balance of over two million dollars. The SIGARCH bylaws are available online at http://www.acm.org/sigs/bylaws/arch_bylaws.html. Officers and Directors During the past fiscal year Doug Burger served as SIGARCH Chair, David Wood served as Vice Chair, and Kevin Skadron served as Secretary/Treasurer. Margaret Martonosi , Krste Asanovic, Bill Dally, and Sarita Adve served on the Board of Directors, and Norm Jouppi also served as Past Chair. In addition to these elected positions, Doug DeGroot continues to serve as the Editor of the SIGARCH newsletter Computer Architecture News, and Nathan Binkert as the SIGARCH Information Director, providing SIGARCH information online. Rob Schreiber serves as SIGARCH’s liaison on the SC conference steering committee. In the spring, SIGARCH elections were held for the next term, effective July 1, 2011. The new officers are: David Wood as SIGARCH Chair, Sarita Adve as Vice Chair, Partha Ranganathan as Secretary/Treasurer, and Kai Li, Norm Jouppi, Per Stenstrom, and Scott Mahlke on the Board of Directors. Doug Burger will serve as Past Chair. Nate Binkert continues to serve as Information Director. Rob Schreiber continues to serve as SIGARCH’s liaison on the SC conference steering committee. The Eckert-Mauchly Award, cosponsored by the IEEE Computer Society, is the most prestigious award in computer architecture. -

R00456--FM Getting up to Speed

GETTING UP TO SPEED THE FUTURE OF SUPERCOMPUTING Susan L. Graham, Marc Snir, and Cynthia A. Patterson, Editors Committee on the Future of Supercomputing Computer Science and Telecommunications Board Division on Engineering and Physical Sciences THE NATIONAL ACADEMIES PRESS Washington, D.C. www.nap.edu THE NATIONAL ACADEMIES PRESS 500 Fifth Street, N.W. Washington, DC 20001 NOTICE: The project that is the subject of this report was approved by the Gov- erning Board of the National Research Council, whose members are drawn from the councils of the National Academy of Sciences, the National Academy of Engi- neering, and the Institute of Medicine. The members of the committee responsible for the report were chosen for their special competences and with regard for ap- propriate balance. Support for this project was provided by the Department of Energy under Spon- sor Award No. DE-AT01-03NA00106. Any opinions, findings, conclusions, or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of the organizations that provided support for the project. International Standard Book Number 0-309-09502-6 (Book) International Standard Book Number 0-309-54679-6 (PDF) Library of Congress Catalog Card Number 2004118086 Cover designed by Jennifer Bishop. Cover images (clockwise from top right, front to back) 1. Exploding star. Scientific Discovery through Advanced Computing (SciDAC) Center for Supernova Research, U.S. Department of Energy, Office of Science. 2. Hurricane Frances, September 5, 2004, taken by GOES-12 satellite, 1 km visible imagery. U.S. National Oceanographic and Atmospheric Administration. 3. Large-eddy simulation of a Rayleigh-Taylor instability run on the Lawrence Livermore National Laboratory MCR Linux cluster in July 2003. -

Ecocloud E-Newsletter May 2015

EcoCloud e-newsletter May 2015 In this Issue: Welcome Message In the News New Members New Projects Visiting Scholars Awards Publications Welcome Message from the Executive Committee Welcome to this edition of EcoCloud’s electronic newsletter. The EcoCloud Annual Event will be held on June 22nd and 23rd at Lausanne Palace. This year’s event features an exciting lineup of EcoCloud and industrial speakers and presenters. In this newsletter, we are also delighted to announce two additions to our Industrial Affiliate Program, a new EcoCloud faculty member expanding our research portfolio in energy management, and the latest news on our research, accomplishments and outreach. In the News Annual Event 2015 EcoCloud will hold its annual event on June 22nd and 23rd, 2015 at Lausanne Palace. The event will kick off on Monday evening with a Keynote by Raghu Ramakhrishnan on Big Data at Microsoft followed by a poster session and cocktail. The event will continue with a full day of presentations from EcoCloud researchers and industrial presentations from AXA Tech, Cloudera, IBM, Micron and Oracle. The event showcases EcoCloud’s diverse research portfolio and will cover a broad set of topics from new algorithms in machine learning to the latest cooling technologies. You can find more information on the event here. Clouds, Datacenters & the Future of IT EcoCloud’s article titled “Clouds, Datacenters & the Future of IT” appeared in L’Hebdo’s January 29th issue this year. L’Hebdo is the most widely circulated weekly magazine in the French part of Switzerland focusing on Swiss and international politics, business and current social events. -

Annual Report – 2008

SIGARCH Annual Report July 2007 - June 2008 Overview The primary mission of SIGARCH continues to be the forum where researchers and practitioners of computer architecture can exchange ideas. SIGARCH sponsors or cosponsors the premier conferences in the field as well as a number of workshops. It publishes a quarterly newsletter and the proceedings of several conferences. It is financially strong with a fund balance of over two million dollars. The SIGARCH bylaws are available online at http://www.acm.org/sigs/bylaws/arch_bylaws.html. Officers and Directors During the past fiscal year Doug Burger served as SIGARCH Chair, David Wood served as Vice Chair, and Kevin Skadron served as Secretary/Treasurer. Margaret Martonosi , Krste Asanovic, Bill Dally, and Sarita Adve served on the board of directors, and Norm Jouppi also served as Past Chair. In addition to these elected positions, Doug DeGroot continues to serve as the Editor of the SIGARCH newsletter Computer Architecture News, and Doug Burger served as temporary Information Director, providing SIGARCH information online. Rob Schreiber serves as SIGARCH’s liaison on the SC conference steering committee. At the end of the year, Nathan Binkert was appointed as the new Information Director, effective July 2008. The Eckert-Mauchly Award, cosponsored by the IEEE Computer Society, is the most prestigious award in computer architecture. SIGARCH endows its half of the award, which is presented annually at the Awards Banquet of ISCA. David Patterson of UC-Berkeley received the award in 2008, "For seminal contributions to RISC microprocessor architectures, RAID storage systems design, and reliable computing, and for leadership in education and in disseminating academic research results into successful industrial products.” This year, SIGARCH petitioned ACM to increase the ACM share of the award to $10,000, using an endowment taken from the SIGARCH fund balance. -

SIGARCH Annual Report July 2011 - June 2012

SIGARCH Annual Report July 2011 - June 2012 Overview The primary mission of SIGARCH continues to be the forum where researchers and practitioners of computer architecture can exchange ideas. SIGARCH sponsors or cosponsors the premier conferences in the field as well as a number of workshops. It publishes a quarterly newsletter and the proceedings of several conferences. It is financially strong with a fund balance of over two million dollars. The SIGARCH bylaws are available online at http://www.acm.org/sigs/bylaws/arch_bylaws.html. Officers and Directors During the past fiscal year David Wood served as SIGARCH Chair, Sarita Adve served as Vice Chair, and Partha Ranganathan served as Secretary/Treasurer. Norm Jouppi, Kai Li, Scott Mahlke, and Per Stenstrom served on the Board of Directors, and Doug Burger also served as Past Chair. In addition to these elected positions, there are three appointed positions. Doug DeGroot continues to serve as the Editor of the SIGARCH newsletter Computer Architecture News. Kevin Lim replaced Nathan Binkert as the SIGARCH Information Director, providing SIGARCH information online. Rob Schreiber served as SIGARCH’s liaison on the SC conference steering committee until May, then stepped down and was replaced by Mattan Erez. Awards The Eckert-Mauchly Award, cosponsored by the IEEE Computer Society, is the most prestigious award in computer architecture. SIGARCH endows its half of the award, which is presented annually at the Awards Banquet of ISCA. Algirdas Avizienis of the University of California, Los Angeles received the award in 2012, for “For fundamental contributions to fault-tolerant computer architecture and computer arithmetic.” In 2009, SIGARCH petitioned ACM to increase the ACM share of the award to $10,000, using an endowment taken from the SIGARCH fund balance, which ACM has approved. -

The Foundation of Modern Life

click i MAGAZINE 2015, VOLUME II THE FOUNDATION ALSO IN THIS ISSUE: OF New Engineering-Based College of Medicine 16 MODERN Illinois Funded by Google on Two Initiatives 18 LIFE. CS Welcomes Three New Faculty 32 High School Students Plunge into CS 42 Department of Computer Science click! Magazine is produced twice yearly for the friends of got your CS swag? CS @ ILLINOIS to showcase the innovations of our faculty and students, the accomplishments of our alumni, and to inspire our partners and peers in the field of computer science. Department Head: Editorial Board: Rob A. Rutenbar Tom Moone Colin Robertson shop now! my.cs.illinois.edu/buy Associate Department Heads: Rob A. Rutenbar Vikram Adve Laura Schmitt Jeff Erickson Michelle Wellens Lenny Pitt Writers: CS Alumni Advisory Board: Liz Ahlberg Alex Bratton (BS CE ’93) Katie Carr Ira Cohen (BS CS ’81) Robin Kravets Vilas S. Dhar (BS CS ’04, BS LAS BioE ’04) Rick Kubetz William M. Dunn (BS CS ‘86, MS ‘87) Tom Moone Mary Jane Irwin (MS ’75, PhD ’77) Colin Robertson Jennifer A. Mozen (MS CS ’97) Jeff Roley Daniel L. Peterson (BS ’05) Laura Schmitt Peter Tannenwald (BS LAS Math & CS ’85) Michelle Wellens Jill Zmaczinsky (BS CS ’00) Design: Contact us: SURFACE 51 [email protected] 217-333-3426 Computing is not about computers any more. It is about living. Nicholas Negroponte You can read past issues of click! magazine, as well as our monthly e-newsletter at cs.illinois.edu/news 4 CS @ ILLINOIS Department of Computer Science College of Engineering, College of Liberal Arts & Sciences University -

Margaret R. Martonosi

Margaret R. Martonosi Computer Science Bldg, Room 208 Email: [email protected] 35 Olden St. Phone: 609-258-1912 Princeton, NJ 08540 http://www.princeton.edu/~mrm Hugh Trumbull Adams ’35 Professor of Computer Science, Princeton University Assistant Director for Computer and Information Science and Engineering (CISE) at National Science Foundation. (IPA Rotator). Andrew Dickson White Visiting Professor-At-Large, Cornell University Associated faculty, Dept. of Electrical Engineering; Princeton Environmental Institute, Center for Information Technology Policy, Andlinger Center for Energy and the Environment. Research areas: Computer architectures and the hardware/software interface, particularly power-aware computing and mobile networks. HONORS IEEE Fellow. “For contributions to power-efficient computer architecture and systems design” ACM Fellow. “For contributions in power-aware computing” 2016-2022: Andrew Dickson White Visiting Professor-At-Large. Cornell University. Roughly twenty people worldwide are extended this title based on their professional stature and expertise, and are considered full members of the Cornell faculty during their six-year term appointment. 2019 SRC Aristotle Award, for graduate mentoring. 2018 IEEE Computer Society Technical Achievement Award. 2018 IEEE International Conference on High-Performance Computer Architecture Test-of-Time Paper award, honoring the long-term impact of our HPCA-5 (1999) paper entitled “Dynamically Exploiting Narrow Width Operands to Improve Processor Power and Performance” 2017 ACM SenSys Test-of-Time Paper award, honoring the long-term impact of our SenSys 2004 paper entitled “Hardware Design Experiences in ZebraNet”. 2017 ACM SIGMOBILE Test-of-Time Paper Award, honoring the long-term impact of our ASPLOS 2002 paper entitled “Energy-Efficient Computing for Wildlife Tracking: Design Tradeoffs and Early Experiences with ZebraNet”.