F13 Donkey Kong

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Unconscious Constellations Scores Superior Chhs

THE LIGHTNING BOLT CHHS EARNS BLUE RIBBON DESIGNATION UNCONSCIOUS CONSTELLATIONS SCORES SUPERIOR SPORTS ATHLETES SHARE THOUGHTS ON SEASON, FUTURE VOLUME 33 iSSUE 2 CHANCELLOR HIGH SCHOOL 6300 HARRISON ROAD, FREDERICKSBURG, VA 22407 1 November 2020 FIGHTING FOG DURING FIRE DRILL Did you know? George Washington on August 27th, 1776, used heavy fog to safely retreat from the Brit- ish during the Battle of Long Island. This pre- vented heavy casualties during a crucial point of the American War for Independence. There has been a lot of fog this fall, and October 23rd was no exception as our Chargers performed their fire drill at 8:00am. INSPIRING THOUGHTS FROM OUR FUR BABIES MASKS ARE Life Can get a NOT... DO: little Ruff... Cover Eye Masks your Hats nose and mouth fully! take some time to put Snout Holders your paws up and relax Ear Warmers STAY SAFE! Front and back cover pictures by TLB Staff Reporter Hailey Patten. Above pictures created by Kaitlyn Bestick. November 2020 2 ON GRATITUDE IN CURRENT TIMES By Cara Hadden are apathetic to the plights of at the very least, the opportu- Therefore, it might behoove Features Editor Many countries have a Word others unless a similar event nity to see each new sunrise is the downtrodden naysayers in of the Year, or a word that has happened to them. And a blessing worthy of immense this holiday season to change supposedly defines the so- yet, this kind of attitude is far gratitude. the Phrase of the Year from ciopolitical climate within from what most reasonable In summation, everyone who “Why me?” to “Thank you.” that country during that year. -

Nintendo Co., Ltd

Nintendo Co., Ltd. Financial Results Briefing for the Six-Month Period Ended September 2013 (Briefing Date: 10/31/2013) Supplementary Information [Note] Forecasts announced by Nintendo Co., Ltd. herein are prepared based on management's assumptions with information available at this time and therefore involve known and unknown risks and uncertainties. Please note such risks and uncertainties may cause the actual results to be materially different from the forecasts (earnings forecast, dividend forecast and other forecasts). Nintendo Co., Ltd. Semi-Annual Consolidated Statements of Income Transition million yen FY3/2010 FY3/2011 FY3/2012 FY3/2013 FY3/2014 Apr.-Sept.'09 Apr.-Sept.'10 Apr.-Sept.'11 Apr.-Sept.'12 Apr.-Sept.'13 Net sales 548,058 363,160 215,738 200,994 196,582 Cost of sales 341,759 214,369 183,721 156,648 134,539 Gross profit 206,298 148,791 32,016 44,346 62,042 (Gross profit ratio) (37.6%) (41.0%) (14.8%) (22.1%) (31.6%) Selling, general, and administrative expenses 101,937 94,558 89,363 73,506 85,321 Operating income 104,360 54,232 -57,346 -29,159 -23,278 (Operating income ratio) (19.0%) (14.9%) (-26.6%) (-14.5%) (-11.8%) Non-operating income 7,990 4,849 4,840 5,392 24,708 (of which foreign exchange gains) ( - ) ( - ) ( - ) ( - ) (18,360) Non-operating expenses 1,737 63,234 55,366 23,481 180 (of which foreign exchange losses) (664) (62,175) (52,433) (23,273) ( - ) Ordinary income 110,613 -4,152 -107,872 -47,248 1,248 (Ordinary income ratio) (20.2%) (-1.1%) (-50.0%) (-23.5%) (0.6%) Extraordinary income 4,311 190 50 - 1,421 Extraordinary loss 2,306 18 62 23 18 Income before income taxes and minority interests 112,618 -3,981 -107,884 -47,271 2,651 Income taxes 43,107 -1,960 -37,593 -19,330 2,065 Income before minority interests - -2,020 -70,290 -27,941 586 Minority interests in income 18 -9 -17 55 -13 Net income 69,492 -2,011 -70,273 -27,996 600 (Net income ratio) (12.7%) (-0.6%) (-32.6%) (-13.9%) (0.3%) - 1 - Nintendo Co., Ltd. -

Super Mario 64 Was Proclaimed by Many As "The Greatest Video Game

The People Behind Mario: When Hiroshi Yamauchi, president of Nintendo Co., Ltd. (NCL), hired a young art student as an apprentice in 1980, he had no idea that he was changing video games forever. That young apprentice was none other than the highly revered Shigeru Miyamoto, the man behind Mario. Miyamoto provided the inspiration for each Mario game Nintendo produces, as he still does today, with the trite exception of the unrelated “Mario-based” games produced by other companies. Just between the years 1985 and 1991, Miyamoto produced eight Mario games that went on to collectively sell 70 million copies. By record industry standards, Miyamoto had gone 70 times platinum in a brief six years. When the Nintendo chairman Gunpei Yokoi was assigned to oversee Miyamoto when he was first hired, Yokoi complained that “he knows nothing about video games” (Game Over 106). It turned out that the young apprentice knew more about video games than Yokoi, or anyone else in the world, ever could. Miyamoto’s Nintendo group, “R&D4,” had the assignment to come up with “the most imaginative video games ever” (Game Over 49), and they did just that. No one disagrees when they hear that "Shigeru is to video gaming what John Lennon is to Music!" (www.nintendoland.com) As soon as Miyamoto and Mario entered the scene, America, Japan, and the rest of the world had become totally engrossed in “Mario Mania.” Before delving deeply into the character that made Nintendo a success, we must first take a look at Nintendo, and its leader, Hiroshi Yamauchi. -

DONKEY KONG COUNTRY RETURNS Disc 1 Into the Disc Slot

INSTRUCTION BOOKLET (CONTAINS IMPORTANT HEALTH AND SAFETY INFORMATION) Any manuals provided with this software are digital reproductions of the original printed manuals. Please note that references may be made to features that can’t be used in this version of the game. There may also be references to outdated consumer information, e.g. warranties and support hotlines. For product information, please visit the Nintendo website at: www.nintendo.com For technical support and troubleshooting, please refer to the Operations Manual for your Wii U console or visit: support.nintendo.com For age rating information for this and other software, please consult the relevant website for the age rating system in your region. PEGI (Europe): www.pegi.info USK (Germany): www.usk.de Classification Operations Branch (Australia): www.classification.gov.au OFLC (New Zealand): www.classificationoffice.govt.nz Russia: minsvyaz.ru/ru/doc/index.php?id_4=883 [0610/UKV/RVL] The in-game language depends on the one that is set on your Wii console. This game includes five different language versions: English, German, French, Spanish and Italian. If your Wii console is already set to one of them, the same language will be displayed in the game. If your Wii console is set to a different language This seal is your assurance that Nintendo has than those available in the game, the in-game default language will be English. You can change the in-game reviewed this product and that it has met our language by changing the language setting of your Wii console. For further instructions about how to change language settings please refer to the Wii Operations Manual – Channels & Settings. -

The History of Nintendo: the Company, Consoles and Games

San Jose State University SJSU ScholarWorks ART 108: Introduction to Games Studies Art and Art History & Design Departments Fall 12-2020 The History of Nintendo: the Company, Consoles And Games Laurie Takeda San Jose State University Follow this and additional works at: https://scholarworks.sjsu.edu/art108 Part of the Computer Sciences Commons, and the Game Design Commons Recommended Citation Laurie Takeda. "The History of Nintendo: the Company, Consoles And Games" ART 108: Introduction to Games Studies (2020). This Final Class Paper is brought to you for free and open access by the Art and Art History & Design Departments at SJSU ScholarWorks. It has been accepted for inclusion in ART 108: Introduction to Games Studies by an authorized administrator of SJSU ScholarWorks. For more information, please contact [email protected]. The history of Nintendo: the company, consoles and games Introduction A handful of the most popular video games from Mario to The Legend of Zelda, and video game consoles from the Nintendo Entertainment System to the Nintendo Switch, were all created and developed by the same company. That company is Nintendo. From its beginning, Nintendo was not a video gaming company. Since the company’s first launch of the Nintendo Entertainment System, or NES, to the present day of the latest release of the Nintendo Switch from 2017, they have sold over 5 billion video games and over 779 million hardware units globally, according to Nintendo UK (Nintendo UK). As Nintendo continues to release new video games and consoles, they have become one of the top gaming companies, competing alongside Sony and Microsoft. -

March 2018 Spring Garden Scoop

http://basdwpweb.beth.k12.pa.us/springgarden/leader_clubs/spring-garden-scoop/ March 2018 TheSPRING GARDEN Scoop The latest information, entertainment, and opinions at Spring Garden Elementary School Ask US! St. Patrick’s Day by Caroline & Lindsey by Casey & Emma On March 17, 2018, we celebrated St. Patrick’s day! For the holiday Dear Ask Us, I want to use the slide at recess but St. Patrick’s day, there are many fun facts. For example, did you whenever I walk over to use it, there know that the four leaves of a four leaf clover have meaning? Yes, are already kids on it. Sometimes that’s right! All of the leaves have a different meaning. The they don’t notice I am waiting for a meanings of the leaves are hope, luck, love, and faith. Also, did you turn but I am too nervous to ask know that the traditional symbols for St. Patrick’s day are shamrocks, them if I can have a turn. I’m worried a leprechaun, a harp, the Celtic Cross, and the Barley Stone. if I ask them for a turn I will sound In today’s world, there are many ways to show your St. Patrick’s bossy. What should I do? day spirit! For example, many fast-food places or restaurants From, serve green or St. Patrick’s day themed milkshakes or cupcakes. Worried27 Not only that, but many people wear the color green, orange, or Dear Worried27, white to show their holiday spirit. You can ask a friend if they can walk Around the world, many kids and adults set up traps to try and up with you and help you ask if you catch a leprechaun. -

Kenya - Caucus Parliamentary Parliamentary National Assembly of Kenya National Assembly Hon

AFRICA 2019-2020 THE ICCF GROUP INTERNATIONALCONSERVATION.ORG COPYRIGHT INTERNATIONAL CONSERVATION CAUCUS FOUNDATION MISSION THE MOST ADVANCED TO ADVANCE SOLUTION IN CONSERVATION CONSERVATION GOVERNANCE BY WE BUILD POLITICAL WILL BUILDING The ICCF Group advances governments' leadership in conservation internationally by building political will POLITICAL WILL, within legislatures and supporting governments in the management of protected areas. PROVIDING ON-THE-GROUND CATALYZING CHANGE WITH KNOWLEDGE & EXPERTISE SOLUTIONS The ICCF Group supports political will by catalyzing strategic partnerships and knowledge sharing between policymakers and our extensive network. VISION TO PRESERVE THE WORLD'S MOST CRITICAL LANDSCAPES A WORLD The ICCF Group's international track record in legislative outcomes, public-private partnerships, & land WHERE management demonstrates that our unique model is emerging as a cost-effective, sustainable solution to PEOPLE AND conservation governance challenges. NATURE SUSTAIN AND NURTURE ONE ANOTHER 2019-2020 THE ICCF GROUP THE ICCF GROUP IN AFRICA EMPOWERING POLICYMAKERS &AND THE JUDICIARY The ICCF Group is working in East, Southern, and Central Africa to foster political will for conservation and support the sustainable management of natural resources. The ICCF Group has facilitated the establishment of parliamentary conservation caucuses in ten countries and is collaborating with each of these coalitions of policymakers to strengthen governance across several key natural resource sectors. The ICCF Group coordinates high-level political engagement with expertise on conservation strategies and solutions; facilitates interactions between U.S. and international policymakers, conservation organizations, and government agencies; and seeks to leverage and integrate resources in support of sustainable natural resource management policies. ICCF-supported caucuses enable, inform, and strengthen policymakers in their commitment to conservation. -

The Story of an Operetta

Vorträge und Abhandlungen zur Slavistik ∙ Band 15 (eBook - Digi20-Retro) Nicholas G. Zekulin The Story of an Operetta Le dernier sorcier by Pauline Viardot and Ivan Turgenev Vol. 1 Verlag Otto Sagner München ∙ Berlin ∙ Washington D.C. Digitalisiert im Rahmen der Kooperation mit dem DFG-Projekt „Digi20“ der Bayerischen Staatsbibliothek, München. OCR-Bearbeitung und Erstellung des eBooks durch den Verlag Otto Sagner: http://verlag.kubon-sagner.de © bei Verlag Otto Sagner. Eine Verwertung oder Weitergabe der Texte und Abbildungen, insbesondere durch Vervielfältigung, ist ohne vorherige schriftliche Genehmigung des Verlages unzulässig. «Verlag Otto Sagner» ist ein Imprint der Kubon & Sagner GmbHNicholas. G. Žekulin - 9783954794058 Downloaded from PubFactory at 01/10/2019 03:51:33AM via free access Bayerische Staatsbibliothek München ISBN 3-87690-428-5 © by Verlag Otto Sagner, München 1989. Abteilung der Firma Kubon und Sagner, Buchexport/import GmbH München Offsetdruck: Kurt Urlaub, Bamberg Nicholas G. Žekulin - 9783954794058 Downloaded from PubFactory at 01/10/2019 03:51:33AM via free access 00047504 Vorträge und Abhandlungen zur Slavistik• i • herausgegeben von Peter Thiergen (Bamberg) Band 15 1989 VERLAG OTTO SAGNER * MÜNCHEN Nicholas G. Žekulin - 9783954794058 Downloaded from PubFactory at 01/10/2019 03:51:33AM via free access Nicholas G. Žekulin - 9783954794058 Downloaded from PubFactory at 01/10/2019 03:51:33AM via free access THE STORY OF AN OPERETTA LE DERNIER SORCIER BY PAULINE VIARDOT AND IVAN TURGENEV von Nicholas G. Žekulin Nicholas G. Žekulin - 9783954794058 Downloaded from PubFactory at 01/10/2019 03:51:33AM via free access PART I BADINERIES IN BADEN-BADEN Nicholas G. Žekulin - 9783954794058 Downloaded from PubFactory at 01/10/2019 03:51:33AM via free access 00047504 For Marian, with whom so many of my musical experiences are associated. -

Intramural Sports Life Size Mario Kart Rules 2016-2017

Intramural Sports Life Size Mario Kart Rules 2016-2017 Rule 1: Racers A. 8 racers will compete in each race representing the 8 different characters in Mario Kart 64 (1 Donkey Kong, 1 Princess Peach, 1 Mario, 1 Luigi, 1 Toad, 1 Bowser, 1 Yoshi, 1 Wario) a. The amount of races and tournament format will be determined after registration closes Rule 2: Course Layout A. The first NC State Intramural Life-Size Mario Kart race will be played at the Oval on Centennial Campus based on the Mario Kart 64 Luigi Raceway found below: Rule 3: Gameplay B. A race is completed once all karts have finished 3 complete laps C. Racers will speed walk throughout the race except when they receive a power-up (Star or Mushroom) or are hit by a projectile item (Green Shell, Red Shell, Blue Shell, or Banana) a. Speed Walking – When one foot must be in contact with the ground at all times. D. There will be three tables containing Item Boxes located throughout the track where racers will have the opportunity to pick ONE up when they pass each table. E. Item Boxes will have one power-up item or projectile item underneath. a. Power-up items include and can be used accordingly: i. Mushroom – When a racer receives a mushroom they can then run to the next item box table. They can be hit by a projectile weapon during this time. ii. Star – When a racer receives a star they can run to the next item box table. They cannot be hit by a projectile weapon during this time. -

Donkey Kong Country: Tropical Freeze Is a Platform Game in Which You Control Donkey Kong on His Adventures Across Various Islands Filled with Traps and Puzzles

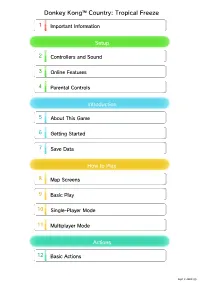

Donkey Kong™ Country: Tropical Freeze 1 Importan t Informati on Setup 2 Controll ers and Sou nd 3 Oinl ne Feusat re 4 Parent al Contro ls Idntro unctio 5 AuTbo t hiGs am e 6 Gtget in Srdta te 7 Seav Daat Hwto o Plya 8 MpSa crese n 9 Bsca i Plya 10 Sing le- Player Mode 11 Multip layer Mo de Actions 12 Basic Acstion WUP-P-ARKP-00 13 Joint Acstion 14 Mult ipl ayer Actio ns Device s and Ite ms 15 Vieh csle 16 Barrels 17 Items Lreade bsoard 18 Time Atta ck Leaderboa rds Prod uct Inform ati on 19 Copyrigh t Informati on 20 Supp ort Inform ati on 1 Importan t Informati on Thank you for selecting Donkey Kong™ Country: Tropical Freeze for Wii U™. This software is designed only for use with the European/Australian version of the Wii U console. Please read this manual carefully before using this software. If the software is to be used by young children, the manual should be read and explained to them by an adult. Before use, please also read the contents of the Health and Safety Information application on the Wii U Menu. It contains important information that will help you enjoy this software. Language Selection The in-game language depends on the one that is set on the console. This title supports five different languages: English, German, French, Spanish and Italian. If your Wii U console language is set to one of these, the same language will be displayed in the game. -

So You Th So You Think You're a Ga Ink You're a Gamer

So You Think You're A Gamer Trivia You think you know video games both new and old? Try your hand at the trivia below and see how many questions you can get right! Then try the questions out on your friends! You could also use these questions for a home trivia contest! Have fun! 1) What color is Sonic the Hedgehog? Blue 2) Who is on the cover of the video game Madden NFL 18? Tom Brady 3) What type of animal is Isabelle, the player's personal assistant in "Animal Crossing: New Leaf"? Dog 4) What is a victory known as in "Fortnite Battle Royale"? Victory Royale 5) Who is on the cover of EA Sport's "FIFA 19"? Cristiano Ronaldo 6) What is the cult in "Far Cry 5" called? Project at Eden's Gate 7) What is the title given to your character in "Mass Effect: Andromeda"? Pathfinder 8) What is the tagline for "Final Fantasy: The Spirits Within"? Unleash A New Reality 9) In "Call of Duty: Advanced Warfare", what is the name of Jack Mitchell's best friend? Will Irons 10) What video-game series is the character "Sub-Zero" from? Mortal Kombat 11) What is Pearl's signature color in "Splatoon 2"? Pink 12) What cartoon character featured in "Jurassic Park" is an unlockable character in "LEGO Jurassic World" ? Mr. DNA 13) What company developed the survival horror video game "The Last of Us Remastered"? Naughty Dog 14) What is the name of the final course in all "Mario Kart" videogames? Rainbow Road 15) Which videogame holds the record for having the highest budget ever to produce? Grand Theft Auto V 16) What are the name of the cartoon-like interludes -

MARIO VS. DONKEY KONG 2: MARCH of the MINIS Game Card

NTR-AMQP-UKV INSTRUCTION BOOKLET (CONTAINS IMPORTANT HEALTH AND SAFETY INFORMATION) [0610/UKV/NTR] THIS GAME ALLOWS WIRELESS DOWNLOAD OF THE DEMO VERSION This seal is your assurance that Nintendo has reviewed this product and that it has met our standards for excellence THIS GAME ALLOWS WIRELESS GAME FEATURE SHARING in workmanship, reliability and entertainment value. Always look for this seal when buying games and accessories to ensure complete com- patibility with your Nintendo Product. NINTENDO Wi-Fi CONNECTION THIS GAME IS DESIGNED TO USE NINTENDO Wi-Fi CONNECTION. Thank you for selecting the MARIO VS. DONKEY KONG 2™: MARCH OF THE MINIS Game Card for the Nintendo DS™ system. IMPORTANT: Please carefully read the important health and safety information included in this booklet before using your Nintendo DS system, Game Card, Game Pak or accessory. Please read this Instruction Booklet thoroughly to ensure maximum enjoyment of your new game. Important warranty and hotline information can be found in the separate Age Rating, Software Warranty and Contact Information Leaflet. Always save these documents for future reference. This Game Card will work only with Nintendo DS systems. IMPORTANT: The use of an unlawful device with your Nintendo DS system may render this game unplayable. © 2006 – 2007 NINTENDO. DEVELOPED BY NINTENDO SOFTWARE TECHNOLOGY CORPORATION. ALL RIGHTS, INCLUDING THE COPYRIGHTS OF GAME, SCENARIO, MUSIC AND PROGRAM, RESERVED BY NINTENDO. TM, ® AND THE NINTENDO DS LOGO ARE TRADEMARKS OF NINTENDO. © 2007 NINTENDO. This product uses the LC Font by Sharp Corporation. LCFONT, LC Font and the LC logo mark are trademarks of Sharp Corporation.