Innovative Technology Elements for Large and Small Pixel CIS Devices

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Photo Bites the Canon Digicam Was Bought on a Digicams and Viewfinders Small Budget

The CameraHobby Newsletter Issue 2, Fall 2012 [email protected] Introduction The Milestone Photo A couple of readers indicated that they In the last newsletter, I discussed a found the newsletter format more milestone photo shoot for my workplace informative than the old website blog- to celebrate our 25th anniversary. The style posts. shoot had been postponed many times from April to August, but we finally I’m not so sure that’s really the case. managed to get it done on August 1. With the blog, talking about a new camera, such as the Canon 5D3, would We had sun and we had a decent be done over several days or weeks with turnout from a workforce of about 250 multiple posts, and that breaks up the people (about 130 people). Although we continuity. were missing many due to summer vacations, many others didn't bother to In the newsletter, you get almost all the come out, such as it is in a largish pieces in one shot. It’s just a different organization with many personalities. presentation, because how I write is the same, loose way I did with the website I got to the Vancouver Gallery several – personal use, experience and minutes early to setup and wait for the sometimes (often?) too much subjective group to assemble. I wanted to be there opinion. early to stake out the ideal vantage point at the top of the stairs to look One reader suggested that if I’m willing down at the plaza where everyone to write 25-pages for a newsletter, I would gather. -

FOR IMMEDIATE RELEASE Press Contacts: MWW Geoff Coalter E: [email protected] Alex Kruse E: [email protected] P: 212-704-9727 Press.Nikonusa.Com

FOR IMMEDIATE RELEASE Press Contacts: MWW Geoff Coalter E: [email protected] Alex Kruse E: [email protected] P: 212-704-9727 press.nikonusa.com MASTER YOUR PERSPECTIVE WITH OPTICAL EXCELLENCE: NIKON ADDS TWO PRO-GRADE FX-FORMAT LENSES TO CELEBRATED NIKKOR LENS LINEUP Extraordinary Next-Generation AF-S NIKKOR 70-200mm f/2.8E FL ED VR Sets a New Standard for Pro Telephoto Workhorse Lenses, While New PC NIKKOR 19mm f/4E ED is Nikon’s Widest Ever Tilt-Shift NIKKOR Offering MELVILLE, NY (October 19, 2016 at 12:01 A.M. EDT) – Today, Nikon Inc. has announced two exciting FX- format additions to the storied NIKKOR lens lineup, designed to achieve amazing optical performance for the most demanding professional and enthusiast photographers. An evolution of one of Nikon’s most versatile and popular pro-zoom lenses, the newly redesigned AF-S NIKKOR 70-200mm f/2.8E FL ED VR sports an updated optical formula capable of amazing image quality, while optimized for high-speed shooting. Also introduced today is Nikon’s widest perspective control lens to date, the PC NIKKOR 19mm f/4E ED tilt-shift lens, which helps photographers effortlessly control perspective when capturing architecture, interiors, fine art, product photography and landscapes. “Nikon continues to raise the bar of optical excellence, and our newest FX-format NIKKOR offerings provide experienced photographers with powerful tools to help ensure brilliantly sharp images, whether capturing a high-speed photo finish or creatively framing an architectural marvel,” said Kosuke Kawaura, Director of -

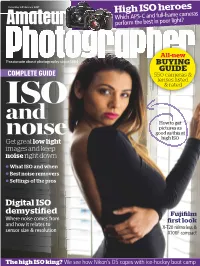

High ISO Heroes Which APS-C and Full-Frame Cameras Perform the Best in Poor Light?

Saturday 4 February 2017 High ISO heroes Which APS-C and full-frame cameras perform the best in poor light? All-new Passionate about photography since 1884 BUYING GUIDE COMPLETE GUIDE 550 cameras & lenses listed ISO & rated and How to get pictures as good as this at high ISO Get great low light images and keep noise right down ● What ISO and when ● Best noise removers ● Settings of the pros Digital ISO demystified Fujifilm Where noise comes from first look and how it relates to X-T20 mirrorless & sensor size & resolution X100F compact The high ISO king? We see how Nikon’s D5 copes with ice-hockey boot camp Ice on the black sand beach at Jökulsárlón.raw ON THE ICE BEACH IT’S A DARK, SOMBRE WINTER’S DAY. The grey cloud is low, and the rain is steady, but the muted light is just perfect for the subject matter all around me, namely waves lapping around the artfully sculpted blocks of ice on the black sand. Now I’ve seen many images of this unique combination before – it’s an Icelandic photographic staple – but there’s no resisting the appeal of such stark, elemental beauty. In fact it’s a beauty that is enhanced by the flat lighting, a cold scene of black and blue with simple graphic appeal. But as so often is the case here in Iceland the conditions are difficult: apart from the rain, salty spray is being driven inshore off the waves and onto my increasingly crusty camera, lens and filter. So be it, such adversity is now familiar. -

![Picture Control Utility 2 Help] Displays This Help](https://docslib.b-cdn.net/cover/0399/picture-control-utility-2-help-displays-this-help-2130399.webp)

Picture Control Utility 2 Help] Displays This Help

Home Ver2.2.0-1 Home Basic Operations of Picture Control Utility 2 What You Can Do with Picture Control Utility 2 Basic Operations of the Picture Control Utility 2 Windows Using Palettes Using Preview Images Quitting Picture Control Utility 2 Detailed Operations of Picture Control Utility 2 Creating/Editing Custom Picture Control About Level Adjustment About Custom Curve Editing Preview Images Importing Custom Picture Control Exporting Custom Picture Control Deleting Custom Picture Control Changing the Names and Comments of Custom Picture Controls Preferences of Picture Control Utility 2 Menu List of Picture Control Utility 2 file:///E|/...81yJIRA%91%CE%89%9E%8C%E3_%8D%C4%94[%95i%81zU1320_160201/EN/sitemap.html[2016/02/04 14:00:45] Basic Operations of Picture Control Utility 2 Home > Basic Operations of Picture Control Utility 2 Basic Operations of Picture Control Utility 2 What You Can Do with Picture Control Utility 2 This section provides a brief introduction to what you can do with Picture Control Utility 2. Basic Operations of the Picture Control Utility 2 Windows This section provides an introduction to the basic windows and operations of Picture Control Utility 2. file:///E|/...yJIRA%91%CE%89%9E%8C%E3_%8D%C4%94[%95i%81zU1320_160201/EN/pc001000.html[2016/02/04 14:00:53] What You Can Do with Picture Control Utility 2 Home > Basic Operations of Picture Control Utility 2 > What You Can Do with Picture Control Utility 2 What You Can Do with Picture Control Utility 2 With Picture Control Utility 2, which can be installed as a standalone application for easy operation, you can perform the actions described below. -

Kerrisdale Cameras: Used List

KERRISDALE CAMERAS This used list is used by our staff internally and we post it weekly on our website, usually on Mondays and Thursdays. To Note: Descriptions are abbreviated because they are from our 'back-office' inventory system and meant for internal-use and therefore not fully "user-friendly". Items shown here were in stock on the morning of the report's date. Contact us to check current availability as items may have sold since this report was run. The item in stock may only be available in one of our seven stores. In most cases, we can transfer an item to any of our stores within one to three business days. Items marked "reserve" may be on hold. Please contact us to check availability. Item marked with two asterisks ** indicate that it is an item that regularly comes into stock and may have more than one in stock available. Also, many new items are required to be held for a month before we can sell them, as required by some municipalities' bylaws. These items are included here. We can accept deposits to hold an item for you until the police allow us to release it for sale. Contact Us: For more product information, to order, to find out which store the item is in, to request a transfer to another store, or to confirm stock availability, please call us at 604-263-3221 or toll-free at 1-866-310-3245 or email us: [email protected] Report Date: 06/03/2019 Date: 06/03/2019 Web Used List Time: 08:33 Department Description : DIGITAL CAMERA BATTERIES used Department Name : DCB Product Product Retail Code Name Price 449.QC NIMH -

Accessories Brochure

Painting with light Fast-moving subjects captured against a blaze of background color: add Speedlights to a scene, and you can achieve a whole lot more in your images. Dare to see the world differently. © Dave Black All the subtlety, all the drama In atmospheric settings, flash photography heightens the beauty of the moment. Radio communication makes even elaborate lighting set-ups feel effortless, allowing your creativity to take control. © Dave Black 4 5 Control the light. Expand the possibilities. Photography is all about working And it just got even better. with light. Take control of the The new SB-5000 Speedlight light, and everything changes. marks the dawn of an Drab settings become instantly exciting new phase for CLS, dramatic. A seemingly mundane and for flash photography moment turns into something in general. For the first unforgettable. time, it’s possible to control For photographers, working with Speedlights via radio waves, flash can be a liberating experience. It’s a way of unlocking the enabling reliable communication over far greater distances (up full potential of the scene in front of you — of bending, or even to 30 m/100 ft), and without having to worry about physical rewriting, the rules. With a few Nikon Speedlights in your bag, obstacles. you’ll have a wealth of creative options at your disposal every With the power to control up to 6 groups of Speedlights time you shoot. at once, even the most ambitious lighting designs are now Portable and highly adaptable, Speedlights let you devise feasible. What’s more, enhanced high-speed sync accuracy and imaginative, multi-angle lighting setups with minimal hassle. -

North Texas PC News

North Texas PC News 3RD SATURDAY SIGS MEET AT King of Glory Lutheran Church www.ntpcug.org 6411 Lyndon B. Johnson Freeway Dallas, Texas June 2012 Prez Sez VOLUME 32 • NUMBER 7 by Bill Drissel [email protected] In this Issue.... At http://blog.mozilla.org/blog/2012/05/22/introducing-mozilla- Prez Sez ..........................1 webmaker, you will find Mozilla’s introduction to Mozilla Web- maker - a toolset that Mozilla hopes will make everyone into a Special Interest programmer. Mozilla writes, “We’re kicking off Mozilla Webmaker Groups (SIGs) .................2 with something special: a massive summer learning campaign. It’s called the Summer Code Party (https://webmaker.org/events), News from the will run all summer long, and kicks off June 23.” Northwest.........................6 They plan to furnish tools and sample projects. They hope to Advertising Rates ..........10 form local communities with events, meet-ups and coding ses- sions all over. “Summer camps, day camps, summer schools, Tips and Tricks – Digital public libraries, recreation centers, neighborhood groups, your Photography .................11 kitchen table — anyone with a willingness to make, learn and engage using the open building blocks of the web.” NTPCUG Member Websites ........................18 The website opened on June 6th, and there is already one event scheduled in Dallas, on June 30th at 8:00 pm. See the NTPCUG Monthly link below for details: Flyer ...............................19 LEARN WEBNOW at https://donate.mozilla.org/page/event/ detail/kitchentable/w5k. Volunteering ...................19 --------------------------------------------------------------------------- 2012 NTPCUG Elected If you are interested in the weather, there is a marvelous dis- Officials .........................20 play of tornado tracks available, with severity emphasized. -

Kerrisdale Cameras: Used List

KERRISDALE CAMERAS This used list is used by our staff internally. We post it on Mondays and Thursdays. This may result in some items appearing as available when they have been sold between these two periods. For more accurate information please contact us using the information provided below. Report Date: 7/23/20 To Note: Descriptions are abbreviated because they are from our 'back-office' inventory system and meant for internal-use and therefore not fully "user-friendly". Items shown here were in stock on the morning of the report's date. Contact us to check current availability as items may have sold since this report was run. The item in stock may only be available in one of our seven stores. In most cases, we can transfer an item to any of our stores within one to three business days. Items marked "reserve" may be on hold. Please contact us to check availability. Item marked with two asterisks ** indicate that it is an item that regularly comes into stock and may have more than one in stock available. Also, many new items are required to be held for a month before we can sell them, as required by some municipalities' bylaws. These items are included here. We can accept deposits to hold an item for you until the police allow us to release it for sale. Contact Us: For more product information, to order, to find out which store the item is in, to request a transfer to another store, or to confirm stock availability, please call us at 604-263-3221 or toll-free at 1-866-310-3245 or email us: [email protected] Date: 07/23/2020 -

Nikon Expands Its Popular Nikon 1 System with the Addition of the New Nikon 1 J2 Camera and 1 Nikkor 11-27.5Mm F/3.5-5.6 Lens

FOR IMMEDIATE RELEASE Press Contacts: MWW Group Geoff Coalter E: [email protected] Matt Kopacz E: [email protected] P: 201.507.9500 press.nikonusa.com NIKON EXPANDS ITS POPULAR NIKON 1 SYSTEM WITH THE ADDITION OF THE NEW NIKON 1 J2 CAMERA AND 1 NIKKOR 11-27.5MM F/3.5-5.6 LENS Nikon’s Dedication to the Growing Nikon 1 System Provides Users with Even More Creative Freedom and Outlets for Self Expression MELVILLE, N.Y. (August 9, 2012) – Today, Nikon Inc. announced the expansion of the popular Nikon 1 Advanced Camera with Interchangeable Lens System with the addition of the Nikon 1 J2 camera and the 1 NIKKOR 11-27.5mm f/3.5-5.6 lens to provide users with amazing image quality and stunning 1080p HD video in a portable, powerful package. The Nikon 1 System, including the new Nikon 1 J2 and the 1 NIKKOR 11-27.5mm lens, is engineered from the ground up to give users the freedom to capture and connect with others to share life experiences. The Nikon 1 J2 improves upon the Nikon 1 J1 with new features such as a Creative Mode that provides a variety of photo effects to users, a metallic body, a higher resolution LCD screen and the addition of stylish new color offerings. Made for those seeking portability without compromising stunning image quality and quick performance, the J2 is the camera designed to empower users to capture their world like never before with stunning and sharp image and HD video quality. In addition to the camera, the 11- 27.5mm lens is a super-compact zoom lens that offers a helpful 2.5x zoom range in an easily pocketable size. -

Book V Camera

b bb bbbera bbbbon.com bbbb Basic Photography in 180 Days Book V - Camera Editor: Ramon F. aeroramon.com Contents 1 Day 1 1 1.1 Camera ................................................ 1 1.1.1 Functional description ..................................... 2 1.1.2 History ............................................ 2 1.1.3 Mechanics ........................................... 5 1.1.4 Formats ............................................ 8 1.1.5 Camera accessories ...................................... 8 1.1.6 Camera design history .................................... 8 1.1.7 Image gallery ......................................... 12 1.1.8 See also ............................................ 14 1.1.9 References .......................................... 15 1.1.10 Bibliography ......................................... 16 1.1.11 External links ......................................... 17 2 Day 2 18 2.1 Camera obscura ............................................ 18 2.1.1 Physical explanation ...................................... 19 2.1.2 Technology .......................................... 19 2.1.3 History ............................................ 20 2.1.4 Role in the modern age .................................... 31 2.1.5 Examples ........................................... 32 2.1.6 Public access ......................................... 33 2.1.7 See also ............................................ 33 2.1.8 Notes ............................................. 34 2.1.9 References .......................................... 34 2.1.10 Sources -

Kerrisdale Cameras: Used List

KERRISDALE CAMERAS This used list is used by our staff internally. We post it on Mondays and Thursdays. This may result in some items appearing as available when they have been sold between these two periods. For more accurate information please contact us using the information provided below. Report Date: 04/20/2020 To Note: Descriptions are abbreviated because they are from our 'back-office' inventory system and meant for internal-use and therefore not fully "user-friendly". Items shown here were in stock on the morning of the report's date. Contact us to check current availability as items may have sold since this report was run. The item in stock may only be available in one of our seven stores. In most cases, we can transfer an item to any of our stores within one to three business days. Items marked "reserve" may be on hold. Please contact us to check availability. Item marked with two asterisks ** indicate that it is an item that regularly comes into stock and may have more than one in stock available. Also, many new items are required to be held for a month before we can sell them, as required by some municipalities' bylaws. These items are included here. We can accept deposits to hold an item for you until the police allow us to release it for sale. Contact Us: For more product information, to order, to find out which store the item is in, to request a transfer to another store, or to confirm stock availability, please call us at 604-263-3221 or toll-free at 1-866-310-3245 or email us: [email protected] Date: 04/20/2020 -

I Am Full of Possibilities

I AM FULL OF POSSIBILITIES I AM THE NIKON TOTAL DIGITAL IMAGING SYSTEMS www.nikon-asia.com The Nikon Total Digital Imaging System: Let your imagination be your guide Nikon is proud to bring you its latest incarnation of the Nikon Total Digital Imaging System, full of photographic excitement, answers and inspiration. Within these pages you will find everything you need to realize your present ideas and inspire new ones. Whether you are a seasoned professional or a passionate weekend shooter, we are confident that the contents of this brochure can help you craft better images. Every item is designed specifically to work with Nikon cameras, which means a seamless performance that truly brings out the best in you and your Nikon D-SLR. Got an idea? Make it happen. Here’s where you start. TABLE OF CONTENTS n Why more light? pp4-5 n See what just one Speedlight can do pp6-7 n Magnify your potential with multiple Speedlights pp8-9 n Many features, unlimited possibilities pp10-11 n The Nikon Creative Lighting System: Lineup pp12-14 n The Nikon Creative Lighting System: Compatibility p15 n Battery packs, batteries, battery chargers and AC adapters pp16-17 n GPS accessories p17 n Wireless transmission accessories p18 This image was achieved via the Creative Lighting n Wireless remote controllers p19 System and the photog- n Viewing attachments and remote control accessories p20 rapher’s imagination. Two Speedlight units n Other accessories p21 that support Advanced Wireless Lighting (one in n System compatibility pp22-23 the kayak and one from above) were wirelessly triggered with a properly positioned SU-800 to send command signals to both remote units.