User's Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Embedded Linux Systems with the Yocto Project™

OPEN SOURCE SOFTWARE DEVELOPMENT SERIES Embedded Linux Systems with the Yocto Project" FREE SAMPLE CHAPTER SHARE WITH OTHERS �f, � � � � Embedded Linux Systems with the Yocto ProjectTM This page intentionally left blank Embedded Linux Systems with the Yocto ProjectTM Rudolf J. Streif Boston • Columbus • Indianapolis • New York • San Francisco • Amsterdam • Cape Town Dubai • London • Madrid • Milan • Munich • Paris • Montreal • Toronto • Delhi • Mexico City São Paulo • Sidney • Hong Kong • Seoul • Singapore • Taipei • Tokyo Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals. The author and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein. For information about buying this title in bulk quantities, or for special sales opportunities (which may include electronic versions; custom cover designs; and content particular to your business, training goals, marketing focus, or branding interests), please contact our corporate sales depart- ment at [email protected] or (800) 382-3419. For government sales inquiries, please contact [email protected]. For questions about sales outside the U.S., please contact [email protected]. Visit us on the Web: informit.com Cataloging-in-Publication Data is on file with the Library of Congress. -

OS-9 for Intel IXDP425 Board Guide

OS-9® for IXDP425 Board Guide Version 4.7 www.radisys.com Revision A • July 2006 Copyright and publication information Reproduction notice This manual reflects version 4.7 of Microware OS-9. The software described in this document is intended to Reproduction of this document, in part or whole, by any means, be used on a single computer system. RadiSys electrical, mechanical, magnetic, optical, chemical, manual, or Corporation expressly prohibits any reproduction of the otherwise is prohibited, without written permission from RadiSys software on tape, disk, or any other medium except for Microware Communications Software Division, Inc. backup purposes. Distribution of this software, in part or whole, to any other party or on any other system Disclaimer may constitute copyright infringements and misappropriation of trade secrets and confidential The information contained herein is believed to be accurate as of processes which are the property of RadiSys the date of publication. However, RadiSys Corporation will not be Corporation and/or other parties. Unauthorized liable for any damages including indirect or consequential, from distribution of software may cause damages far in use of the OS-9 operating system, Microware-provided software, excess of the value of the copies involved. or reliance on the accuracy of this documentation. The information contained herein is subject to change without notice. July 2006 Copyright ©2006 by RadiSys Corporation All rights reserved. EPC and RadiSys are registered trademarks of RadiSys Corporation. ASM, Brahma, DAI, DAQ, MultiPro, SAIB, Spirit, and ValuePro are trademarks of RadiSys Corporation. DAVID, MAUI, OS-9, OS-9000, and SoftStax are registered trademarks of RadiSys Corporation. -

Building Embedded Linux Systems ,Roadmap.18084 Page Ii Wednesday, August 6, 2008 9:05 AM

Building Embedded Linux Systems ,roadmap.18084 Page ii Wednesday, August 6, 2008 9:05 AM Other Linux resources from O’Reilly Related titles Designing Embedded Programming Embedded Hardware Systems Linux Device Drivers Running Linux Linux in a Nutshell Understanding the Linux Linux Network Adminis- Kernel trator’s Guide Linux Books linux.oreilly.com is a complete catalog of O’Reilly’s books on Resource Center Linux and Unix and related technologies, including sample chapters and code examples. ONLamp.com is the premier site for the open source web plat- form: Linux, Apache, MySQL, and either Perl, Python, or PHP. Conferences O’Reilly brings diverse innovators together to nurture the ideas that spark revolutionary industries. We specialize in document- ing the latest tools and systems, translating the innovator’s knowledge into useful skills for those in the trenches. Visit con- ferences.oreilly.com for our upcoming events. Safari Bookshelf (safari.oreilly.com) is the premier online refer- ence library for programmers and IT professionals. Conduct searches across more than 1,000 books. Subscribers can zero in on answers to time-critical questions in a matter of seconds. Read the books on your Bookshelf from cover to cover or sim- ply flip to the page you need. Try it today for free. main.title Page iii Monday, May 19, 2008 11:21 AM SECOND EDITION Building Embedded Linux SystemsTomcat ™ The Definitive Guide Karim Yaghmour, JonJason Masters, Brittain Gilad and Ben-Yossef, Ian F. Darwin and Philippe Gerum Beijing • Cambridge • Farnham • Köln • Sebastopol • Taipei • Tokyo Building Embedded Linux Systems, Second Edition by Karim Yaghmour, Jon Masters, Gilad Ben-Yossef, and Philippe Gerum Copyright © 2008 Karim Yaghmour and Jon Masters. -

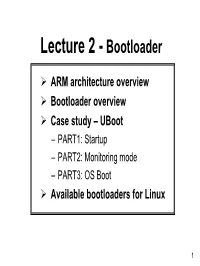

Lecture 2 - Bootloader

Lecture 2 - Bootloader ¾ ARM architecture overview ¾ Bootloader overview ¾ Case study – UBoot – PART1: Startup – PART2: Monitoring mode – PART3: OS Boot ¾ Available bootloaders for Linux 1 ARM Architecture Overview • ARM Operating Modes – User mode: a normal program execution state – FIQ – Fast Interrupt: for fast interrupt handling – IRQ – Normal Interrupt: for general purpose interrupt handling – Supervisor mode (SVC): a protected mode for operating system – Abort mode: when a data or instruction pre-fetch is aborted – Undefined mode: when an undefined instruction is executed – System mode: a privileged user mode for the operating system • ARM Processor States – Arm state: all instructions are 32bits long, word-aligned. – Thumb state: all instructions are 16 bits wide, half-word aligned. – Jazelle state: all instructions are 8 bits wide for Java Bytecode (for v5TEJ only) 2 ARM Architecture Overview • ARM-State Registers 3 ARM Architecture Overview • Thumb-State Registers 4 ARM Architecture Overview • Program Status Register (PSR) ¾ CPSR: Current Program Status Register ¾ SPSR: Saved Program Status Register 5 ARM Architecture Overview • ARM Exception Types – Reset • Hardware reset: when the processor reset pin is asserted • Software reset: by branching to the reset vector (0x0000) – Undefined instruction • the processor cannot recognize the currently execution instruction – Software Interrupt (SWI) • By s/w instruction, to allow a program running in User mode to request privileged operations that are in Supervisor mode – Prefetch Abort -

Redboot · User Manual

RedBoot · User Manual RedBoot · User Manual Important hints Thank you very much for purchasing a Garz & Fricke product. Our products are dedicated to professional use and therefore we suppose extended technical knowledge and practice in working with such products. The information in this manual is subject to technical changes, particularly as a result of continuous product upgrades. Thus this manual only reflects the technical status of the products at the time of printing. Before design-in the device into your or your customer’s product, please verify that this document and the therein described specification is the latest revision and matches to the PCB version. We highly recommend contacting our technical sales team prior to any activity of that kind. A good way getting the latest information is to check the release notes of each product and/or service. Please refer to the chapter [Online Support]. The attached documentation does not entail any guarantee on the part of Garz & Fricke GmbH with respect to technical processes described in the manual or any product characteristics set out in the manual. We do not accept any liability for any printing errors or other inaccuracies in the manual unless it can be proven that we are aware of such errors or inaccuracies or that we are unaware of these as a result of gross negligence and Garz & Fricke has failed to eliminate these errors or inaccuracies for this reason. Garz & Fricke GmbH expressly informs that this manual only contains a general description of technical processes and instructions which may not be applicable in every individual case. -

Practical Practical

PRACTICAL PRACTICAL GPLCOMPLIANCE GPLCOMPLIANCE A GUIDE FOR STARTUPS, SMALL ABUSINESSES GUIDE FOR STARTUPS, AND ENGINEERS SMALL BUSINESSES AND ENGINEERS ARMIJN HEMEL, MSC AND SHANE COUGHLAN ARMIJN HEMEL, MSC AND SHANE COUGHLAN Copyright © 2017 Linux Foundation All rights reserved. This book or any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of the publisher except for the use of brief quotations in a book review and certain other noncommercial uses permitted by copyright law. Printed in the United States of America First Edition, 2017 ISBN: 978-0-9989078-0-2 1 Letterman Drive Building D Suite D4700 San Francisco CA 94129 Phone/Fax: +1 415 723 9709 https://linuxfoundation.org About the Authors Shane Coughlan Shane Coughlan is an expert in communi- cation, security, and business development. His professional accomplishments include spearheading the licensing team that elevated Open Invention Network into the largest patent non-aggression community in history, establishing the leading professional network of open source legal experts, and aligning stakeholders to launch both the first law journal and the first law book dedicated to open source. He currently leads the OpenChain community as Program Manager. Shane has extensive knowledge of open source governance, internal process development, supply chain management, and community building. His experience includes engagement with the enterprise, embedded, mobile, and automotive industries. Armijn Hemel Armijn Hemel is the owner of Tjaldur Software Governance Solutions. He is an active re- searcher of and internationally recognized expert in open source license compliance and supply chain management. He studied computer science at Utrecht University in The Netherlands, where he pioneered reproducible builds with NixOS. -

Anthony J. Massa

EMBEDDED SOFTWARE DEVELOPMENT WITH ECOS™ Anthony J. Massa EMBEDDED SOFTWARE DEVELOPMENT WITH ECOS Anthony J. Massa PRENTICE HALL PROFESSIONAL TECHNICAL REFERENCE UPPER SADDLE RIVER, NJ 07458 WWW.PHPTR.COM WWW.PHPTR.COM/MASSA/ Library of Congress Cataloging-in-Publication Data Massa, Anthony J. Embedded software development with eCos / Anthony J. Massa p. cm.--(Bruce Perens' Open source series) ISBN 0-13-035473-2 1. Embedded computer systems--Programming. 2. Application software--Development. 3. Real-time data processing. I. Title. II. Series. QA76.6 .M364317 2002 005.26--dc21 2002035507 Editorial/production supervision: Techne Group Cover design director: Jerry Votta Cover design: Anthony Gemmellaro Art director: Gail Cocker-Bogusz Interior design: Meg Van Arsdale Manufacturing buyer: Maura Zaldivar Editor-in-Chief: Mark L. Taub Editorial assistant: Kate Wolf Marketing manager: Bryan Gambrel Full-service production manager: Anne R. Garcia © 2003 Pearson Education, Inc. Publishing as Prentice Hall Professional Technical Reference Upper Saddle River, New Jersey 07458 This material may be distributed only subject to the terms and conditions set forth in the Open Publication License, v1.0 or later (the latest version is presently available at <http://www.opencontent.org/openpub/>). Prentice Hall books are widely used by corporations and government agencies for training, marketing, and resale. For information regarding corporate and government bulk discounts please contact: Corporate and Government Sales (800) 382-3419 or [email protected] Other company and product names mentioned herein are the trademarks or registered trademarks of their respective owners. All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher. -

Intelligent Medical Device Integration with Real Time Operating System

Copyright is owned by the Author of the thesis. Permission is given for a copy to be downloaded by an individual for the purpose of research and private study only. The thesis may not be reproduced elsewhere without the permission of the Author. Intelligent Medical Device Integration with Real Time Operating System by © Zaid Jan A thesis submitted to the School of Engineering in partial fulfilment of the requirements for the degree of Master of Engineering Department of Electronics and Computer Syetem Engineering at Massey University, [Albany], New Zealand April 2009 Abstract Many commercial devices now being produced have the ability to be remotely monitored and controlled. This thesis aims to develop a generic platform that can easily be extended to interface with many different kinds of devices for remote monitoring and control via a TCP/IP connection. The deployment will be concentrated on Medical devices but can be extended to all serial device interfaces. The hardware to be used in the development of this platform is an ARM Cortex M3 based Micro-Controller board which has to be designed to meet the requirement set by the Precept Health the founder of this platform. The design was conducted at Massey University in collaboration with senior engineer from the company. The main task in achieving the aim was the development of the necessary software layers to implement remote monitoring and control. The eCosCentric real-time embedded operating system was used to form a generic base for developing applications to monitor and control specific devices. The majority of the work involved in this project was the deployment of the operating system to the Micro-Controller. -

Uboot and Redboot a Compartive Study

Jeevan Prasath S Tejas Krishna UBOOT AND REDBOOT A COMPARTIVE STUDY Abstract :This Paper attempts to provide the basic understanding of the BIOS and the Boot loader in general and does a comparative study of the two Boot loaders the Redboot and the Uboot .With its main focus on the hardware abstraction layers that are provided by these bootloaders ,which acts as an generic interface between the underlying hardware and the Operating System Software. The paper goes ahead and provides the basic sequences that are followed during the power on startup in each of the boot loaders and the Hardware abstraction layers of the two boot loaders are compared through their interfaces and the standardized modularity through their layers which brings about the compatibility of the boot loaders across all the CPU architectures. In this paper we attempt to study the HAL (Hardware Abstraction Layer) organization for a simple serial device across the two boot loaders. The basic boot up configuration procedure followed for a Beagle Board using the Uboot is also covered as a part of this paper. As a conclusion the paper tries to summarize the need for the HAL and how the standardization of this is achieved in both the boot loaders. The scope of the paper does not cover the need for having different boot loaders with all providing the same services. Introduction: BIOS this stands for the Basic Input and Output System this is a piece of the software that generally resides on the processor chip the main responsibility of this is locate the source of the bootloader that is in which storage device it is available and then give control to the bootloader for its execution. -

Interfacing Freebsd with U-Boot

Interfacing FreeBSD with U-Boot Rafał Jaworowski [email protected] BSDCan 2008, Ottawa Introduction – TOC ● U-Boot basics ● Overview of FreeBSD booting process ● loader(8) + U-Boot ● New API for standalone applications ● Summary Interfacing FreeBSD with U-Boot BSDCan 2008 Was ist Das U-Boot? ● Firmware – Stored in permanent memory (NOR/NAND FLASH) ● Initial level boot loader ● Configures H/W and starts operating system ● Overall operation – First executing from the permanent memory – Elementary CPU initialization, cache enable/disable, stack fixup etc. – Console – RAM initialization (controller, memory modules) – Relocation to RAM, continue executing from there – Further configuration of a system – Autoboot or interactive loop (user prompt) – No interrupts (polling) Interfacing FreeBSD with U-Boot BSDCan 2008 After relocation to RAM RAM end U-Boot code/data Heap (malloc area) Stack User area Reserved RAM start Interfacing FreeBSD with U-Boot BSDCan 2008 U-Boot highlights ● Written in C and assembly ● Accompanied by helper applications, host tools, documentation ● Self-contained source tree ● Closely tied to Linux – Follows its standards – Coding style – Interfaces (Flattened Device Tree) – License (GPLv2) ● Omnipresent in the PowerPC world, popular on other architecters too ● History: PPCBoot Interfacing FreeBSD with U-Boot BSDCan 2008 Supported systems ● Architectures – ARM, AVR32, BlackFin, ColdFire, MicroBlaze, MIPS, NIOS, PowerPC, SH ● SoCs ● Platforms (boards) – $ ls include/configs/ | wc 423 423 4363 ● Peripherals – FLASH, DRAM chips, -

Standard Bootstrap Firmware Technical Overview Functionality

Standard Bootstrap Firmware RedBoot™ is a comprehensive debug and bootstrap firmware solution for the development, deployment and management of embedded devices. It supports the installation, execution and debugging of all types of embedded applications, ranging from native stand-alone, proprietary and eCos® RTOS based applications, through to embedded Linux® systems. RedBoot has been adopted by many semiconductor and development board manufacturers as their standard bootstrap firmware. It is the standard firmware shipped with all Intel® XScale® development boards, various Freescale ARM and PowerPC platforms, and NXP set top box reference designs. All major architectures are supported including ARM®, ColdFire®, MIPS®, PowerPC®, SuperH®, XScale® and x86. RedBoot has been deployed in embedded products from ASCOM®, Axis®, HP®, Intel®, Linksys®, Meraki®, NETGEAR®, Watchguard®, Yamaha®, Zyxel® and many others. Most development boards supported by eCosCentric’s eCosPro® Developer’s Kit also include a port of RedBoot. The feature set of RedBoot provides support for all phases of a product’s life-cycle. In the initial development phases it provides a standardized bootstrap and debug environment on commercial development boards and on an OEM’s own prototype hardware. During manufacturing it can provide application installation, power-on self tests (POST), and built-in diagnostic tests to enhance quality control and assurance. Finally, when deployed in products and used in the field, RedBoot provides the system bootstrap mechanism, site specific configuration ability, as well as a straightforward migration path for firmware upgrades. eCosCentric provides a range of commercial RedBoot focused services that cover porting, customization and technical support, simplifying the provision of firmware for your embedded design. -

Building a Linux Image and Downloading Onto I.MX Processors Using a Virtual Machine

Freescale Semiconductor Document Number: AN3875 Application Note Rev. 1, 08/2009 Building a Linux Image and Downloading onto i.MX Processors Using a Virtual Machine Multimedia Applications Division Freescale Semiconductor, Inc. Detroit, MI A virtual machine (VM) is a software Contents implementation of a machine (computer) that 1 Introduction .................................................. 2 executes programs like a real machine. This 2 Creating a Virtual Machine ............................ 5 application note specifies the following: 3 Installing VM Player....................................... 9 • The details of how to create a virtual 4 Installing Debian in the Virtual Machine ..... 14 machine using open source software 5 Install Freescale LTIB for i.MX Processors . 41 Appendix A i.MX51 Bootlog ............................ 59 on a Windows machine. • Installation of Debian Linux on this virtual machine. • Installation of Linux Target Image Builder (LTIB) on the virtual machine and set up the host to TFTP files on the target. © Freescale Semiconductor, Inc., 2009. All rights reserved. _______________________________________________________________________ 1 Introduction This document details the following steps using open source tools and Freescale provided board support packages. • Creating a virtual machine using open source software on a Windows machine • Installing Debian Linux on this virtual machine • Installing Linux Target Image Builder (LTIB) on the virtual machine and setting up the host to TFTP files on the target 1.1 Scope This document is meant to serve as a step-by-step guide for hardware and software engineers to create their own virtual machines, install Linux on it, and create their own Linux image to be downloaded onto i.MX processors. 1.2 Overview This section includes a brief introduction to virtual machines, discusses different embedded operating systems, and presents how they fit into the i.MX development environment.