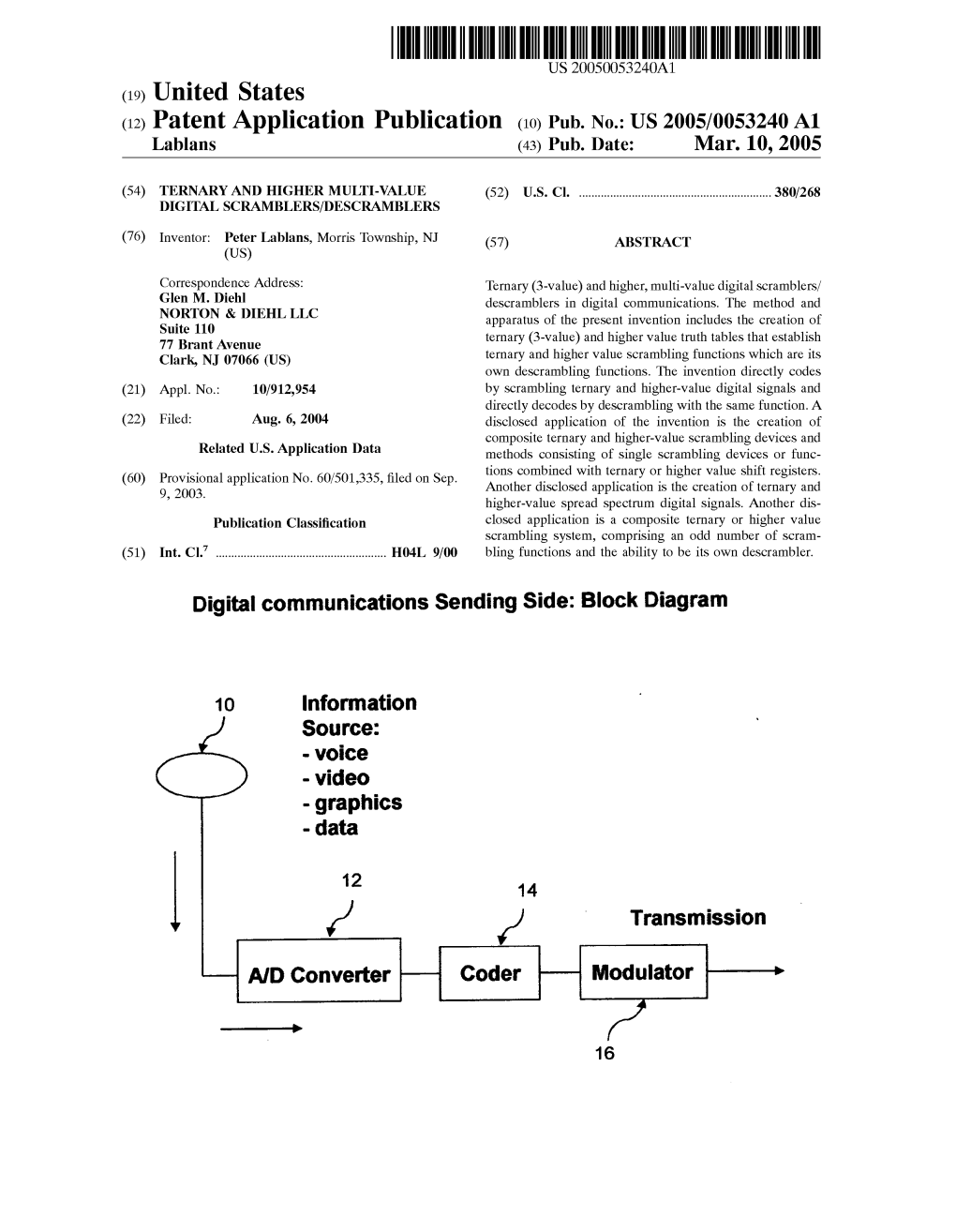

Digital Communications Sending Side: Block Diagram

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Criteria for Choosing Line Codes in Data Communication

ISTANBUL UNIVERSITY – YEAR : 2003 (843-857) JOURNAL OF ELECTRICAL & ELECTRONICS ENGINEERING VOLUME : 3 NUMBER : 2 CRITERIA FOR CHOOSING LINE CODES IN DATA COMMUNICATION Demir Öner Istanbul University, Engineering Faculty, Electrical and Electronics Engineering Department Avcılar, 34850, İstanbul, Turkey E-mail: [email protected] ABSTRACT In this paper, line codes used in data communication are investigated. The need for the line codes is emphasized, classification of line codes is presented, coding techniques of widely used line codes are explained with their advantages and disadvantages and criteria for chosing a line code are given. Keywords: Line codes, correlative coding, criteria for chosing line codes.. coding is either performed just before the 1. INTRODUCTION modulation or it is combined with the modulation process. The place of line coding in High-voltage-high-power pulse current The transmission systems is shown in Figure 1. purpose of applying line coding to digital signals before transmission is to reduce the undesirable The line coder at the transmitter and the effects of transmission medium such as noise, corresponding decoder at the receiver must attenuation, distortion and interference and to operate at the transmitted symbol rate. For this ensure reliable transmission by putting the signal reason, epecially for high-speed systems, a into a form that is suitable for the properties of reasonably simple design is usually essential. the transmission medium. For example, a sampled and quantized signal is not in a suitable form for transmission. Such a signal can be put 2. ISSUES TO BE CONSIDERED IN into a more suitable form by coding the LINE CODING quantized samples. -

(12) Patent Application Publication (10) Pub. No.: US 2004/0131130A1 Shor Et Al

US 2004O131130A1 (19) United States (12) Patent Application Publication (10) Pub. No.: US 2004/0131130A1 Shor et al. (43) Pub. Date: Jul. 8, 2004 (54) SYSTEM AND METHOD FOR MULTI-BAND (60) Provisional application No. 60/404,070, filed on Aug. ULTRA-WIDE BAND SIGNAL GENERATORS 16, 2002. Provisional application No. 60/450,737, filed on Feb. 28, 2003. (76) Inventors: Gadi Shor, Tel-Aviv (IL); David Yaish, Tel-Aviv (IL); Yaron Knobel, Publication Classification Givat-Shmuel (IL); David Meshulam, Hod-Hasharon (IL); Zeev Rubin, (51) Int. Cl. ................................................. H04L 27/20 Alphei-Mcnashe (IL); Benny Blumer, Kfar-Saba (IL) (52) U.S. Cl. .............................................................. 375/308 Correspondence Address: BROWN, RAYSMAN, MILLSTEIN FELDER & STEINER LLP 9 9 (57) ABSTRACT 900 THIRDAVENUE NEW YORK, NY 10022 (US) The present invention provides Systems and methods relat ing to ultra-wide band communications. A method is pro (21) Appl. No.: 10/643,108 Vided for transmitting information using ultra-wide band transmission. The method includes allocating, for Signal (22)22) FileFilled: Aug.ug. 18,185, 2003 transmission, each of a plurality of frequencys Sub-bands. Related U.S. Application Data The method further includes sending an ultra-wide band transmission comprising the information by transmitting a (63) Continuation-in-part of application No. 10/389,789, burst symbol cycle Signal over each of the plurality of filed on Mar. 17, 2003. frequency Sub-bands. 10560Mhz. 1320 MHz 213 Data Y1 2O2 Out 5280,5060Hz Clk Z 211 Ref 210 RF Out MHz 1012OMZ Z Channel IFMHz :253 5280 5060 88O 3960 528O 5060 440 5280 5060 0 4840 5280 5060 5280 5060 5940 5280 5060 1320 6160 5280 5060 1760 6600 Patent Application Publication Jul. -

"CPM Signals for Machine to Machine Communications"

N o d’ordre: 2015telb0367 Sous le sceau de l’Université Européenne de Bretagne Télécom Bretagne En accréditation conjointe avec l’Ecole Doctorale Sicma Application des signaux CPM pour la collecte de données à grande échelle provenant d’émetteurs faible coût Thèse de Doctorat Mention: Sciences et Technologies de l’information et de la Communication (STIC) Présentée par: Malek Messai Département: Signal et Communications Laboratoire: LabSTICC Pôle CACS/COM Directrice de thèse: Karine AMIS Soutenue le 20 Novembre 2015 Jury : Rapporteurs: Mérouane Debbah - Centrale-Supélec/ HUAWEI Philippe Ciblat - Telecom Paris Tech Examinateurs: Giulio Colavolpe - Università degli Studi di Parma (Italy) Gilles Burel - Université de Bretagne Occidentale Jérôme Lebrun - CNRS/ Université de Nice Sophia Antipolis Encadrants: Karine Amis - Telecom Bretagne Frédéric Guilloud - Telecom Bretagne Invité: Alain Dominique Thomas - Zodiac Aerospace Acknowledgments would like to express my sincerest thanks and appreciation to all the members of I the Signal and Communications department for welcoming me in your laboratory. I have met many people inside and outside the work sphere that made the Ph.D an enjoyable adventure. I am deeply grateful to my supervisors, Dr. Karine AMIS and Dr. Frédéric GUILLOUD, for their invaluable advice, kindness, encouragements, patience and support during these three years. Their profound scientific knowledge, invaluable insight and experience have had a great impact on the success of the thesis. There is no doubt in my mind that without their comments, criticisms and guidance, my Phd will not be accomplished. I am also indebted to them for giving me the opportunity to improve my research background and experience. I am very lucky to have had the opportunity to work with them. -

Advanced Modulation Formats and Multiplexing Techniques for Optical Telecommunication Systems 13

Advanced Modulation Formats and Multiplexing Techniques for Optical Telecommunication Systems 13 Advanced Modulation Formats and Multiplexing Techniques for Optical X2 Telecommunication Systems Ghafour Amouzad Mahdiraji and Ahmad Fauzi Abas Advanced Modulation Formats and Multiplexing Techniques for Optical Telecommunication Systems Ghafour Amouzad Mahdiraji1 and Ahmad Fauzi Abas2 1UCSI University & 2Universiti Putra Malaysia Malaysia 1. Introduction Since ancient times, one of the principal needs of people has been to communicate. This need created interest in devising communication systems for sending messages from one place to another. The advent of high performance computer processors brought many advantages for digital communications over that of analog. These benefits include more features, easy storage and faster processing. These caused huge amount of information, which is increasing exponentially every year, to be carried over communication networks. Various types of communication system appeared over the years. Among the basic motivations behind each type are to improve the transmission fidelity, increase the data rate, and increase the transmission distance between stations. All these facilities are achievable utilizing optical fiber communications. Optical fiber offers several advantages over the traditional media (e.g., twisted wire pair and coaxial cable). Its decisive advantages are huge bandwidth and very low attenuation and noise (Arumugam, 2001). The first, results in higher bit rate, and the second, results in longer transmission distance. These potentials can be further pushed by utilizing multiplexing techniques and/or advanced modulation formats. The invention of wavelength division multiplexing (WDM) (G. E. Keiser, 1999) contributes great benefit to the optical fiber communication systems especially after the introduction of Erbium-doped fiber amplifier (EDFA). -

CODING and MODULATION for BANDWIDTH COMPRESSION of TELEVISION and FACSIMILE SIGNALS. a Thesis Submitted for the Degree of Doctor

CODING AND MODULATION FOR BANDWIDTH COMPRESSION OF TELEVISION AND FACSIMILE SIGNALS. A thesis submitted for the degree of Doctor of Philosophy by PIOTR WLADYSLAW JOZta BYLANSKI Imperial College, University of London. 1966. 2. ABSTRACT Two aspects relevant to the coding of picture signals with a view to compression of signal bandwidth are considered. Firstly: the problem of combining the information associated with the run length representation of the picture signal, for transmission over a practical channel, is studied. A solution is proposed in terms of combined amplitude and phase modulation and an analysis is presented which demonstrates the feasibility of the technique. Secondly, several aspects of the digram representation of the picture signal are studied. The second order redundancy is experimentally determined using a digital technique. The results obtained lead to the design of several simple and efficient digram -based codes for black and white facsimile pictures, result- ing in useful reduction of signal bandwidth. These codes are implemented and assessed experimentally. An adaptive encoding technique is proposed whereby errors produced by a non-uniquely decodable code may be minimised in a controlled way by the use of predictive feedback at the encoder. 3. CONTENTS. Item Page ABSTRACT 2 CONTENTS 3 LIST OF SYMBOLS AND ABBREVIATIONS 6 ACKNOWLEDGEMENTS 9 CHAPTER. 1. INTRODUCTION 10 141 The Trend of Modern Communications. 10 1.2 Visual Redundancy. 11 1.3 Signal Compression. 13 1.4 Television and Facsimile Communication. 16 1,5 The Organisation of the Material of this Work. 18 1.6 Summaries of Individual Chapters. 19 CHAPTER 2. THE PROBLEM OF CHANNEL UTILISATION. -

Method, System and Transceiver Device for Bi-Directionally

(19) TZZ ¥Z ¥_T (11) EP 2 830 239 A1 (12) EUROPEAN PATENT APPLICATION (43) Date of publication: (51) Int Cl.: 28.01.2015 Bulletin 2015/05 H04B 10/25 (2013.01) H04J 14/02 (2006.01) H04B 10/516 (2013.01) (21) Application number: 13003679.1 (22) Date of filing: 23.07.2013 (84) Designated Contracting States: • Elbers, Jörg-Peter AL AT BE BG CH CY CZ DE DK EE ES FI FR GB 82256 Fürstenfeldbruck (DE) GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO • Griesser, Helmut PL PT RO RS SE SI SK SM TR 86551 Aichach (DE) Designated Extension States: • Eiselt, Michael BA ME 99334 Kirchheim (DE) (71) Applicant: ADVA AG Optical Networking (74) Representative: Eder, Thomas 98617 Meiningen (DE) Eder & Schieschke Patentanwälte (72) Inventors: Elisabethstrasse 34 • Grobe, Klaus 80796 München (DE) 82152 Planegg (DE) (54) Method, system and transceiver device for bi- directionally transmitting digital optical signals over an optical transmission link (57) The invention relates to a method for bi-direc- (S1TX,CHI) received at the second end of the optical trans- tionally transmitting digital optical signals over an optical mission link, the optical wavelength reuse signal being transmission link, wherein a first optical transmit signal modulated according to a second digital signal in such a (S1TX,CHI) at a predetermined optical wavelength is sup- way that the bit information of the second digital signal plied to a first end of the optical transmission link and is included in second sections of the symbol interval of transmitted in a first transmission direction to a second the first optical transmit signal (S1TX,CHI) received. -

The Use of Digital Circuits in Data Transmission

,1969, No. 3 71 The use of digital circuits in data transmission P. J. van Gerwen Data transmission is the name given to the transmission of digital signals in such a form that they can be applied directly to a computer. Now that computers are being more and more widely used, it is becoming much more important to be able to transmit these signals reliably and at high speed. In this article it is shown that where data signals have to be transmitted over ordinary telephone lines, digital circuits have several advantages over conventional circuits containing inductors and capacitors. A survey is given of digital cir- cuits designedfor this purpose. The use of such circuits has made it possible to design a data transmitter in the form of an integrated circuit on a chip a few millimetres square. A significant development of the last few years is the transmission, but in order to use a telephone system growth of a new branch of computer technology: the for binary pulse trains an extra operation is required. combination of computer and telecommunications. To Telephone lines are, after all, designed for speech: only make the most economic use of the computer, it is signals at frequencies required for intelligibility are located at a central point and connected to the more or transmitted (ranging from 300 to 3400 Hz). Data sig- less distant places where the users are situated. The nals, however, have' a spectrum that also possesses a information to be processed then has to be supplied to d.c. component and a number of a.c. -

An Overview of Coherent and Non-Coherent Pulse Compression Waveforms T

J E E I C E International Journal of Electrical, Electronics ISSN No. (Online): 2277-2626 and Computer Engineering 9(1&2): 01-05(2020) An Overview of Coherent and Non-coherent Pulse Compression Waveforms T. D. Bhatt Department of Electronics and Communication Engineering, Mahatma Gandhi Institute of Technology, Chaitanya Bharathi (post), Gandipet, Hyd-75, Telangana, India. (Corresponding author: T. D. Bhatt) (Received 25 February 2020, Accepted 09 June 2020) (Published by Research Trend, Website: www.researchtrend.net) ABSTRACT: One central issue in the design of radar waveform is its capability to resolve two closely spaced small targets, which are located at long range. In this context the most promising technique that is used by modern radar systems is pulse compression. This technique combines the advantages of energy associated with long pulse-width and range-resolution corresponding to a short duration pulse. The matched filter used in receiver accumulates the received energy in to a short pulse. This paper presents an overview of the aperiodic and periodic phase coded waveforms for Coherent and Non- Coherent Pulse Compression radar systems. Keywords: Autocorrelation, Cross-correlation, matched filter, pulse compression, range-resolution. I. INTRODUCTION predetermined values. That is, each pulse of such Woodward’s [1] studies play significant role in the waveform has a 100% duty cycle. The correlated context of radar signal design. The basic concept of his compressed pulse is achieved at the output of matched presentations is to achieve energy requirement for filter used in radar receivers. In phase coded signals, the detection of a target at long ranges, a wide pulse can be pulse compression ratio is N, where N is the number of transmitted. -

Spread Spectrum and CDMA : Principles and Applications

//INTEGRAS/KCG/PAGINATION/WILEY/SSPA/FINALS_17-02-05/PRELIMS.3D – 3 – [1–12/12] 18.2.2005 5:15PM Spread Spectrum and CDMA Principles and Applications Valery P. Ipatov University of Turku, Finland and St. Petersburg Electrotechnical University ‘LETI’, Russia //INTEGRAS/KCG/PAGINATION/WILEY/SSPA/FINALS_17-02-05/PRELIMS.3D – 2 – [1–12/12] 18.2.2005 5:15PM //INTEGRAS/KCG/PAGINATION/WILEY/SSPA/FINALS_17-02-05/PRELIMS.3D – 1 – [1–12/12] 18.2.2005 5:15PM Spread Spectrum and CDMA //INTEGRAS/KCG/PAGINATION/WILEY/SSPA/FINALS_17-02-05/PRELIMS.3D – 2 – [1–12/12] 18.2.2005 5:15PM //INTEGRAS/KCG/PAGINATION/WILEY/SSPA/FINALS_17-02-05/PRELIMS.3D – 3 – [1–12/12] 18.2.2005 5:15PM Spread Spectrum and CDMA Principles and Applications Valery P. Ipatov University of Turku, Finland and St. Petersburg Electrotechnical University ‘LETI’, Russia //INTEGRAS/KCG/PAGINATION/WILEY/SSPA/FINALS_17-02-05/PRELIMS.3D – 4 – [1–12/12] 18.2.2005 5:15PM Copyright Ó 2005 John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England Telephone (þ44) 1243 779777 Email (for orders and customer service enquiries): [email protected] Visit our Home Page on www.wiley.com All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London W1T 4LP, UK, without the permission in writing of the Publisher. -

Signal Detection for Ambient Backscatter Communication with OFDM Carriers

sensors Article Signal Detection for Ambient Backscatter Communication with OFDM Carriers Thu L. N. Nguyen 1 , Yoan Shin 1,∗, Jin Young Kim 2 and Dong In Kim 3 1 School of Electronic Engineering, Soongsil University, Seoul 06978, Korea; [email protected] 2 Department of Wireless Communications Engineering, Kwangwoon University, Seoul 01897, Korea; [email protected] 3 College of Information and Communication Engineering, Sungkyunkwan University, Suwon 16419, Gyeonggi-do, Korea; [email protected] * Correspondence: [email protected] Received: 18 December 2018; Accepted: 23 January 2019; Published: 26 January 2019 Abstract: Ambient backscatter communication (AmBC) is considered as a promising future emerging technology. Several works on AmBC have been proposed thanks to its convenience and low cost property. This paper focuses on finding the optimal energy detector at the receiver side and estimating the corresponding bit error rate for the communication system utilizing the AmBC. Through theoretical and numerical analyses, we present two important results. First, we improve the existing energy detector by calculating the optimal averaging power orders. Second, we take advantage of the early work on orthogonal frequency division multiplexing (OFDM), where the repeating structure of ambient OFDM signals is exploited to cancel out the direct-link interference by using a cyclic prefix, then provide a test statistic in which optimal detection threshold and optimal power order are derived accordingly. The study reveals the inherent limitation of AmBC energy detectors and provides a guidance for achieving optimal power order for a given significance level. Keywords: ambient backscatter communication; energy detector; OFDM; test statistic 1. Introduction Ambient backscatter communication (AmBC) is a new mechanism in which a device can communicate with others by backscattering ambient radio-frequency (RF) signals (e.g, WiFi, TV signals) without any additional power suppliers [1,2]. -

FED-STD-1037C T: Abbreviation for Tera

FED-STD-1037C T: Abbreviation for tera (1012 ). See net. This means that each unit receives all the International System of Units. information transmitted. This is a direct transfer of data and no relaying is involved. (188) Tactical Automatic Digital Switching System (TADSS): A tactical data information link—B (TADIL—B): A transportable store-and-forward point-to-point data link between two units which message-switching system used for rapid deployment provides for simultaneous transmission and reception in support of tactical forces. (188) of data (duplex). (188) tactical command and control (C2 ) systems: The tactical load: For the host service tactical forces, the equipment, communications, procedures, and total power requirements for communications, personnel essential to a commander for planning, including the requirements for weapons, detection, directing, coordinating, and controlling tactical command and control systems, and related support operations of assigned forces pursuant to assigned functions. (188) Note: The tactical load is a part of missions. the operational load. tactical communications: Communications in which TADIL: Acronym for tactical data information link. information of any kind, especially orders and decisions, are conveyed from one command, person, TADSS: Acronym for Tactical Automatic Digital or place to another within the tactical forces, usually Switching System. by means of electronic equipment, including communications security equipment, organic to the tag: See flag, label. tactical forces. (188) Note: Tactical communications do not include communications provided to tactical tag image file format (TIFF): A file format used to forces by the Defense Communications System store an image using the particular data structure of (DCS), to nontactical military commands, and to the file. -

Data Transmission Using Hierarchical Modulation

Europäisches Patentamt *EP001406421A2* (19) European Patent Office Office européen des brevets (11) EP 1 406 421 A2 (12) EUROPEAN PATENT APPLICATION (43) Date of publication: (51) Int Cl.7: H04L 27/34 07.04.2004 Bulletin 2004/15 (21) Application number: 03256098.9 (22) Date of filing: 29.09.2003 (84) Designated Contracting States: • Hayashi, Takahiro, c/o NTT DoCoMo Inc. AT BE BG CH CY CZ DE DK EE ES FI FR GB GR Tokyo 100-6150 (JP) HU IE IT LI LU MC NL PT RO SE SI SK TR • Futakata, Toshiyuki, c/o NTT DoCoMo Inc. Designated Extension States: Tokyo 100-6150 (JP) AL LT LV MK (74) Representative: (30) Priority: 03.10.2002 JP 2002291571 Luckhurst, Anthony Henry William MARKS & CLERK, (71) Applicant: NTT DoCoMo, Inc. 57-60 Lincoln’s Inn Fields Tokyo 100-6150 (JP) London WC2A 3LS (GB) (72) Inventors: • Moon, Sung Uk, NTT DoCoMo Inc. Tokyo 100-6150 (JP) (54) Data transmission using hierarchical modulation (57) A modulation device comprises a modulation ta having been subjected to hierarchical modulation us- unit (2) that modulates data in a hierarchical manner us- ing multiple types of modulation techniques, and a de- ing multiple types of modulation techniques, and a trans- modulation unit (6) that demodulates the hierarchical mission unit (3) that transmits the hierarchically modu- modulation data using a demodulation technique corre- lated data. A demodulation device comprises a receiv- sponding to a specific hierarchy of the hierarchical mod- ing unit (4) that receives the hierarchical modulation da- ulation data. EP 1 406 421 A2 Printed by Jouve, 75001 PARIS (FR) 1 EP 1 406 421 A2 2 Description with the above-described QPSK under the same trans- mission rate, the occupied band-width of 16-QAM is nar- BACKGROUND OF THE INVENTION rower than that of QPSK.