ARM® Cortex® -M3 & M4 MCU Architecture

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Bluetooth Low Energy Software Release Notes

BLUEGIGA BLUETOOTH LOW ENERGY SOFTWARE RELEASE NOTES Wednesday, 2 December 2020 Version 6.1 Table of Contents 1 Changes: 1.10.0 (Build 153) compared to 1.9.0 (Build 150) ______________________________________ 4 2 Changes: 1.9.0 (Build 150) compared to 1.8.0 (Build 143) _______________________________________ 5 3 Changes: 1.8.0 (Build 143) compared to 1.7.0 (Build 142) _______________________________________ 6 4 Changes: 1.7.0 (Build 142) compared to 1.6.0 (Build 140) _______________________________________ 7 5 Changes: 1.6.0 (Build 140) compared to 1.5.0 (Build 137) _______________________________________ 8 6 Changes: 1.5.0 (Build 137) compared to 1.4.2 (Build 130) _______________________________________ 9 7 Changes: 1.4.2 (Build 130) compared to 1.4.1 (Build 128) ______________________________________ 10 8 Changes: 1.4.1 (Build 128) compared to 1.4.0 (Build 127) ______________________________________ 11 9 Changes: 1.4.0 (Build 127) compared to 1.3.2 (Build 122) ______________________________________ 12 10 Changes: 1.3.2 (Build 122) compared to 1.3.1 (Build 119) _____________________________________ 13 11 Changes: 1.3.1 (Build 119) compared to 1.3.1 (Build 118) _____________________________________ 14 12 Changes: 1.3.1 (Build 118) compared to 1.3.0 Beta (Build 110) _________________________________ 15 13 Changes: 1.3.0 Beta (Build 110) compared to 1.2.2 (Build 100) _________________________________ 16 14 Changes: 1.2.2 (Build 100) compared to 1.2.1 (Build 91) ______________________________________ 17 15 Changes: 1.2.1 (Build 91) compared -

TS10: Ember Em35x NCP Host (STM32)

TS10 ® EMBER EM35X NCP HOST (STM32) MODULE TECHNICAL SPECIFICATION When combined with an Ember EM35x NCP Breakout Board, the Ember STM32 NCP Host Module offers a complete ZigBee wireless solution for development and deployment of a low-data-rate, low-power ZigBee application. The STM32 microprocessor is part of the two-layer (FR4-based) host module that connects to the EM35x NCP Breakout Board through the board-to-board connectors. This document provides the technical specification for the STM32 EM35x NCP Host Module. It describes the board- level interfaces as well as the key performance parameters. In addition, it provides the necessary information for developer to validate their application designs using the STM32 EM35x NCP Host Module. New in This Revision Document renumbering. Contents 1 STM32 Host Module Features ......................................................................................................................... 2 2 Components ................................................................................................................................................... 3 2.1 STM32 Microcontroller ............................................................................................................................. 4 2.2 EM35x NCP Breakout Board interface connector (J1-J2) .......................................................................... 4 2.3 JTAG Programming and Debug Connector (J3)........................................................................................ 6 2.4 Unused STM32 GPIO -

Ember Em35x Development Kit User Guide

UG113 EM34X DEVELOPMENT KIT USER’S GUIDE Contents 1 About This Guide ............................................................................................................................................ 4 1.1 Purpose ................................................................................................................................................... 4 1.2 Audience .................................................................................................................................................. 4 1.3 Documentation Conventions..................................................................................................................... 4 2 Introducing the EM34x Development Kit .......................................................................................................... 4 2.1 Overview .................................................................................................................................................. 4 2.2 Development Kit Contents ........................................................................................................................ 5 2.3 Hardware Requirements .......................................................................................................................... 5 2.4 Software Requirements ............................................................................................................................ 5 2.5 Hardware ................................................................................................................................................ -

Silicon Labs to Acquire Energy Micro, a Leader in Low Power ARM Cortex-Based Microcontrollers and Radios

June 7, 2013 Silicon Labs to Acquire Energy Micro, a Leader in Low Power ARM Cortex-Based Microcontrollers and Radios Companies' Combined Portfolios Enable the Internet of Things, Smart Energy and Portable Electronics AUSTIN, Texas & OSLO, Norway--(BUSINESS WIRE)-- Silicon Labs (Nasdaq: SLAB), a leader in high-performance, analog- intensive, mixed-signal ICs, today announced that it has signed a definitive agreement to acquire Energy Micro AS. Based in Oslo, Norway, the late-stage privately held company offers the industry's most power-efficient portfolio of 32-bit microcontrollers (MCUs) and is developing multi-protocol wireless RF solutions based on the industry-leading ARM® Cortex-M architecture. Energy Micro's energy-friendly MCU and radio solutions are designed to enable a broad range of power-sensitive applications for the Internet of Things (IoT), smart energy, home automation, security and portable electronics markets. This strategic acquisition accelerates Silicon Labs' growth opportunities and positions the company as the foremost innovator in energy-friendly embedded solutions. The growth of the IoT market, coupled with continued deployment of smart grid and smart energy infrastructure, is driving strong demand for energy-efficient processing and wireless connectivity technology to enable connected devices in which low-power capabilities are increasingly important. Industry experts predict that the number of connected devices for the IoT will top 15 billion nodes by 2015 and reach 50 billion nodes by 2020. Energy Micro's portfolio complements Silicon Labs' 32-bit Precision32™ MCU, Ember® ZigBee® and sub-GHz wireless products and targets a growing embedded market. The acquisition greatly expands Silicon Labs' MCU portfolio, adding nearly 250 ARM- based EFM32 Gecko MCU products ranging from extreme-low-power, small-footprint MCUs based on the ARM Cortex-M0+ core to higher-performance, energy-friendly MCUs powered by the Cortex-M4 core capable of DSP and floating-point operations. -

AN669: Integrating Silicon Labs Sim3xxxx Devices Into the Keil Μvision®

AN669 INTEGRATING SILICON LABS SiM3XXXX DEVICES INTO THE KEIL µVISION® IDE 1. Introduction This application note describes how to configure and use the Keil µVision® Integrated Development Environment (IDE) with Silicon Laboratories Precision32™ 32-bit microcontrollers (SiM3xxxx). 2. Key Points Key points described in this application note include: Generating a blank project in Keil µVision Configuring a µVision project for use with Silicon Laboratories SiM3xxxx devices Using the µVision IDE to build, download, run, and debug a project Using the System Viewer Windows and Debug (Print) Viewer 3. Creating a Project A project is necessary in order to build an example and download the firmware image to the MCU. To create a project in µVision: 1. Under the Project menu, select New µVision Project. After naming your new project, select SiLabs SiM3x Devices in the Select a CPU Data Base File dialog and click OK. 2. Expand the Silicon Laboratories data base to open a list of supported MCUs, select the appropriate MCU, and click OK. Figure 1. Selecting a SiM3x Device After creating your blank project, there will be an empty project in the Project Window. The next step is to configure the project options. Rev. 0.1 2/12 Copyright © 2012 by Silicon Laboratories AN669 AN669 4. Configuring Options for Target Specific configurations are required in order to communicate with the MCU using µVision. Some of the options are preconfigured after selecting a device under the Device tab, but some modifications are required. This section describes the required settings in all of the configuration tabs within the ProjectOptions for Target dialog; tabs that do not require any changes are explicitly noted. -

Si106x Development Kits User's Guide

Si106x-DK Si106X DEVELOPMENT KITS USER’S GUIDE 1. Kits Overview This user's guide describes the development kits of the Si106x Wireless MCU family. The latest version of this user guide is available online at http://www.silabs.com/products/wireless/wirelessmcu/Pages/default.aspx. Each kit contains two RF nodes based on the Wireless Motherboard to support evaluation and development of sub-GHz RF links with the different Wireless MCUs. WMCU pico board content of the different kits is listed in Table 1, and content common to all the kits is listed in Table 2. Table 1. WMCU Pico Boards of the Si106x Development Kits Qty Description Part Number Si1060 490 MHz Wireless MCU Development Kit 1060-490-DK 2 Si1060 490 MHz PICO Board 1060-PCE20C490 Si1060 915 MHz Wireless MCU Development Kit 1060-915-DK 2 Si1060 915 MHz PICO Board 1060-PCE20C915 Si1062 868 MHz Wireless MCU Development Kit 1062-868-DK 2 Si1062 868 MHz PICO Board 1062-PCE13D868 Si1064 434 MHz Wireless MCU Development Kit 1064-434-DK 2 Si1064 434 MHz PICO Board 1064-PCE10D434 Si1064 868 MHz Wireless MCU Development Kit 1064-868-DK 2 Si1064 868 MHz PICO Board 1064-PCE10D868 Si1064 915 MHz Wireless MCU Development Kit 1064-915-DK 2 Si1064 915 MHz PICO Board 1064-PCE10D915 Table 2. Common Kit Content Qty Description Part Number 2 Wireless Motherboard MSC-WMB912 2 USB cable (USBA-USB mini) 2 Antenna with SMA connection MSC-AT50-XXX 4 AA Battery 1 Si106x Development Kit User’s Guide Rev. 0.4 12/17 Copyright © 2017 by Silicon Laboratories Si106x-DK Si106x-DK 2. -

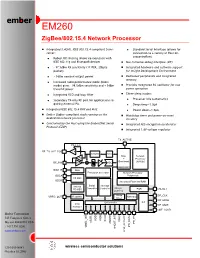

EM260 Zigbee/802.15.4 Network Processor

EM260 ZigBee/802.15.4 Network Processor Integrated 2.4GHz, IEEE 802.15.4-compliant trans- • Standard Serial Interface (allows for ceiver: connection to a variety of Host mi- crocontrollers) • Robust RX filtering allows co-existence with IEEE 802.11g and Bluetooth devices Non-intrusive debug interface (SIF) • - 97.5dBm RX sensitivity (1% PER, 20byte Integrated hardware and software support packet) for InSight Development Environment • + 3dBm nominal output power Dedicated peripherals and integrated memory • Increased radio performance mode (boost mode) gives – 98.5dBm sensitivity and + 5dBm Provides integrated RC oscillator for low transmit power power operation • Integrated VCO and loop filter Three sleep modes: • Secondary TX-only RF port for applications re- • Processor idle (automatic) quiring external PA. • Deep sleep—1.0μA Integrated IEEE 802.15.4 PHY and MAC • Power down—1.0μA Ember ZigBee-compliant stack running on the Watchdog timer and power-on-reset dedicated network processor circuitry Controlled by the Host using the EmberZNet Serial Integrated AES encryption accelerator Protocol (EZSP) Integrated 1.8V voltage regulator TX_ACTIVE PA select RF_TX_ALT_P,N PA SYNTH DAC MAC Network PA + Processor Baseband (XAP2b) RF_P,N LNA IF ADC PacketTrace BIAS_R Bias Encryption acclerator Network Processor OSCA Peripherals HF OSC OSCB Integrated Flash and RAM Internal Serial Interrupt Always RC-OSC Controller Controller POR nRESET powered Sleep Regulator Watchdog SIF_CLK VREG_OUT timer SIF_MISO IO Controller SIF Chip SIF_MOSI manager nSIF_LOAD Ember Corporation 343 Congress Street MOSI MISO SCLK SDBG nSSEL Boston MA 02210 USA nWAKE PTI_EN PTI_DATA +1 617.951.0200 nSSEL_INT nHOST_INT www.ember.com LINK_ACTIVITY 120-1003-000G wireless semiconductor solutions October 10, 2006 EM260 General Description The EM260 integrates a 2.4GHz, IEEE 802.15.4-compliant transceiver with a 16-bit network processor (XAP2b core) to run EmberZNet, the Ember ZigBee-compliant network stack. -

Zigbee 802.15.4 Network Processor

SN260 ZigBee® 802.15.4 network processor Features ■ Controlled by the Host using the EmberZNet™ Serial Protocol (EZSP) ■ Integrated 2.4GHz, IEEE 802.15.4-compliant – Standard SPI or UART interfaces allow for transceiver: connection to a variety of Host – Robust RX filtering allows co-existence microcontrollers with IEEE 802.11g and Bluetooth devices ■ Non-intrusive debug interface (SIF) – –99 dBm RX sensitivity (1% PER, 20-byte ■ packet) Integrated hardware and software support for InSight™ Development Environment – +2.5 dBm nominal output power ■ – Increased radio performance mode (Boost Provides integrated RC oscillator for low power mode) gives –100 dBm sensitivity and operation +4.5 dBm transmit power ■ Three sleep modes: – Integrated VCO and loop filter – Processor idle (automatic) – Secondary TX-only RF port for applications – Deep sleep—1.0µA requiring external PA. – Power down—1.0µA ■ Integrated IEEE 802.15.4 PHY and MAC ■ Watchdog timer and power-on-reset circuitry ■ Dedicated peripherals and integrated memory ■ Integrated AES encryption accelerator ■ Ember ZigBee®-compliant stack running on ■ Integrated 1.8V voltage regulator the dedicated network processor Obsolete Product(s) - Obsolete Product(s) March 2009 Rev 4 1/47 www.st.com 1 Contents SN260 Contents 1 Abbreviations and acronyms . 5 2 References . 6 3 General description . 7 4 Pin assignment . 8 5 Top-level functional description . 12 6 Functional description . 14 6.1 Receive (RX) path . 14 6.1.1 RX baseband . 14 6.1.2 RSSI and CCA . 14 6.2 Transmit (TX) path . 15 6.2.1 TX baseband . 15 6.2.2 TX_ACTIVE signal . 15 6.3 Integrated MAC module . -

Albert Shih ASSOCIATE

Albert Shih ASSOCIATE Litigation Palo Alto [email protected] 650-849-3022 FOCUS AREAS EXPERIENCE Albert Shih is an associate in the Palo Alto office of Wilson Sonsini Goodrich & Rosati, Litigation where his practice focuses on intellectual property litigation and counseling. He has litigated Patent Litigation more than 25 patent cases before federal district courts, the International Trade Commission, and Judicial Arbitration and Mediation Services, including a $31 million judgment obtained for his client in the field of telecommunication protocol. He also regularly advises clients on company intellectual property strategy, technology transactions, licensing negotiation, FRAND-rate setting for standard-essential patents, and patent prosecution matters. Prior to law school, Albert was a design engineer at Intel, where he taught courses at Intel University on chipset design. His field experience and knowledge allow him to understand and appreciate the unique business and technical perspective associated with leaders and innovators in the field of mobile telecommunication protocol, baseband processor, liquid crystal display, semiconductor fabrication, digital signal processors, digital receivers and tuners, image sensors, Internet security software, and various digital and analog circuit designs. Educated in Taiwan and Singapore in his early years, Albert is fluent in Mandarin Chinese. CREDENTIALS Education J.D., Loyola Law School, Los Angeles B.S., Electrical Engineering, University of Michigan, Ann Arbor Associations and Memberships Member, American Bar Association, Intellectual Property Section Member, American Intellectual Property Law Association Member, Asia Pacific Intellectual Property Association Member, International Trade Commission Trial Lawyer Association Honors Named to the 2015-2018 editions of the "Rising Stars" list published by Northern California Super Lawyers Admissions State Bar of California U.S. -

UG103.4: HAL Fundamentals

UG103.4: HAL Fundamentals Silicon Labs HAL (Hardware Abstraction Layer) is program code between a system’s hardware and its software that provides a KEY POINTS consistent interface for applications that can run on several differ- • Provides information on how the HAL is ent hardware platforms. The HAL is designed for developers us- organized, including naming conventions, ing EmberZNet PRO with the EFR32MG family of products. API files, and directory structure. • Includes an overview of each of the main Silicon Labs’ Fundamentals series covers topics that project managers, application de- subsections of the HAL functionality. signers, and developers should understand before beginning to work on an embedded • Describes how to adapt the HAL to your networking solution using Silicon Labs chips, networking stacks such as EmberZNet specific hardware and application PRO or Silicon Labs Bluetooth®, and associated development tools. The documents requirements. can be used as a starting place for anyone needing an introduction to developing wire- less networking applications, or who is new to the Silicon Labs development environ- ment. silabs.com | Building a more connected world. Rev. 1.4 UG103.4: HAL Fundamentals Introduction 1. Introduction The Hardware Abstraction Layer (HAL) is program code between a system’s hardware and its software that provides a consistent inter- face for applications that can run on several different hardware platforms. To take advantage of this capability, applications should ac- cess hardware through the API provided by the HAL, rather than directly. Then, when you move to new hardware, you only need to update the HAL. In some cases, due to extreme differences in hardware, the HAL API may also change slightly to accommodate the new hardware. -

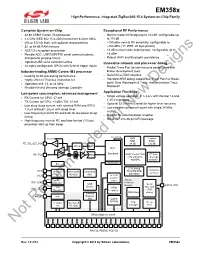

Em358x High-Performance, Integrated Zigbee/802.15.4 System-On-Chip Family

EM358x High-Performance, Integrated ZigBee/802.15.4 System-on-Chip Family Complete System-on-Chip Exceptional RF Performance - 32-bit ARM® Cortex -M3 processor - Normal mode link budget up to 103 dB; configurable up - 2.4 GHz IEEE 802.15.4-2003 transceiver & lower MAC to 110 dB - 256 or 512 kB flash, with optional read protection - –100 dBm normal RX sensitivity; configurable to - 32 or 64 kB RAM memory –102 dBm (1% PER, 20 byte packet) - AES128 encryption accelerator - +3 dB normal mode output power; configurable up to - Flexible ADC, UART/SPI/TWI serial communications, +8 dBm and general purpose timers - Robust Wi-Fi and Bluetooth coexistence Optional USB serial communications - Innovative network and processor debug 24 highly configurable GPIOs with Schmitt trigger inputs - - Packet Trace Port for non-intrusive packet trace with Industry-leading ARM® Cortex -M3 processor Ember development tools - Leading 32-bit processing performance - Serial Wire/JTAG interface - Highly efficient Thumb-2 instruction set - Standard ARM debug capabilities: Flash Patch & Break- - Operation at 6, 12, or 24 MHz point; Data Watchpoint & Trace; InstrumentationDesigns Trace Macrocell - Flexible Nested Vectored Interrupt Controller Application Flexibility Low power consumption, advanced management - Single voltage operation: 2.1–3.6 V with internal 1.8 and - RX Current (w/ CPU): 27 mA 1.25 V regulators - TX Current (w/ CPU, +3 dBm TX): 31 mA - Optional 32.768 kHz crystal for higher timer accuracy - Low deep sleep current, with retained RAM and GPIO: - Low -

Meshconnect™ EM357 Mini Modules ZICM357SP0, ZICM357SP2 Embertm EM357 Transceiver Based Modules

DATASHEET MeshConnect™ EM357 Mini Modules ZICM357SP0, ZICM357SP2 EmberTM EM357 Transceiver Based Modules Integrated Transceiver Modules for ZigBee / IEEE 802.15.4 Development Kit available: ZICM-EM35X-DEV-KIT-2 DESCRIPTION MeshConnect™ The MeshConnect™ EM357 Mini Modules from EM357 Mini Modules California Eastern Laboratories (CEL) combine high • 192 kB FLASH • 12 kB SRAM performance RF solutions with the market's premier ® ® • 32-bit ARM Cortex™-M3 ZigBee stack. Available in low and high output • Up to 23 GPIO Pins power options (+8dBm and +20dBm), these modules • SPI (Master/Slave), TWI, UART can accommodate variable range and performance • Timers, Serial Wire/JTAG Interface • 5-channel 14-bit ADC requirements. The mini module footprint makes them suitable for a wide range of ZigBee applications. The ZICM357SP0 ZICM357SP2 MeshConnect EM357 Mini Modules are certified and Tx: +8dBm +20dBm qualified, enabling customers to accelerate time to Rx: -100dBm -103dBm Link Budget: +108dB +123dB market by greatly reducing the design and certification phases of development. FEATURES • High RF Performance: • Mini Footprint: CEL's MeshConnect EM357 Mini Modules Up to 123dB RF Link Budget - 0.940" x 0.655" RX Sensitivity: (ZICM357SP0 and ZICM357SP2) are based on the (23.9mm x 16.6mm) -100dBm (ZICM357SP0) Ember EM357 ZigBee compliant SoC radio IC. The • -103dBm (ZICM357SP2) Antenna Options IC is a single-chip solution, compliant with ZigBee 1) Integrated PCB Trace Antenna • Data Rate: 250kbps specifications and IEEE 802.15.4, a complete or • Advanced Cortex-M3 Processor wireless solution for all ZigBee applications. The 2) RF Port for External Antenna • Advanced Power Management • IC consists of an RF transceiver with the baseband Supports Mesh Networks • 16 RF Channels • modem, a hardwired MAC and an embedded 32- AES Encryption • Industry's Premier ZigBee Pro • bit ARM® Cortex™-M3 microcontroller with internal FCC, CE and IC Certifications Stack: EmberZNet PRO™ • RAM (12kB) and Flash (192kB) memory.