Stage, Time Interleaved Sub – Ranging Analog to Digital Converter Using MATLAB

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Victorian Popular Science and Deep Time in “The Golden Key”

“Down the Winding Stair”: Victorian Popular Science and Deep Time in “The Golden Key” Geoffrey Reiter t is sometimes tempting to call George MacDonald’s fantasies “timeless”I and leave it at that. Such is certainly the case with MacDonald’s mystical fairy tale “The Golden Key.” Much of the criticism pertaining to this work has focused on its more “timeless” elements, such as its intrinsic literary quality or its philosophical and theological underpinnings. And these elements are not only important, they truly are the most fundamental elements needed for a full understanding of “The Golden Key.” But it is also important to remember that MacDonald did not write in a vacuum, that he was in fact interested in and engaged with many of the pressing issues of his day. At heart always a preacher, MacDonald could not help but interact with these issues, not only in his more openly didactic realistic novels, but even in his “timeless” fantasies. In the Victorian period, an era of discovery and exploration, the natural sciences were beginning to come into their own as distinct and valuable sources of knowledge. John Pridmore, examining MacDonald’s view of nature, suggests that MacDonald saw it as serving a function parallel to the fairy tale or fantastic story; it may be interpreted from the perspective of Christian theism, though such an interpretation is not necessary (7). Björn Sundmark similarly argues that in his works “MacDonald does not contradict science, nor does he press a theistic interpretation onto his readers” (13). David L. Neuhouser has concluded more assertively that while MacDonald was certainly no advocate of scientific pursuits for their own sake, he believed science could be of interest when examined under the aegis of a loving God (10). -

Geochronology Database for Central Colorado

Geochronology Database for Central Colorado Data Series 489 U.S. Department of the Interior U.S. Geological Survey Geochronology Database for Central Colorado By T.L. Klein, K.V. Evans, and E.H. DeWitt Data Series 489 U.S. Department of the Interior U.S. Geological Survey U.S. Department of the Interior KEN SALAZAR, Secretary U.S. Geological Survey Marcia K. McNutt, Director U.S. Geological Survey, Reston, Virginia: 2010 For more information on the USGS—the Federal source for science about the Earth, its natural and living resources, natural hazards, and the environment, visit http://www.usgs.gov or call 1-888-ASK-USGS For an overview of USGS information products, including maps, imagery, and publications, visit http://www.usgs.gov/pubprod To order this and other USGS information products, visit http://store.usgs.gov Any use of trade, product, or firm names is for descriptive purposes only and does not imply endorsement by the U.S. Government. Although this report is in the public domain, permission must be secured from the individual copyright owners to reproduce any copyrighted materials contained within this report. Suggested citation: T.L. Klein, K.V. Evans, and E.H. DeWitt, 2009, Geochronology database for central Colorado: U.S. Geological Survey Data Series 489, 13 p. iii Contents Abstract ...........................................................................................................................................................1 Introduction.....................................................................................................................................................1 -

Career Stage, Time Spent on the Road, and Truckload Driver Attitudes

CAREER STAGE, TIME SPENT ON THE ROAD, AND TRUCKLOAD DRIVER ATTITUDES James C. McElroy Julene M. Rodriguez Gene C. Griffin Paula C. Morrow Michael G. Wilson UGPTI Staff Paper No. 113 May 1993 Career Stage, Time Spent on the Road, And Truckload Driver Attitudes1 James C. McElroy, Department of Management Iowa State University Julene M. Rodriguez and Gene C. Griffin Upper Great Plains Transportation Institute North Dakota State University Paula C. Morrow Industrial Relations Center Iowa State University Michael G. Wilson Iowa State University Address correspondence to: James C. McElroy, Chair Departments of Management, Marketing, and Transportation & Logistics Iowa State University 300 Carver Hall Ames, Iowa 50011 1The authors would like to thank their respective institutions for support, Drs. Ben Allen, Michael Crum, Richard Poist, and David Shrock for their comments and suggestions and Brenda Lantz for her assistance with data analysis. TABLE OF CONTENTS Page CAREER STAGE, TIME SPENT ON THE ROAD, AND TRUCKLOAD DRIVER ATTITUDES ......................................... 1 Determinants of Work-Related Attitudes ......................................... 2 Propositions ................................................................ 3 Method ................................................................... 3 Sample ................................................................ 3 Independent Variables ...................................................... 4 Dependent Variables ....................................................... 4 Research -

It's About Time: Opportunities & Challenges for U.S

I t’s About Time: Opportunities & Challenges for U.S. Geochronology About Time: Opportunities & Challenges for t’s It’s About Time: Opportunities & Challenges for U.S. Geochronology 222508_Cover_r1.indd 1 2/23/15 6:11 PM A view of the Bowen River valley, demonstrating the dramatic scenery and glacial imprint found in Fiordland National Park, New Zealand. Recent innovations in geochronology have quantified how such landscapes developed through time; Shuster et al., 2011. Photo taken Cover photo: The Grand Canyon, recording nearly two billion years of Earth history (photo courtesy of Dr. Scott Chandler) from near the summit of Sheerdown Peak (looking north); by J. Sanders. 222508_Cover.indd 2 2/21/15 8:41 AM DEEP TIME is what separates geology from all other sciences. This report presents recommendations for improving how we measure time (geochronometry) and use it to understand a broad range of Earth processes (geochronology). 222508_Text.indd 3 2/21/15 8:42 AM FRONT MATTER Written by: T. M. Harrison, S. L. Baldwin, M. Caffee, G. E. Gehrels, B. Schoene, D. L. Shuster, and B. S. Singer Reviews and other commentary provided by: S. A. Bowring, P. Copeland, R. L. Edwards, K. A. Farley, and K. V. Hodges This report is drawn from the presentations and discussions held at a workshop prior to the V.M. Goldschmidt in Sacramento, California (June 7, 2014), a discussion at the 14th International Thermochronology Conference in Chamonix, France (September 9, 2014), and a Town Hall meeting at the Geological Society of America Annual Meeting in Vancouver, Canada (October 21, 2014) This report was provided to representatives of the National Science Foundation, the U.S. -

End Times Timeline CCC August 30, 2020 Visuals

End Times Timeline CCC August 30, 2020 Visuals – Across the stage signage. Four signs representing each age. Three cutouts – One of Rapture, one of Second Coming, one of Zombie Introduction – Quick show of hands. How many people have ever found end times stuff to be Confusing? If your neighbor just raised his/her hand, say to them “I knew you were confused.” How would you like to have a quick handle on what is going to happen when Jesus comes back again? Today, I am going to try to make that happen in under 40 minutes. So lets pray. Seriously… Pray OK, so the end times are so crazy partly because of terminology. Partly because of theological positions. Partly because the Bible is crystal clear on some things – like Jesus is coming back. Unclear on other things – like what is the order of events. And downright intentionally obtuse about other things – like when the rapture will take place. So I am going to run after this with a really clear statement up front. “I might be wrong.” I know… a shocking thing for a pastor to admit. Now raise your eyebrows and turn to the person next to you and say – he might be wrong. (really, I wont do that all message). I have studied this for 30 years now and changed my mind a few times. I may change it again in five years. I may have never been right on some aspects – so I’ll do my best to share multiple views and my personal opinion… but just so you know that I know that this is complex stuff that will come down in the future – and I am approaching it all with humility – and I’ll let you know if I change my mind. -

A Chronology for Late Prehistoric Madagascar

Journal of Human Evolution 47 (2004) 25e63 www.elsevier.com/locate/jhevol A chronology for late prehistoric Madagascar a,) a,b c David A. Burney , Lida Pigott Burney , Laurie R. Godfrey , William L. Jungersd, Steven M. Goodmane, Henry T. Wrightf, A.J. Timothy Jullg aDepartment of Biological Sciences, Fordham University, Bronx NY 10458, USA bLouis Calder Center Biological Field Station, Fordham University, P.O. Box 887, Armonk NY 10504, USA cDepartment of Anthropology, University of Massachusetts-Amherst, Amherst MA 01003, USA dDepartment of Anatomical Sciences, Stony Brook University, Stony Brook NY 11794, USA eField Museum of Natural History, 1400 S. Roosevelt Rd., Chicago, IL 60605, USA fMuseum of Anthropology, University of Michigan, Ann Arbor, MI 48109, USA gNSF Arizona AMS Facility, University of Arizona, Tucson AZ 85721, USA Received 12 December 2003; accepted 24 May 2004 Abstract A database has been assembled with 278 age determinations for Madagascar. Materials 14C dated include pretreated sediments and plant macrofossils from cores and excavations throughout the island, and bones, teeth, or eggshells of most of the extinct megafaunal taxa, including the giant lemurs, hippopotami, and ratites. Additional measurements come from uranium-series dates on speleothems and thermoluminescence dating of pottery. Changes documented include late Pleistocene climatic events and, in the late Holocene, the apparently human- caused transformation of the environment. Multiple lines of evidence point to the earliest human presence at ca. 2300 14C yr BP (350 cal yr BC). A decline in megafauna, inferred from a drastic decrease in spores of the coprophilous fungus Sporormiella spp. in sediments at 1720 G 40 14C yr BP (230e410 cal yr AD), is followed by large increases in charcoal particles in sediment cores, beginning in the SW part of the island, and spreading to other coasts and the interior over the next millennium. -

Guide-For-U.S. Delegates-To-ISO-And-IEC-Meetings

GUIDE FOR U.S. DELEGATES to ISO and IEC meetings Guide for U.S. Delegates to ISO and IEC Meetings 1 TABLE OF CONTENTS LETTER FROM ANSI’S PRESIDENT & CEO 3 INTRODUCTION: YOU THE DELEGATE 4 THE MEETING: HOW TO PREPARE, PARTICIPATE, AND FOLLOW UP 6 Preparing for the Meeting 6 Participating in the Meeting 7 Extending Invitations for Meetings in the United States 8 Accepting Secretariats 9 After the Meeting 10 WHO IS INVOLVED IN ISO AND IEC ACTIVITIES? 11 Management of ISO and the IEC 11 Membership 11 The Role of ANSI 11 Technical Committees, Subcommittees, Project Committees, and System Committees 11 ISO/IEC JTC 1 12 U.S. Technical Advisory Groups 12 Working Groups 13 Liaisons 13 HOW ISO/IEC STANDARDS ARE DEVELOPED 14 Typical Stages of Development 14 Other Deliverables 17 Maintenance 17 Other Considerations 18 CONCLUSION 19 APPENDIX A: ORGANIZATIONAL INFORMATION 21 APPENDIX B: COMMONLY USED ACRONYMS 24 APPENDIX C: ADDITIONAL RESOURCES 27 APPENDIX D: CONTACTS 28 APPENDIX E: ORGANIZATION STRUCTURES 29 Guide for U.S. Delegates to ISO and IEC Meetings 2 LETTER FROM ANSI’S PRESIDENT & CEO: S. JOE BHATIA Congratulations on your appointment as a delegate to a technical meeting of the International Organization for Standardization (ISO) or the International Electrotechnical Commission (IEC). You have been chosen for your expertise in a given field along with your ability to effectively present the U.S. viewpoint as part of a delegation to an international standards forum. On behalf of the American National Standards Institute (ANSI), I would like to express our appreciation to you and the company or organization that supports your participation in international standardization activities. -

Paleogeographic Maps Earth History

History of the Earth Age AGE Eon Era Period Period Epoch Stage Paleogeographic Maps Earth History (Ma) Era (Ma) Holocene Neogene Quaternary* Pleistocene Calabrian/Gelasian Piacenzian 2.6 Cenozoic Pliocene Zanclean Paleogene Messinian 5.3 L Tortonian 100 Cretaceous Serravallian Miocene M Langhian E Burdigalian Jurassic Neogene Aquitanian 200 23 L Chattian Triassic Oligocene E Rupelian Permian 34 Early Neogene 300 L Priabonian Bartonian Carboniferous Cenozoic M Eocene Lutetian 400 Phanerozoic Devonian E Ypresian Silurian Paleogene L Thanetian 56 PaleozoicOrdovician Mesozoic Paleocene M Selandian 500 E Danian Cambrian 66 Maastrichtian Ediacaran 600 Campanian Late Santonian 700 Coniacian Turonian Cenomanian Late Cretaceous 100 800 Cryogenian Albian 900 Neoproterozoic Tonian Cretaceous Aptian Early 1000 Barremian Hauterivian Valanginian 1100 Stenian Berriasian 146 Tithonian Early Cretaceous 1200 Late Kimmeridgian Oxfordian 161 Callovian Mesozoic 1300 Ectasian Bathonian Middle Bajocian Aalenian 176 1400 Toarcian Jurassic Mesoproterozoic Early Pliensbachian 1500 Sinemurian Hettangian Calymmian 200 Rhaetian 1600 Proterozoic Norian Late 1700 Statherian Carnian 228 1800 Ladinian Late Triassic Triassic Middle Anisian 1900 245 Olenekian Orosirian Early Induan Changhsingian 251 2000 Lopingian Wuchiapingian 260 Capitanian Guadalupian Wordian/Roadian 2100 271 Kungurian Paleoproterozoic Rhyacian Artinskian 2200 Permian Cisuralian Sakmarian Middle Permian 2300 Asselian 299 Late Gzhelian Kasimovian 2400 Siderian Middle Moscovian Penn- sylvanian Early Bashkirian -

Market Simulation – Summer 2021 Release

Market Simulation – Summer 2021 Release Anshuman Vaidya Market Simulation Coordinator July 29, 2021 COPYRIGHT © 2016 by California ISO. All Rights Reserved. Recordings Calls and webinars are recorded for stakeholder convenience, allowing those who are unable to attend to listen to the recordings after the meetings. The recordings will be publicly available on the ISO web page for a limited time following the meetings. The recordings, and any related transcriptions, should not be reprinted without the ISO’s permission. COPYRIGHT © 2016 by California ISO. All Rights Reserved. Page 2 Agenda • Summer 2021 Release MAP Stage Availability • Summer 2021 Release Market Simulation Initiatives & Timelines • Initiatives – Summer 2021 readiness • Summer 2021 - System Interface Changes • ADS AS Test • ADS Infrastructure Decommission • Application Delivery Resiliency - OASIS • Fall 2021 Release Preview • Next Steps COPYRIGHT © 2016 by California ISO. All Rights Reserved. Page 3 Summer 2021 Release MAP Stage Availability • Refer to MAP Stage portal https://portalmap.caiso.com for system availability information • Current MAP Stage Scheduled Maintenance – Friday, 7/30: • ADS Infrastructure Decommission; :447 will no longer be available • OASIS infrastructure update - no interruption • MAP Stage Weekly Maintenance Window – Friday COPYRIGHT © 2016 by California ISO. All Rights Reserved. Page 4 Summer 2021 Release Market Simulation Initiatives & Timelines Summer 2021 Release Start Start Date End Structured Go Live Date Initiatives Date (Trade Date) Date Simulation Start (Trade Date) Summer 2021 Release 04/26/21 04/26/21 07/31/21 05/10/21 Market Simulation Summer 2021 readiness 7/27 - 8a Export, wheeling, and load 8/4 7/30, 8/3- 8b scheduling priorities Market Simulation Plan: http://www.caiso.com/Documents/MarketSimulationPlan-Summer2021Release.pdf COPYRIGHT © 2016 by California ISO. -

INTERNATIONAL CHRONOSTRATIGRAPHIC CHART International Commission on Stratigraphy V 2020/03

INTERNATIONAL CHRONOSTRATIGRAPHIC CHART www.stratigraphy.org International Commission on Stratigraphy v 2020/03 numerical numerical numerical numerical Series / Epoch Stage / Age Series / Epoch Stage / Age Series / Epoch Stage / Age GSSP GSSP GSSP GSSP EonothemErathem / Eon System / Era / Period age (Ma) EonothemErathem / Eon System/ Era / Period age (Ma) EonothemErathem / Eon System/ Era / Period age (Ma) Eonothem / EonErathem / Era System / Period GSSA age (Ma) present ~ 145.0 358.9 ±0.4 541.0 ±1.0 U/L Meghalayan 0.0042 Holocene M Northgrippian 0.0082 Tithonian Ediacaran L/E Greenlandian 0.0117 152.1 ±0.9 ~ 635 U/L Upper Famennian Neo- 0.129 Upper Kimmeridgian Cryogenian M Chibanian 157.3 ±1.0 Upper proterozoic ~ 720 0.774 372.2 ±1.6 Pleistocene Calabrian Oxfordian Tonian 1.80 163.5 ±1.0 Frasnian 1000 L/E Callovian Quaternary 166.1 ±1.2 Gelasian 2.58 382.7 ±1.6 Stenian Bathonian 168.3 ±1.3 Piacenzian Middle Bajocian Givetian 1200 Pliocene 3.600 170.3 ±1.4 387.7 ±0.8 Meso- Zanclean Aalenian Middle proterozoic Ectasian 5.333 174.1 ±1.0 Eifelian 1400 Messinian Jurassic 393.3 ±1.2 Calymmian 7.246 Toarcian Devonian Tortonian 182.7 ±0.7 Emsian 1600 11.63 Pliensbachian Statherian Lower 407.6 ±2.6 Serravallian 13.82 190.8 ±1.0 Lower 1800 Miocene Pragian 410.8 ±2.8 Proterozoic Neogene Sinemurian Langhian 15.97 Orosirian 199.3 ±0.3 Lochkovian Paleo- Burdigalian Hettangian proterozoic 2050 20.44 201.3 ±0.2 419.2 ±3.2 Rhyacian Aquitanian Rhaetian Pridoli 23.03 ~ 208.5 423.0 ±2.3 2300 Ludfordian 425.6 ±0.9 Siderian Mesozoic Cenozoic Chattian Ludlow -

An Amillennial Response to a Premillennial View of Isaiah 65:20

JETS 61.3 (2018): 461–92 AN AMILLENNIAL RESPONSE TO A PREMILLENNIAL VIEW OF ISAIAH 65:20 G. K. BEALE* Abstract: This essay argues that Isa 65:20 is not about a temporary reversible millennium in which there is actual death but about the eternal irreversible reality of there being no untime- ly death in the everlasting new creation. I adduce seven main lines of argument in favor of this: (1) discussion of a translational problem in 65:20, which could support premillennialism or could fit into an amillennial view; (2) the eternal new creation context of Isa 65:17–19 and 65:21–25 points to the probability that 65:20 is also about the eternal new creation; (3) the use of Genesis 3 in Isaiah 65, which points to an eternal new creation context; (4) the eternal new creation context of Isa 65:17–25 is supported further by its use of Isa 25:7–10, which is about there being no death any longer in the new, eternal age; (5) arguments favoring a figura- tive view of Isa 65:20; (6) the use of Isaiah in Rev 21:1–22:4 is figurative, thus pointing to Isa 65:20 being a depiction of the irreversible, eternal new creation; (7) the irreversible nature of eschatology itself favors the conclusion that Isa 65:20 is not about a temporary, eschatologi- cal millennial state but about the eternal new heavens and earth. Key Words: eschatology, inaugurated eschatology, premillennialism, amillennialism, new cre- ation Isaiah 65:20 says: “No longer will there be from there an infant who lives but a few days, or an old man who does not live out his days; for the youth will die at the age of one hundred and the one who does not reach the age of one hundred will be thought accursed.”1 This essay had its stimulus in a Westminster Theological Semi- nary panel discussion on eschatology at the Gospel Coalition conference in Orlan- do, FL in the spring of 2015. -

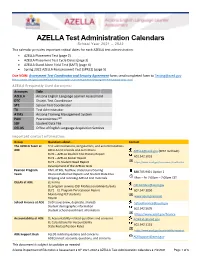

AZELLA Test Administration Calendars School Year 2021-2022

AZELLA Test Administration Calendars School Year 2021 – 2022 This calendar provides important critical dates for each AZELLA test administration. • AZELLA Placement Test (page 2) • AZELLA Placement Test Cycle Dates (page 3) • AZELLA Stand Alone Field Test (SAFT) (page 4) • Spring 2022 AZELLA Reassessment Test (SPR22) (page 5) Due NOW: Assessment Test Coordinator and Security Agreement form; send completed form to [email protected] (https://www.azed.gov/sites/default/files/2021/04/DTC%20Test%20Security%20Agreement%202021-2022.docx) AZELLA Frequently Used Acronyms: Acronym Title AZELLA Arizona English Language Learner Assessment DTC District Test Coordinator STC School Test Coordinator TA Test Administrator ATMS Arizona Training Management System PAN PearsonAccessnext SDF Student Data File OELAS Office of English Language Acquisition Services Important contact information: Group Questions about… Contact The AZELLA Team at Test administrations, irregularities, and accommodations ADE AZELLA test records and corrections [email protected] (BEST method!) EL70 – AZELLA Student Test History Report 602.542.5031 EL72 – AZELLA Roster Report EL73 – EL Student Need Report https://www.azed.gov/assessment/azella-dtcs Development of the AZELLA tests PAN, ATMS, TestNav, Understand Scoring Pearson Program 888.705.9421 Option 2 Team Pearson Published Reports and Student Data Files Shipping and receiving AZELLA test materials Mon – Fri 7:00am – 7:00pm CST OELAS at ADE EL Forms EL program services (SEI Models) enrollments/exits [email protected] EL71 – EL Program