Open On-Chip Debugger: Openocd User's Guide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

NXP Powerpoint Template Confidential 16:9 Widescreen

NXP MCU PRODUCT UPDATE & ROADMAP Q4 2016 NXP’S MCU POWERHOUSE PORTFOLIO 1 PUBLIC USE NXP Microcontrollers Business Line Why Customers Choose Us Applications • Comprehensive portfolio supporting the diverse IoT landscape Wearable / Healthcare • Fitness & Wireless Healthcare • Extensive software and development environment • Diabetes & Cardiac Care • Diagnostics & therapy • Industry leading customer support, quality, and longevity Home & Building Automation • Broad ecosystem of partners enabling system solutions • Smart meters & grid • Integrated wireless connectivity solutions • Ease of use solutions tailored for mass market • Home energy control Smart Accessories • Game controllers and consoles Example Customers • Wearable computing • eReaders, tablets, portable navigation Vehicle Networking & Information • Infotainment, software define radio • Navigation systems, E-call Home Appliances • Energy efficient refrigerators, dishwashers • Human-machine interface • Connected appliances Industrial Controls & Factory Automation • Machine-to-machine • Motor control Products • Industrial networking Kinetis & LPC 32-bit i.MX ARM® Applications 2 ARMPUBLIC® Microcontrollers USE Processors NXP MCUs - Powerhouse Portfolio ARM Expertise Broadest licensee of ARM cores in industry Most scalable portfolio with Expansive Portfolio optimized performance and capabilities Development Tools Best-in-class hardware platforms and software solutions Ecosystem Leadership Industry leading partnerships for innovation and differentiation Experienced global support team -

Fill Your Boots: Enhanced Embedded Bootloader Exploits Via Fault Injection and Binary Analysis

IACR Transactions on Cryptographic Hardware and Embedded Systems ISSN 2569-2925, Vol. 2021, No. 1, pp. 56–81. DOI:10.46586/tches.v2021.i1.56-81 Fill your Boots: Enhanced Embedded Bootloader Exploits via Fault Injection and Binary Analysis Jan Van den Herrewegen1, David Oswald1, Flavio D. Garcia1 and Qais Temeiza2 1 School of Computer Science, University of Birmingham, UK, {jxv572,d.f.oswald,f.garcia}@cs.bham.ac.uk 2 Independent Researcher, [email protected] Abstract. The bootloader of an embedded microcontroller is responsible for guarding the device’s internal (flash) memory, enforcing read/write protection mechanisms. Fault injection techniques such as voltage or clock glitching have been proven successful in bypassing such protection for specific microcontrollers, but this often requires expensive equipment and/or exhaustive search of the fault parameters. When multiple glitches are required (e.g., when countermeasures are in place) this search becomes of exponential complexity and thus infeasible. Another challenge which makes embedded bootloaders notoriously hard to analyse is their lack of debugging capabilities. This paper proposes a grey-box approach that leverages binary analysis and advanced software exploitation techniques combined with voltage glitching to develop a powerful attack methodology against embedded bootloaders. We showcase our techniques with three real-world microcontrollers as case studies: 1) we combine static and on-chip dynamic analysis to enable a Return-Oriented Programming exploit on the bootloader of the NXP LPC microcontrollers; 2) we leverage on-chip dynamic analysis on the bootloader of the popular STM8 microcontrollers to constrain the glitch parameter search, achieving the first fully-documented multi-glitch attack on a real-world target; 3) we apply symbolic execution to precisely aim voltage glitches at target instructions based on the execution path in the bootloader of the Renesas 78K0 automotive microcontroller. -

Fog Gateways:The Cornerstone of Iot Security

WHITE PAPER Fog Gateways: The Cornerstone of IoT Security Fog Gateways: The Cornerstone of IoT Security By Nicholas Cravotta The IoT offers tremendous value, safety. Utilities can dynamically change rates and shift loads—thus preventing overinvestment in power but also introduces major security generation. IoT-based medical devices can monitor challenges. Connecting previously offline patients continuously to identify trends and alert systems increases the attack surface for hackers— caregivers before an emergency arises. and the diversity of these systems makes it difficult to But all these benefits depend on secure data flow. deploy and manage consistent security. If the network is compromised, the result can be The nature of internal networks—such as the automation disastrous. For industrial applications, the cost could be networks that connect factory machinery—add to the the shutdown of operations or equipment damage. In a problem. Legacy networks provide minimal authorization, utilities environment, invalid data could result in black- little authentication, and not enough encryption. There outs and lost revenue. For retail applications, security is often no protection against intrusion, unauthorized breaches could halt sales and expose customer data. reconfiguration of edge equipment, or DDoS attacks. If an attacker gains access to these unsecure networks, the What Makes IoT Security Different entire organization can be at risk. In some ways, security concerns are nothing new. Most Fog computing can address these security issues today organizations already have security precautions in place and help you prepare for new challenges on the horizon. to protect sensitive IT systems and physical assets. But Fog gateways provide secure connectivity to local equip- the IoT introduces new threats that can catch businesses ment, intelligent data processing, and end-to-end off guard. -

Systemverilog

SystemVerilog ● Industry's first unified HDVL (Hw Description and Verification language (IEEE 1800) ● Major extension of Verilog language (IEEE 1364) ● Targeted primarily at the chip implementation and verification flow ● Improve productivity in the design of large gate-count, IP- based, bus-intensive chips Sources and references 1. Accellera IEEE SystemVerilog page http://www.systemverilog.com/home.html 2. “Using SystemVerilog for FPGA design. A tutorial based on a simple bus system”, Doulos http://www.doulos.com/knowhow/sysverilog/FPGA/ 3. “SystemVerilog for Design groups”, Slides from Doulos training course 4. Various tutorials on SystemVerilog on Doulos website 5. “SystemVerilog for VHDL Users”, Tom Fitzpatrick, Synopsys Principal Technical Specialist, Date04 http://www.systemverilog.com/techpapers/date04_systemverilog.pdf 6. “SystemVerilog, a design and synthesis perspective”, K. Pieper, Synopsys R&D Manager, HDL Compilers 7. Wikipedia Extensions to Verilog ● Improvements for advanced design requirements – Data types – Higher abstraction (user defined types, struct, unions) – Interfaces ● Properties and assertions built in the language – Assertion Based Verification, Design for Verification ● New features for verification – Models and testbenches using object-oriented techniques (class) – Constrained random test generation – Transaction level modeling ● Direct Programming Interface with C/C++/SystemC – Link to system level simulations Data types: logic module counter (input logic clk, ● Nets and Variables reset, ● enable, Net type, -

Porting the Arduino Library to the Cypress Psoc in Psoc Creator

Porting the Arduino Library to the Cypress PSoC in PSoC Creator Matt Durak November 11, 2011 Design Team 1 Abstract Arduino, the open-source electronic platform is a useful tool to hobbyists in building embedded systems. It provides an easy to use library which includes components to work with an Ethernet board, called the Ethernet shield. PSoC is a programmable system-on-chip made by Cypress Semiconductor. It is a very flexible platform which includes an ARM Cortex M3 processor. This application note includes the steps necessary to port parts of the Arduino library to the PSoC in order to use Arduino software and hardware, known as shields, with the PSoC. The note will cover many issues which must be overcome in porting this software. Keywords PSoC, Arduino, C++, C, Library, Software, Porting, PSoC Creator, Ethernet shield Introduction Arduino Library The Arduino is an open-source electronics hardware platform that is designed primarily for students and hobbyists (1). Arduino provides the schematics to build the hardware, as well as kits which can be pre- assembled or just include the parts. This application note will focus on the software for Arduino. Arduino has its own open-source development environment based on Wiring, a platform for programming electronics (2). The software library used by Arduino is written in C++ and is also open-source and freely available (3). This library is composed of a low layer which communicates directly with hardware registers and provides an abstraction for programmers to set whether a pin is an input or an output and to read and write to those pins. -

Gotcha Again More Subtleties in the Verilog and Systemverilog Standards That Every Engineer Should Know

Gotcha Again More Subtleties in the Verilog and SystemVerilog Standards That Every Engineer Should Know Stuart Sutherland Sutherland HDL, Inc. [email protected] Don Mills LCDM Engineering [email protected] Chris Spear Synopsys, Inc. [email protected] ABSTRACT The definition of gotcha is: “A misfeature of....a programming language...that tends to breed bugs or mistakes because it is both enticingly easy to invoke and completely unexpected and/or unreasonable in its outcome. A classic gotcha in C is the fact that ‘if (a=b) {code;}’ is syntactically valid and sometimes even correct. It puts the value of b into a and then executes code if a is non-zero. What the programmer probably meant was ‘if (a==b) {code;}’, which executes code if a and b are equal.” (http://www.hyperdictionary.com/computing/gotcha). This paper documents 38 gotchas when using the Verilog and SystemVerilog languages. Some of these gotchas are obvious, and some are very subtle. The goal of this paper is to reveal many of the mysteries of Verilog and SystemVerilog, and help engineers understand the important underlying rules of the Verilog and SystemVerilog languages. The paper is a continuation of a paper entitled “Standard Gotchas: Subtleties in the Verilog and SystemVerilog Standards That Every Engineer Should Know” that was presented at the Boston 2006 SNUG conference [1]. SNUG San Jose 2007 1 More Gotchas in Verilog and SystemVerilog Table of Contents 1.0 Introduction ............................................................................................................................3 2.0 Design modeling gotchas .......................................................................................................4 2.1 Overlapped decision statements ................................................................................... 4 2.2 Inappropriate use of unique case statements ............................................................... -

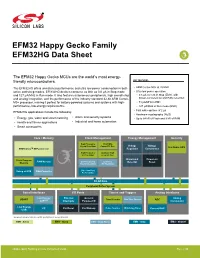

EFM32 Happy Gecko Family EFM32HG Data Sheet

EFM32 Happy Gecko Family EFM32HG Data Sheet The EFM32 Happy Gecko MCUs are the world’s most energy- friendly microcontrollers. KEY FEATURES The EFM32HG offers unmatched performance and ultra low power consumption in both • ARM Cortex-M0+ at 25 MHz active and sleep modes. EFM32HG devices consume as little as 0.6 μA in Stop mode • Ultra low power operation and 127 μA/MHz in Run mode. It also features autonomous peripherals, high overall chip • 0.6 μA current in Stop (EM3), with and analog integration, and the performance of the industry standard 32-bit ARM Cortex- brown-out detection and RAM retention M0+ processor, making it perfect for battery-powered systems and systems with high- • 51 μA/MHz in EM1 performance, low-energy requirements. • 127 μA/MHz in Run mode (EM0) • Fast wake-up time of 2 µs EFM32HG applications include the following: • Hardware cryptography (AES) • Energy, gas, water and smart metering • Alarm and security systems • Up to 64 kB of Flash and 8 kB of RAM • Health and fitness applications • Industrial and home automation • Smart accessories Core / Memory Clock Management Energy Management Security High Frequency 48/24 MHz Voltage Voltage Crystal Oscillator Comm. RC Osc. Hardware AES ARM CortexTM M0+ processor Regulator Comparator High Frequency Auxiliary High RC Oscillator Freq. RC Osc. Brown-out Power-on Flash Program RAM Memory Low Frequency Low Freq. Detector Reset Memory Crystal Oscillator RC Oscillator Debug w/ MTB DMA Controller Ultra Low Freq. RC Oscillator 32-bit bus Peripheral Reflex System Serial Interfaces I/O Ports Timers and Triggers Analog Interfaces Low Energy External General Analog USART Timer/Counter Real Time Counter ADC UARTTM Interrupts Purpose I/O Comparator Low Energy I2C Pin Reset Pin Wakeup Pulse Counter Watchdog Timer Current DAC USB Lowest power mode with peripheral operational: EM0 - Active EM1 - Sleep EM2 – Deep Sleep EM3 - Stop EM4 - Shutoff silabs.com | Building a more connected world. -

Schedule 14A Employee Slides Supertex Sunnyvale

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 SCHEDULE 14A Proxy Statement Pursuant to Section 14(a) of the Securities Exchange Act of 1934 Filed by the Registrant Filed by a Party other than the Registrant Check the appropriate box: Preliminary Proxy Statement Confidential, for Use of the Commission Only (as permitted by Rule 14a-6(e)(2)) Definitive Proxy Statement Definitive Additional Materials Soliciting Material Pursuant to §240.14a-12 Supertex, Inc. (Name of Registrant as Specified In Its Charter) Microchip Technology Incorporated (Name of Person(s) Filing Proxy Statement, if other than the Registrant) Payment of Filing Fee (Check the appropriate box): No fee required. Fee computed on table below per Exchange Act Rules 14a-6(i)(1) and 0-11. (1) Title of each class of securities to which transaction applies: (2) Aggregate number of securities to which transaction applies: (3) Per unit price or other underlying value of transaction computed pursuant to Exchange Act Rule 0-11 (set forth the amount on which the filing fee is calculated and state how it was determined): (4) Proposed maximum aggregate value of transaction: (5) Total fee paid: Fee paid previously with preliminary materials. Check box if any part of the fee is offset as provided by Exchange Act Rule 0-11(a)(2) and identify the filing for which the offsetting fee was paid previously. Identify the previous filing by registration statement number, or the Form or Schedule and the date of its filing. (1) Amount Previously Paid: (2) Form, Schedule or Registration Statement No.: (3) Filing Party: (4) Date Filed: Filed by Microchip Technology Incorporated Pursuant to Rule 14a-12 of the Securities Exchange Act of 1934 Subject Company: Supertex, Inc. -

Getting Started with Psoc 6 MCU (AN221774)

AN221774 Getting Started with PSoC 6 MCU Authors: Srinivas Nudurupati, Vaisakh K V Associated Part Family: All PSoC® 6 MCU devices Software Version: ModusToolbox™ 1.0, PSoC Creator™ 4.2 Associated Application Notes and Code Examples: Click here. More code examples? We heard you. To access an ever-growing list of hundreds of PSoC code examples, please visit our code examples web page. You can also explore the PSoC video library here. AN221774 introduces the PSoC 6 MCU, a dual-CPU programmable system-on-chip with Arm® Cortex®-M4 and Cortex-M0+ processors. This application note helps you explore PSoC 6 MCU architecture and development tools, and shows you how to create your first project using ModusToolbox and PSoC Creator. This application note also guides you to more resources available online to accelerate your learning about PSoC 6 MCU. To get started with the PSoC 6 MCU with BLE Connectivity device family, refer to AN210781 – Getting Started with PSoC 6 MCU with BLE Connectivity. Contents 1 Introduction .................................................................. 2 5.6 Part 4: Build the Application .............................. 32 1.1 Prerequisites ....................................................... 3 5.7 Part 5: Program the Device ............................... 33 2 Development Ecosystem ............................................. 4 5.8 Part 6: Test Your Design ................................... 34 2.1 PSoC Resources ................................................ 4 6 My First PSoC 6 MCU Design 2.2 Firmware/Application Development .................... 5 Using PSoC Creator .................................................. 36 2.3 Support for Other IDEs ....................................... 9 6.1 Using These Instructions .................................. 36 2.4 RTOS Support .................................................... 9 6.2 About the Design .............................................. 37 2.5 Debugging......................................................... 11 6.3 Part 1: Create a New Project from Scratch ...... -

A Full-System VM-HDL Co-Simulation Framework for Servers with Pcie

A Full-System VM-HDL Co-Simulation Framework for Servers with PCIe-Connected FPGAs Shenghsun Cho, Mrunal Patel, Han Chen, Michael Ferdman, Peter Milder Stony Brook University ABSTRACT the most common connection choice, due to its wide availability in The need for high-performance and low-power acceleration tech- server systems. Today, the majority of FPGAs in data centers are nologies in servers is driving the adoption of PCIe-connected FPGAs communicating with the host system through PCIe [2, 12]. in datacenter environments. However, the co-development of the Unfortunately, developing applications for PCIe-connected application software, driver, and hardware HDL for server FPGA FPGAs is an extremely slow and painful process. It is challeng- platforms remains one of the fundamental challenges standing in ing to develop and debug the host software and the FPGA hardware the way of wide-scale adoption. The FPGA accelerator development designs at the same time. Moreover, the hardware designs running process is plagued by a lack of comprehensive full-system simu- on the FPGAs provide little to no visibility, and even small changes lation tools, unacceptably slow debug iteration times, and limited to the hardware require hours to go through FPGA synthesis and visibility into the software and hardware at the time of failure. place-and-route. The development process becomes even more diffi- In this work, we develop a framework that pairs a virtual ma- cult when operating system and device driver changes are required. chine and an HDL simulator to enable full-system co-simulation of Changes to any part of the system (the OS kernel, the loadable ker- a server system with a PCIe-connected FPGA. -

Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure

UNLV Theses, Dissertations, Professional Papers, and Capstones 5-1-2014 Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure Bill Jason Pidlaoan Tomas University of Nevada, Las Vegas Follow this and additional works at: https://digitalscholarship.unlv.edu/thesesdissertations Part of the Computer Engineering Commons, Computer Sciences Commons, and the Electrical and Computer Engineering Commons Repository Citation Tomas, Bill Jason Pidlaoan, "Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure" (2014). UNLV Theses, Dissertations, Professional Papers, and Capstones. 2152. http://dx.doi.org/10.34917/5836171 This Thesis is protected by copyright and/or related rights. It has been brought to you by Digital Scholarship@UNLV with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you need to obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Thesis has been accepted for inclusion in UNLV Theses, Dissertations, Professional Papers, and Capstones by an authorized administrator of Digital Scholarship@UNLV. For more information, please contact [email protected]. CO-EMULATION OF SCAN-CHAIN BASED DESIGNS UTILIZING SCE-MI INFRASTRUCTURE By: Bill Jason Pidlaoan Tomas Bachelor‟s Degree of Electrical Engineering Auburn University 2011 A thesis submitted -

Embedded Linux Systems with the Yocto Project™

OPEN SOURCE SOFTWARE DEVELOPMENT SERIES Embedded Linux Systems with the Yocto Project" FREE SAMPLE CHAPTER SHARE WITH OTHERS �f, � � � � Embedded Linux Systems with the Yocto ProjectTM This page intentionally left blank Embedded Linux Systems with the Yocto ProjectTM Rudolf J. Streif Boston • Columbus • Indianapolis • New York • San Francisco • Amsterdam • Cape Town Dubai • London • Madrid • Milan • Munich • Paris • Montreal • Toronto • Delhi • Mexico City São Paulo • Sidney • Hong Kong • Seoul • Singapore • Taipei • Tokyo Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals. The author and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein. For information about buying this title in bulk quantities, or for special sales opportunities (which may include electronic versions; custom cover designs; and content particular to your business, training goals, marketing focus, or branding interests), please contact our corporate sales depart- ment at [email protected] or (800) 382-3419. For government sales inquiries, please contact [email protected]. For questions about sales outside the U.S., please contact [email protected]. Visit us on the Web: informit.com Cataloging-in-Publication Data is on file with the Library of Congress.