ON Semiconductor Is

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Snubber Considerations for IGBT Applications

Snubber Considerations for IGBT Applications by Yi Zhang, Saed Sobhani, Rahul Chokhawala International Rectifier Applications Engineering 233 Kansas St., El Segundo, CA, 90245 USA Abstract - Snubber circuits can be used to protect fast Note that the fault current transients are more switching IGBTs from turn-on and turn-off voltage effectively protected by considerably slowing the rate transients. Snubbers are available in various of fall of fault current. Fault current turn-off protection configurations and a clear understanding of their through electronic gate control is convered in detail operation is necessary to make the appropriate elsewhere[1]. selection. This paper will discuss pros and cons of these circuits. Decoupling capacitors, RCD voltage Decoupling Capacitors clamp circuit, RCD charge-discharge snubbers are As mentioned earlier, the magnitude of transient voltage included in the discussion. depends on the trapped energy in the circuit stray inductance, also call “DC loop” inductance LS. As a Introduction preventive measure, steps should be taken to improve When a power device is abruptly turned off, trapped the circuit layout. Usage of laminated copper plates, energy in the circuit stray inductance is dissipated in minimizing the size of the “DC loop” and choosing the switching device, causing a voltage overshoot source capacitance with inherently low self inductance across the device. The magnitude of this transient are ways to lower stray inductance [2]. Decoupling voltage is proportional to the amount of stray capacitors, connected across the module’s bus inductance and the rate of fall or turn-off current. The terminals, as shown in Fig.1a, are found to be useful situation is at its worst for fast switching IGBT for low/medium current applications. -

AN1048/D RC Snubber Networks for Thyristor Power Control

AN1048/D RC Snubber Networks For Thyristor Power Control and Littelfuse.com Transient Suppression By George Templeton APPLICATION NOTE Thyristor Applications Engineer INTRODUCTION Edited and Updated RC networks are used to control voltage transients that ǒdVǓ DEVICE PHYSICS could falsely turn-on a thyristor. These networks are called dt s snubbers. Static dV turn-on is a consequence of the Miller effect The simple snubber consists of a series resistor and dt capacitor placed around the thyristor. These components and regeneration (Figure 1). A change in voltage across the along with the load inductance form a series CRL circuit. junction capacitance induces a current through it. This cur- Snubber theory follows from the solution of the circuit’s rent is proportional to the rate of voltage change ǒdVǓ . It differential equation. dt Many RC combinations are capable of providing accept- triggers the device on when it becomes large enough to able performance. However, improperly used snubbers can raise the sum of the NPN and PNP transistor alphas to unity. cause unreliable circuit operation and damage to the semi- conductor device. A Both turn-on and turn-off protection may be necessary A for reliability. Sometimes the thyristor must function with a I IA BP PE range of load values. The type of thyristors used, circuit V PNP configuration, and load characteristics are influential. I CJ I I 1 P J CP NB CJ Snubber design involves compromises. They include N C C I J CN I2 dv I G P cost, voltage rate, peak voltage, and turn-on stress. Practi- J dt B cal solutions depend on device and circuit physics. -

Magnetic Amplifiers & Saturable Reactors

Magnetic amplifiers & Saturable reactors Ricciarelli Fabrizio 01/01/2016 Magnetic amplifiers and saturable reactors Summary SECTION I.......................................................................................................................................................... 2 What are the saturable reactors .................................................................................................................. 2 SECTION II ......................................................................................................................................................... 3 Types of reactors .......................................................................................................................................... 3 Saturable reactors .................................................................................................................................... 4 Linear reactors .......................................................................................................................................... 4 Control modules ....................................................................................................................................... 4 SECTION III ........................................................................................................................................................ 5 History ......................................................................................................................................................... -

Minimizing Switching Ringing at TPS53355 and TPS53353 Family Devices

Application Report SLUA831A–July 2017–Revised November 2018 Minimizing Switching Ringing at TPS53355 and TPS53353 Family Devices Benyam Gebru ABSTRACT The system reliability of a high efficiency DC/DC converter with a fast slew rate is improved when switch node ringing is reduced. This document describes switching ringing reduction methods and lab bench test results with the 30-A TPS53355, and also applies to the pin compatible 20-A TPS53353. Both devices are well-suite for rack server, single board computer, and hardware accelerator applications that benefit from the fast transient response time of D-CAPTM control, or when multi-layer ceramic capacitors are undesirable for the output filter. Contents 1 Introduction ................................................................................................................... 2 2 Proper Measurement Method of Switch Ringing ........................................................................ 2 3 Minimize the Switch Ringing by Adding RC Snubber and Bootstrap Circuit......................................... 5 4 Practical Design.............................................................................................................. 8 5 Adding Bootstrap Resistor ................................................................................................ 11 6 Effects of Snubber on the Efficiency Performance .................................................................... 12 7 Summary ................................................................................................................... -

Single and Dual RC Snubbers

RC Snubbers Single and dual RC snubbers Description: A range of RC snubbers suitable for a broad range of circuit protection applications. The RC snubbers are mounted in a potted box with 6.3mm push on tabs for easy connection to the circuit. The devices have 80mm fixing centers so can be easily mounted alongside industry standard thyristor and diode modules. The range of RC snubbers are suitable for 50Hz/60Hz operation with resistive loads. Images shown are computer generated, for accurate package information please see product drawing Product Highlights Applications 80mm fixing centres Thyristor protection in AC and DC circuits Compact package Diode Protection 440Vrms rating (690Vrms available upon request) Output filters Component Data: Product Reference Maximum varistor energy (J) l voltage 10% 10% - - 10/1000us 2ms Configuration Resistance Value (Ohms) +/ Max. Power Dissipation (W) Capacitance Value (uf) +/ Maximum working voltage (Vrms) Dimension figure. Circuit configuration Varistor nomina (Vrms) ECLRC440 Single RC 56 10 0.22 440 N/A 1 A ECLRC440-2 Dual RC 56 10 0.22 440 N/A 2 B Humidity max. 50% RH @ 35 C / 90% RH @ 20 C Pollution degree: III Isolation: 2500Vrms / 1min Operation temperature: -25C to 80C Mounting position: Any Approx weight: 70grms (single) / 76grms (Dual) (1) The voltages shown are for general phase control applications in W1C circuits. (2) Typical voltage for general purpose rectifier circuits ATTENTION: for continuous operation near to 90 deg phase angle a larger power loss will occur, please consult the factory in these circumstances to see if the device is suitable for the application [email protected] Data can be changed without notice. -

Lossless Active Snubber for Half-Bridge Output Rectifiers

Europaisches Patentamt 19 European Patent Office Office europeen des brevets © Publication number: 0 614 267 A1 12 EUROPEAN PATENT APPLICATION (2j) Application number : 94301445.6 6i) Int. CI.5 : H02M 7/06 (22) Date of filing : 01.03.94 (§) Priority : 05.03.93 US 27031 @ Inventor : Tsai, Fu Sheng 105 Bartlett Street @ Date of publication of application : Northboro, Massachusetts 01532 (US) 07.09.94 Bulletin 94/36 Inventor : Dhaval, Dalai B. 70-9 Commons Drive Shrewsbury, Massachusetts 01545 (US) @ Designated Contracting States : DE FR GB IT (74) Representative : Goodman, Christopher et al Eric Potter & Clarkson © Applicant : DIGITAL EQUIPMENT St. Mary's Court CORPORATION St. Mary's Gate 146 Main Street Nottingham NG1 1LE (GB) Maynard, Massachusetts 01745 (US) @) Lossless active snubber for half-bridge output rectifiers. (57) A bridge-type primary switching circuit (12) is represented by a pulsed voltage source (VSW). The primary switched waveform is transformed to secondary circuit (14) using a transformer (T1) with the required turns ratio N and a cen- ter-tapped secondary winding (16). Half-bridge rectifier (18) formed by diodes (DR1) and (DR2) rectifies the secondary waveform and feeds the waveform through a low-pass filter (LF) and (CF) to obtain the desired DC output voltage. The snubber circuit (20) is represented by switch-diode-capacitor combinations (SA- DS1-CS1) and (SB-DS2-CS2) across each rec- tifier (DR1) and (DR2). Capacitances (CS1) and (CS2) are selected large enough such that their voltages remain essentially constant during a switching cycle. The controlled switches (SA) and (SB) are turned ON with a specific delay after the primary voltage reaches a magnitude close to the input voltage in order to allow the rectifier diodes (DR1) and (DR2) to be commu- tated. -

Snubber Circuits

Lecture Notes Snubber Circuits William P. Robbins Dept. of Electrical and Computer Engineering University of Minnesota Outline A. Overview of Snubber Circuits B. Diode Snubbers C. Turn-off Snubbers D. Overvoltage Snubbers E. Turn-on Snubbers F. Thyristor Snubbers Snubbers -1 1 W.P. Robbins Overview of Snubber Circuits for Hard-Switched Converters Function: Protect semiconductor devices by: Types of Snubber Circuits • Limiting device voltages during turn-off transients 1. Unpolarized series R-C snubbers • Used to protect diodes and thyristors • Limiting device currents during turn-on transients 2. Polarized R-C snubbers • Limiting the rate-of-rise (di/dt) of currents through • Used as turn-off snubbers to shape the turn-on the semiconductor device at device turn-on switching trajectory of controlled switches. • Used as overvoltage snubbers to clamp voltages applied to controlled switches to safe values. • Limiting the rate-of-rise (dv/dt) of voltages across • Limit dv/dt during device turn-off the semiconductor device at device turn-off 3. Polarized L-R snubbers • Shaping the switching trajectory of the device as it • Used as turn-on snubbers to shape the turn-off turns on/off switching trajectory of controlled switches. • Limit di/dt during device turn-on Snubbers - 2 W.P. Robbins Need for Diode Snubber Circuit di Df Vd = d t L L σ + σ R Io s I t o i Df (t) D I Vd f Cs rr - Sw v (t) t Df Vd • Lσ = stray inductance • S w closes at t = 0 • Diode voltage di L σ without snubber Lσ • Rs - Cs = snubber circuit d t diLσ • Diode breakdown if V + L > BV d σ dt BD Snubbers - 3 W.P. -

La Marche Battery Charger Technologies

Battery Charger Technologies Vance Persons Murad Daana Engineering Manager Business Development Manager La Marche Mfg. Co. La Marche Mfg. Co. Des Plaines, IL 60018 Des Plaines, IL 60018 Abstract This paper reviews the history of the battery charger industry and provides a technical overview on the methodology of the different battery charger technologies, such as Magnetic Amplifiers, Ferro-resonant, SCR rectifiers and High Frequency Switchmode chargers. Introduction Many industrial applications such as Utility Switchgear, Oil Platforms, Gas Turbines, Process Control, etc., involve the operation of critical DC loads. Dropping any of these critical loads may result in extreme and costly circumstances. Therefore, these applications require the use of batteries as a backup power source in case of a power outage. Hence, a need was developed for equipment used to maintain the charge in the batteries. Battery charger / DC power supply technologies have been developed over the years to improve the efficiency, reliability and cost of the equipment. These different technologies serve the same purpose of supporting the DC loads and maintaining a full charge in the battery of a DC system. Each technology, however, has its advantages and disadvantages. 1 – 1 Magnetic Amplifier (Mag-Amp) Technology Magnetic Amplifier is one of the first technologies used in rectifying the AC power in DC power applications. Mag-Amp has had many development stages over the years and has over 190 patent filings. This technology started when Dr. Alexanderson submitted a paper presenting this concept to the Institute of Radio Engineers in 1916. The paper detailed replacing Vacuum Tube Rectifiers which had many disadvantages compared to Mag- Amp. -

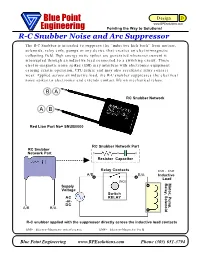

SNUBBER Circuit

Blue Point Design D www.BPEsolutions.com Engineering Pointing the Way to Solutions! R-C Snubber Noise and Arc Suppressor The R-C Snubber is intended to suppress the “inductive kick back” from motors, solenoids, relay coils, pumps or any device that creates an electro-magnetic collapsing field. High energy noise spikes are generated whenever current is interrupted through an inductive load connected to a switching circuit. These electro-magnetic noise spikes (EMI) may interfere with electronics equipment causing erratic operation, CPU failure and may also accelerate relay contact wear. Applied across an inductive load, the R-C snubber suppresses the electrical noise spikes to electronics and extends contact life on mechanical relays. B A RC Snubber Network A B Red Lion Part No= SNUB0000 RC Snubber Network Part RC Snubber Network Part Resistor Capacitor Relay Contacts EMI - EMF A/B B/A Inductive Load (NO) Relay, Solenoid Motor, Pump, Supply Voltage Switch AC RELAY -or- DC A/B B/A R-C snubber applied with the suppressor directly across the inductive load contacts EMI= Electro-Magnetic interference EMF= Electro-Magnetic Field Blue Point Engineering www.BPEsolutions.com Phone (303) 651-3794 Relay, Solenoid Motor, Pump, Blue Point Design D www.BPEsolutions.com Engineering Pointing the Way to Solutions! R-C Snubber Noise and Arc Suppressor APPLICATION The inductive load suppressors are effective in both AC and DC Power circuits Preferred Application Method R-C snubber should be applied with the inductive load suppressor directly across the inductive -

Assessment of Saturable Reactor Replacement Options

Assessment of Saturable Reactor Replacement Options D.T.A Kho, K.S. Smith Abstract -- The performance of the dynamic reactive power overvoltage is unclear. Given that the original TOV compensation provided by the existing variable static characteristics on which the design of the saturable reactor compensation (STC) on the UK side of the Cross-Channel HVDC operation is based is not available, and that the actual link has been assessed. These uniquely designed STCs are now requirement may have changed over time, it is difficult to being considered for replacement. Alternatives to provide the design and specify the control systems for both the TCR and same performance as delivered by the existing STCs have been auto-switched shunt reactor options. This paper summarises proposed and their overvoltage suppression performances have the study undertaken to assess the voltage waveform during been assessed against the existing STCs using a PSCAD-EMTDC model of the England-France HVDC link. The paper transient disturbances, particularly following ac side faults, demonstrates how the PSCAD-EMTDC simulation has been used leading to converter blocking, filter islanding and ultimately to make informed design decision concerning the STC bipole connection trip. The PSCAD-EMTDC model of the replacement option. recent IFA2000 refurbishment project had been used throughout the study. The performance of the three Keywords : Saturable reactor, Temporary overvoltage, HVDC replacement options have been compared in the context of link, Thyristor Controlled Reactor (TCR), PSCAD-EMTDC. TOV suppression due to faults. I. INTRODUCTION II. STC REPLACEMENT OPTIONS HE original Cross-Channel HVDC link was on the UK T side, designed with three Saturable Reactors installed, two A. -

RC Snubber Circuits

Snubber Circuits For Power Electronics Rudy Severns 1 2 Snubber Circuits For Power Electronics Rudy Severns 3 Copyright © 2008 Rudolf Severns All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photo-copying, recording or otherwise, without prior written permission of Rudolf Severns. Legal notice: Great effort has been made to make the material presented in this book as accurate as possible. However, the author and publisher assume no responsibility or liability whatsoever on behalf of any Purchaser or Reader of these materials. It is the responsibility of the user to exercise good engineering judgment when using this material. A note from the author. Preparing a book like this takes well over 1000 hours of effort and a substantial investment by the author and publisher. Hopefully, this book will prove to be a useful contribution to the power electronics art. When such books are successful and provide some reasonable return to their authors, there is motivation to write more such books on other important subjects. The result is of benefit to all in our profession. Honesty is a fundamental requirement for any professional engineer and is expected of those in the profession or training for it. Your help is requested in not making copies of this work and distributing it to others or in accepting any such copy. 4 Table of contents PREFACE 7 ACKNOWLEDGEMENT 11 CHAPTER 1 13 An Overview Of Snubbers 13 What is a snubber? 21 Classifying snubbers -

Saturable Reactor for Power Flow Control in Electric Transmission Systems: Modeling and System Impact Study

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Doctoral Dissertations Graduate School 5-2015 Saturable Reactor for Power Flow Control in Electric Transmission Systems: Modeling and System Impact Study Marcus Aaron Young II University of Tennessee - Knoxville, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_graddiss Part of the Electromagnetics and Photonics Commons, and the Power and Energy Commons Recommended Citation Young, Marcus Aaron II, "Saturable Reactor for Power Flow Control in Electric Transmission Systems: Modeling and System Impact Study. " PhD diss., University of Tennessee, 2015. https://trace.tennessee.edu/utk_graddiss/3377 This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a dissertation written by Marcus Aaron Young II entitled "Saturable Reactor for Power Flow Control in Electric Transmission Systems: Modeling and System Impact Study." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Doctor of Philosophy, with a major in Electrical Engineering. Yilu Liu, Major Professor We have read this