Memory LCD Programming.Fm

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

LQ043T3DX02 TFT-LCD Module

PRODUCT SPECIFICATIONS Mobile Liquid Crystal Displays Group LQ043T3DX02 TFT-LCD Module Spec. Issue Date: Feb. 8, 2005 No: LCP-05005 SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. Suggested applications (if any) are for standard use; See Important Restrictions for limitations on special applications. See Limited Warranty for SHARP’s product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will SHARP be liable, or in any way responsible, for any incidental or consequential economic or property damage. NORTH AMERICA EUROPE JAPAN SHARP Microelectronics of the Americas SHARP Microelectronics Europe SHARP Corporation 5700 NW Pacific Rim Blvd. Division of Sharp Electronics (Europe) GmbH Electronic Components & Devices Camas, WA 98607, U.S.A. Sonninstrasse 3 22-22 Nagaike-cho, Abeno-Ku Phone: (1) 360-834-2500 20097 Hamburg, Germany Osaka 545-8522, Japan Fax: (1) 360-834-8903 Phone: (49) 40-2376-2286 Phone: (81) 6-6621-1221 Fast Info: (1) 800-833-9437 Fax: (49) 40-2376-2232 Fax: (81) 6117-725300/6117-725301 www.sharpsma.com www.sharpsme.com www.sharp-world.com TAIWAN SINGAPORE KOREA SHARP Electronic Components SHARP Electronics (Singapore) PTE., Ltd. SHARP Electronic Components (Taiwan) Corporation 438A, Alexandra Road, #05-01/02 (Korea) Corporation 8F-A, No. 16, Sec. 4, Nanking E. Rd. Alexandra Technopark, RM 501 Geosung B/D, 541 Taipei, Taiwan, Republic of China Singapore 119967 Dohwa-dong, Mapo-ku Phone: (886) 2-2577-7341 Phone: (65) 271-3566 Seoul 121-701, Korea Fax: (886) 2-2577-7326/2-2577-7328 Fax: (65) 271-3855 Phone: (82) 2-711-5813 ~ 8 Fax: (82) 2-711-5819 CHINA HONG KONG SHARP Microelectronics of China SHARP-ROXY (Hong Kong) Ltd. -

GP2Y0D310K 1 Bit Output Distance Measuring Sensor

PRODUCT DOCUMENTATION Sharp Optoelectronic Components GP2Y0D310K 1 Bit Output Distance Measuring Sensor Issue Date: January 18, 2005 No: ED-05G009 SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. Suggested applications (if any) are for standard use; See Important Restrictions for limitations on special applications. See Limited Warranty for SHARP’s product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will SHARP be liable, or in any way responsible, for any incidental or consequential economic or property damage. NORTH AMERICA EUROPE JAPAN SHARP Microelectronics of the Americas SHARP Microelectronics Europe SHARP Corporation 5700 NW Pacific Rim Blvd. Division of Sharp Electronics (Europe) GmbH Electronic Components & Devices Camas, WA 98607, U.S.A. Sonninstrasse 3 22-22 Nagaike-cho, Abeno-Ku Phone: (1) 360-834-2500 20097 Hamburg, Germany Osaka 545-8522, Japan Fax: (1) 360-834-8903 Phone: (49) 40-2376-2286 Phone: (81) 6-6621-1221 Fast Info: (1) 800-833-9437 Fax: (49) 40-2376-2232 Fax: (81) 6117-725300/6117-725301 www.sharpsma.com www.sharpsme.com www.sharp-world.com TAIWAN SINGAPORE KOREA SHARP Electronic Components SHARP Electronics (Singapore) PTE., Ltd. SHARP Electronic Components (Taiwan) Corporation 438A, Alexandra Road, #05-01/02 (Korea) Corporation 8F-A, No. 16, Sec. 4, Nanking E. Rd. Alexandra Technopark, RM 501 Geosung B/D, 541 Taipei, Taiwan, Republic of China Singapore 119967 Dohwa-dong, Mapo-ku Phone: (886) 2-2577-7341 Phone: (65) 271-3566 Seoul 121-701, Korea Fax: (886) 2-2577-7326/2-2577-7328 Fax: (65) 271-3855 Phone: (82) 2-711-5813 ~ 8 Fax: (82) 2-711-5819 CHINA HONG KONG SHARP Microelectronics of China SHARP-ROXY (Hong Kong) Ltd. -

LED Specification

Technical Document LED Specification EC/Opto Group PC817XxNiP0F Series Photocoupler Product Specification June 2008 PC817XxNiP0F Series Full Specification for part numbers: PC817XNNIP0F PC817XlNIP0F PC817X2NIP0F PC817X3NIP0F PC817X4NIP0F PC817X5NIP0F PC817X6NIP0F PC817X7NIP0F PC817X8NIP0F PC817X9NIP0F PC817XONIP0F Technical Document Opto Specification Opto/EC Group NORTH AMERICA EUROPE JAPAN Sharp Microelectronics of the Americas Sharp Microelectronics Europe Sharp Corporation 5700 NW Pacific Rim Blvd. Division of Sharp Electronics (Europe) GmbH Electronic Components & Devices Camas, WA 98607, U.S.A. Sonninstrasse 3 22-22 Nagaike-cho, Abeno-Ku Phone: (1) 360-834-2500 20097 Hamburg, Germany Osaka 545-8522, Japan Fax: (1) 360-834-8903 Phone: (49) 40-2376-2286 Phone: (81) 6-6621-1221 www.sharpsma.com Fax: (49) 40-2376-2232 Fax: (81) 6117-725300/6117-725301 www.sharpsme.com www.sharp-world.com TAIWAN Sharp Electronic Components SINGAPORE HONG KONG (Taiwan) Corporation Sharp Electronics (Singapore) PTE., Ltd. Sharp-Roxy (Hong Kong) Ltd. 8F-A, No. 16, Sec. 4, Nanking E. Rd. 438A, Alexandra Road, #05-01/02 Level 26, Tower 1, Kowloon Commerce Centre, Taipei, Taiwan, Republic of China Alexandra Technopark, No. 51, Kwai Cheong Road, Kwai Chung, Phone: (886) 2-2577-7341 Singapore 119967 New Territories, Hong Kong Fax: (886) 2-2577-7326/2-2577-7328 Phone: (65) 271-3566 Phone: (852) 28229311 Fax: (65) 271-3855 Fax: (852) 28660779 CHINA www.sharp.com.hk Sharp Microelectronics of China KOREA Shenzhen Representative Office: (Shanghai) Co., Ltd. Sharp Electronic Components Room 602-603, 6/F., 28 Xin Jin Qiao Road King Tower 16F (Korea) Corporation International Chamber of Commerce Tower, Pudong Shanghai, 201206 P.R. -

Kina Datterselskabsliste 2012.Pdf

1. Preface .......................................................................................................................... 3 2. Abbreviations ............................................................................................................... 3 3. AEC .............................................................................................................................. 4 4. E&E .............................................................................................................................. 8 5. FDR.............................................................................................................................20 6. FOOD ........................................................................................................................36 7. HEALTH ...................................................................................................................43 8. ITE ..............................................................................................................................52 9. MMI ............................................................................................................................61 10. SERVICE ....................................................................................................................75 Consulate General of Denmark, Guangzhou Page 2 of 86 The Trade Council The Trade Council thanks you for taking an interest in the list of Danish companies in China. The list is produced by the Consulate General Guangzhou, China. -

Infrastructure Asset Management Review of Tall Residential Buildings Of

Journal of Built Environment, Technology and Engineering, Vol. 3 (September) 2017 ISSN 0128-1003 ASSET MANAGEMENT REVIEW OF TALL RESIDENTIAL BUILDINGS IN MAJOR CITIES: CHICAGO, HONG KONG AND SINGAPORE Raymond Cheng Email: [email protected] Reader, Industrial Doctorate (IndD) Programme, Asia e University, Kuala Lumpur, MALAYSIA Ivan Ng Email: [email protected] Executive Director, Russia Capital Investment Corporation Limited, HONG KONG ABSTRACT There is only one residential skyscraper within China’s top 100 tallest buildings in the crowded 24-million- population city of Shanghai, China (and eleven residential skyscrapers among the 134 tallest buildings, i.e. those taller than 150 metres), whereas there are comparatively a lot more skyscrapers used for residential purposes in equally densely populated cities like Hong Kong, Singapore, Kuala Lumpur and, of course, Chicago and New York. This paper, hence, looked, from a historical perspective, how the development of tall buildings in Chicago, Hong Kong and Singapore have evolved to become what we see today. How does the tall building development history of a city help forge the people’s view in terms of living in skyscrapers? Would such help provide explanations and hints as to the future development of skyscrapers in the other cities like Shanghai? Keywords: Tall building, skyscraper, high-rise, development history Learning from the American experience The mythical story of the Tower of Babel tells us that how height, in itself, since the beginning of known history, means power to human beings. But before Elisha Otis revolutionized and refined the safety of the elevator by inventing the elevator brakes1 in 1852, both the Greek mathematician Archimedes of Syracuse and King Louis XV of France could only have envisioned their great ideas through primitive, man-powered, inefficient mechanical lifting devices back in their days. -

GP2Y3A002K0F Wide Angle Sensor

PRODUCT DOCUMENTATION Sharp Optoelectronic Components GP2Y3A002K0F Wide Angle Sensor Issue Date: April 28, 2005 No: ED-05G107 SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. Suggested applications (if any) are for standard use; See Important Restrictions for limitations on special applications. See Limited Warranty for SHARP’s product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will SHARP be liable, or in any way responsible, for any incidental or consequential economic or property damage. NORTH AMERICA EUROPE JAPAN SHARP Microelectronics of the Americas SHARP Microelectronics Europe SHARP Corporation 5700 NW Pacific Rim Blvd. Division of Sharp Electronics (Europe) GmbH Electronic Components & Devices Camas, WA 98607, U.S.A. Sonninstrasse 3 22-22 Nagaike-cho, Abeno-Ku Phone: (1) 360-834-2500 20097 Hamburg, Germany Osaka 545-8522, Japan Fax: (1) 360-834-8903 Phone: (49) 40-2376-2286 Phone: (81) 6-6621-1221 Fast Info: (1) 800-833-9437 Fax: (49) 40-2376-2232 Fax: (81) 6117-725300/6117-725301 www.sharpsma.com www.sharpsme.com www.sharp-world.com TAIWAN SINGAPORE KOREA SHARP Electronic Components SHARP Electronics (Singapore) PTE., Ltd. SHARP Electronic Components (Taiwan) Corporation 438A, Alexandra Road, #05-01/02 (Korea) Corporation 8F-A, No. 16, Sec. 4, Nanking E. Rd. Alexandra Technopark, RM 501 Geosung B/D, 541 Taipei, Taiwan, Republic of China Singapore 119967 Dohwa-dong, Mapo-ku Phone: (886) 2-2577-7341 Phone: (65) 271-3566 Seoul 121-701, Korea Fax: (886) 2-2577-7326/2-2577-7328 Fax: (65) 271-3855 Phone: (82) 2-711-5813 ~ 8 Fax: (82) 2-711-5819 CHINA HONG KONG SHARP Microelectronics of China SHARP-ROXY (Hong Kong) Ltd. -

LQ064A5CG01 TFT-LCD Module

PRODUCT SPECIFICATIONS Liquid Crystal Displays Group LQ064A5CG01 TFT-LCD Module Spec. Issue Date: April 14, 1999 No: LCY-99052B sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp sharp SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. Suggested applications (if any) are for standard use; See Important Restrictions for limitations on special applications. See Limited Warranty for SHARP’s product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will SHARP be liable, or in any way responsible, for any incidental or consequential economic or property damage. NORTH AMERICA EUROPE JAPAN SHARP Microelectronics of the Americas SHARP Microelectronics Europe SHARP Corporation 5700 NW Pacific Rim Blvd. Division of Sharp Electronics (Europe) GmbH Electronic Components & Devices Camas, WA 98607, U.S.A. Sonninstrasse 3 22-22 Nagaike-cho, Abeno-Ku Phone: (1) 360-834-2500 20097 Hamburg, Germany Osaka 545-8522, Japan Fax: (1) 360-834-8903 Phone: (49) 40-2376-2286 Phone: (81) 6-6621-1221 Fast Info: (1) 800-833-9437 Fax: (49) 40-2376-2232 Fax: (81) 6117-725300/6117-725301 www.sharpsma.com www.sharpsme.com www.sharp-world.com TAIWAN SINGAPORE KOREA SHARP Electronic Components SHARP Electronics (Singapore) PTE., Ltd. SHARP Electronic Components (Taiwan) Corporation 438A, Alexandra Road, #05-01/02 (Korea) Corporation 8F-A, No. 16, Sec. 4, Nanking E. Rd. Alexandra Technopark, RM 501 Geosung B/D, 541 Taipei, Taiwan, Republic of China Singapore 119967 Dohwa-dong, Mapo-ku Phone: (886) 2-2577-7341 Phone: (65) 271-3566 Seoul 121-701, Korea Fax: (886) 2-2577-7326/2-2577-7328 Fax: (65) 271-3855 Phone: (82) 2-711-5813 ~ 8 Fax: (82) 2-711-5819 CHINA HONG KONG SHARP Microelectronics of China SHARP-ROXY (Hong Kong) Ltd. -

GP1S092HCPIF Photointerrupter

PRODUCT SPECIFICATION Optoelectronics Components Group GP1S092HCPIF Photointerrupter (Model Number: GP1S092HCPIF) Spec. Issue Date: September 5, 2005 Spec No: ED-03G027 SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. Suggested applications (if any) are for standard use; See Important Restrictions for limitations on special applications. See Limited Warranty for SHARP’s product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will SHARP be liable, or in any way responsible, for any incidental or consequential economic or property damage. NORTH AMERICA EUROPE JAPAN SHARP Microelectronics of the Americas SHARP Microelectronics Europe SHARP Corporation 5700 NW Pacific Rim Blvd. Division of Sharp Electronics (Europe) GmbH Electronic Components & Devices Camas, WA 98607, U.S.A. Sonninstrasse 3 22-22 Nagaike-cho, Abeno-Ku Phone: (1) 360-834-2500 20097 Hamburg, Germany Osaka 545-8522, Japan Fax: (1) 360-834-8903 Phone: (49) 40-2376-2286 Phone: (81) 6-6621-1221 Fast Info: (1) 800-833-9437 Fax: (49) 40-2376-2232 Fax: (81) 6117-725300/6117-725301 www.sharpsma.com www.sharpsme.com www.sharp-world.com TAIWAN SINGAPORE KOREA SHARP Electronic Components SHARP Electronics (Singapore) PTE., Ltd. SHARP Electronic Components (Taiwan) Corporation 438A, Alexandra Road, #05-01/02 (Korea) Corporation 8F-A, No. 16, Sec. 4, Nanking E. Rd. Alexandra Technopark, RM 501 Geosung B/D, 541 Taipei, Taiwan, Republic of China Singapore 119967 Dohwa-dong, Mapo-ku Phone: (886) 2-2577-7341 Phone: (65) 271-3566 Seoul 121-701, Korea Fax: (886) 2-2577-7326/2-2577-7328 Fax: (65) 271-3855 Phone: (82) 2-711-5813 ~ 8 Fax: (82) 2-711-5819 CHINA HONG KONG SHARP Microelectronics of China SHARP-ROXY (Hong Kong) Ltd. -

The Role of the Aerodynamic Modifications of the Shapes of Tall Buildings Jooeun Lee Massachusetts Institute of Technology JUN 2

The Role of the Aerodynamic Modifications MASSACHUSETTS INSTITUTE of the Shapes of Tall Buildings OF TECH'OLOGY JUN 2 4 2011 by Jooeun Lee LIBRA RIE S B.Eng. School of Architecture and Architectural Engineering Inha University, South Korea ARCHVES 1999 Submitted to the Department of Civil and Environmental Engineering in Partial Fulfillment of the Requirements for the degree of Master of Science in Civil and Environmental Engineering at the Massachusetts Institute of Technology June 2011 © 2011 Massachusetts Institute of Technology All rights reserved Signature of Author: Department ol' Civil and nvironmental Engineering April 15, 2011 Certified by: Jerome J. Connor Professor of Civil and Environmental Engineering Z Thesis Supervisor Accepted by: M. Nepf Chair, Departmental Committee for Students The Role of the Aerodynamic Modifications of the Shapes of Tall Buildings by Jooeun Lee Submitted to the Department of Civil and Environmental Engineering on April 15, 2011 in Partial Fulfillment of the Requirements for the degree of Master of Science in Civil and Environmental Engineering Abstract With the advances in technology, recent tall building design has undergone a shift to the free-style geometric forms in the exuberant and liberal atmosphere. As a height of the building increases, it is more susceptible to vibration caused by wind because of its asymmetric distribution of mass and stiffness, increased flexibility and insufficient inherent damping. This wind-induced motion, in particular crosswind response, endangers the dynamic response of tall structures, the performance of cladding and window, and the habitability of occupants. Therefore, much research on mitigating wind induced excitations of tall buildings has been carried out. -

169 Annex 5–List of Subsidiaries

ANNEX 5 – LIST OF SUBSIDIARIES OF NIKON 169 NIKON GROUP Companies Domestic Companies Name Address Telephone Main Business Mito Nikon Precision Corporation✩ 4500, Sugaya, Naka, Ibaraki 311-0194 +81-29-298-8111 Manufacture of devices for IC/LCD steppers and scanners Zao Nikon Co., Ltd.✩ 20, Shin-oyoke, Miya, Zao-machi, Katta-gun, +81-224-32-2336 Manufacture of devices for IC/LCD Miyagi 989-0701 steppers and scanners Sendai Nikon Precision 289, Aza-hara, Tako, Natori, Miyagi 981-1221 +81-22-384-0018 Manufacture of devices for IC/LCD Corporation✩*2 steppers and scanners Tochigi Nikon Precision Co., Ltd.✩ 760, Midori, Otawara, Tochigi 324-8520 +81-287-28-1177 Manufacture of IC/LCD steppers and scanners, and lenses for IC/LCD steppers and scanners Nikon Tec Corporation✩ 5-21, Katsushima 1-chome, Shinagawa-ku, Tokyo +81-3-5762-8911 Maintenance and servicing of IC/ 140-0012 LCD steppers and scanners, sales of used steppers and scanners Tochigi Nikon Corporation✩ 770, Midori, Otawara, Tochigi 324-8625 +81-287-28-1111 Manufacture of interchangeable lenses and optical lenses Sendai Nikon Corporation✩ 277, Aza-hara, Tako, Natori, Miyagi 981-1221 +81-22-384-0011 Manufacture of cameras Nikon Imaging Japan Inc.✩*3 4-1, Shibaura 3-chome, Minato-ku, Tokyo 108- +81-3-3769-7900 Sales and servicing of cameras 0023 Kurobane Nikon Co., Ltd.✩ 1434, Kurobanemuko-machi, Otawara, Tochigi +81-287-53-1111 Manufacture of objective lenses for 324-0241 microscopes/measuring instruments/ semiconductor inspection equipment, and optical components Nikon Instech Co., Ltd.✩*4 6-3, Nishiohi 1-chome, Shinagawa-ku, Tokyo +81-3-3773-1173 Sales, maintenance and servicing 140-8601 of microscopes, measuring instruments, and semiconductor inspection equipment Hikari Glass Co., Ltd.✩ 1399, Monoi, Yotsukaido, Chiba 284-0012 +81-43-422-5221 Manufacture and sale of optical glass and molded optical glass Nikon Optical Shop Co., Ltd. -

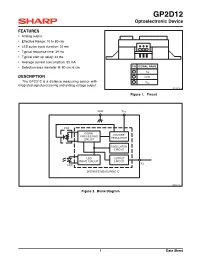

GP2D12 Data Sheet.Fm

GP2D12 Optoelectronic Device FEATURES • Analog output • Effective Range: 10 to 80 cm • LED pulse cycle duration: 32 ms 132 • Typical response time: 39 ms • Typical start up delay: 44 ms • Average current consumption: 33 mA • Detection area diameter @ 80 cm: 6 cm PIN SIGNAL NAME 1VO DESCRIPTION 2 GND The GP2D12 is a distance measuring sensor with 3 VCC integrated signal processing and analog voltage output. GP2D12-8 Figure 1. Pinout GND VCC PSD SIGNAL VOLTAGE PROCESSING REGULATOR CIRCUIT OSCILLATOR CIRCUIT LED OUTPUT DRIVE CIRCUIT CIRCUIT V LED O DISTANCE MEASURING IC GP2D12-4 Figure 2. Block Diagram 1 Data Sheet GP2D12 ELECTRICAL SPECIFICATIONS Absolute Maximum Ratings Ta = 25°C, VCC = 5 VDC PARAMETER SYMBOL RATING UNIT Supply Voltage VCC -0.3 to +7.0 V Output Terminal Voltage VO -0.3 to (VCC + 0.3) V Operating Temperature Topr -10 to +60 °C Storage Temperature Tstg -40 to +70 °C Operating Supply Voltage PARAMETER SYMBOL RATING UNIT Operating Supply Voltage VCC 4.5 to 5.5 V Electro-optical Characteristics Ta = 25°C, VCC = 5 VDC PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT NOTES Measuring Distance Range ΔL10-80cm1, 2 Output Voltage VO L = 80 cm 0.25 0.4 0.55 V 1, 2 Output change at L change Output Voltage Difference ΔV 1.75 2.0 2.25 V 1, 2 O (80 cm - 10 cm) Average Supply Current ICC L = 80 cm - 33 50 mA 1, 2 NOTES: 1. Measurements made with Kodak R-27 Gray Card, using the white side, (90% reflectivity). 2. L = Distance to reflective object. -

LQ064V3DG01 TFT-LCD Module

PRODUCT SPECIFICATIONS Mobile Liquid Crystal Displays Group LQ064V3DG01 TFT-LCD Module Spec. Issue Date: May 16, 2005 No: LAI-04032C LA1-04032C-1 NOTICE This publication is the proprietary of SHARP and is copyrighted, with all rights reserved. Under the copyright laws, no part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical for any purpose, in whole or in part, without the express written permission of SHARP. Express written permission is also required before any use of this publication may be made by a third party. The application circuit examples in this publication are provided to explain the representative applications of SHARP's devices and are not intended to guarantee any circuit design or permit any industrial property right or other rights to be executed. SHARP takes no responsibility for any problems related to any industrial property right or a third party resulting from the use of SHARP's devices, except for those resulting directly from device manufacturing processes. In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that occur in equipment using any of SHARP's devices, shown in catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP's device. SHARP reserves the right to make changes in the specifications, characteristics, data, materials, structures and other contents described herein at any time without notice in order to improve design or reliability. Contact SHARP in order to obtain the latest specification sheets before using any SHARP's device.