Fault-Tolerant Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Digital Switching Systems, I.E., System Testing and Accep- Tance and System Maintenance and Support

SSyyed Riifffat AAlli DDiiggiittaall SSwwiittcchhiinngg SSyysstteemmss ((Syystemm Reliaabbiilliittyy aandd AAnnalysis) Bell Communications Research, Inc. Piscataway, New Jersey McGraw-Hill, Inc. New York • San Francisco • Washington, DC. Auckland • BogotA • Cara- cas • Lisbon • London Madrid • Mexico City • Milan • Montreal • New Delhi San Juan • Singapore • Sydney • Tokyo • Toronto 2 PREFACE The motive of this book is to expose practicing telephone engineers and other graduate engineers to the art of digital switching system (DSS) analysis. The concept of applying system analysis techniques to the digital switching sys- tems as discussed in this book evolved during the divestiture period of the Bell Operating Companies (BOCs) from AT&T. Bell Communications Research, Inc. (Bellcore), formed in 1984 as a research and engineering company support- ing the BOCs, now known as the seven Regional Bell Operating Companies (RBOCs), conducted analysis of digital switching system products to ascertain compatibility with the network. Since then Bellcore has evolved into a global provider of communications software, engineering, and consulting services. The author has primarily depended on his field experience in writing this book and has extensively used engineering and various symposium publications and advice from many subject matter experts at Bellcore. This book is divided into six basic categories. Chapters 1, 2, 3, and 4 cover digital switching system hardware, and Chaps. 5 and 6 cover software ar- chitectures and their impact on switching system reliability. Chapter 7 primarily covers field aspects of digital switching systems, i.e., system testing and accep- tance and system maintenance and support. Chapter 8 covers networked aspects of the digital switching system, including STf SCP, and AIN. -

The Great Telecom Meltdown for a Listing of Recent Titles in the Artech House Telecommunications Library, Turn to the Back of This Book

The Great Telecom Meltdown For a listing of recent titles in the Artech House Telecommunications Library, turn to the back of this book. The Great Telecom Meltdown Fred R. Goldstein a r techhouse. com Library of Congress Cataloging-in-Publication Data A catalog record for this book is available from the U.S. Library of Congress. British Library Cataloguing in Publication Data Goldstein, Fred R. The great telecom meltdown.—(Artech House telecommunications Library) 1. Telecommunication—History 2. Telecommunciation—Technological innovations— History 3. Telecommunication—Finance—History I. Title 384’.09 ISBN 1-58053-939-4 Cover design by Leslie Genser © 2005 ARTECH HOUSE, INC. 685 Canton Street Norwood, MA 02062 All rights reserved. Printed and bound in the United States of America. No part of this book may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without permission in writing from the publisher. All terms mentioned in this book that are known to be trademarks or service marks have been appropriately capitalized. Artech House cannot attest to the accuracy of this information. Use of a term in this book should not be regarded as affecting the validity of any trademark or service mark. International Standard Book Number: 1-58053-939-4 10987654321 Contents ix Hybrid Fiber-Coax (HFC) Gave Cable Providers an Advantage on “Triple Play” 122 RBOCs Took the Threat Seriously 123 Hybrid Fiber-Coax Is Developed 123 Cable Modems -

Economic Analysis of the Cost of Inconsistencies in the Implementation of ISDN Network Layer Standards

Rochester Institute of Technology RIT Scholar Works Theses 2002 Economic analysis of the cost of inconsistencies in the implementation of ISDN network layer standards Thomas Bennett Follow this and additional works at: https://scholarworks.rit.edu/theses Recommended Citation Bennett, Thomas, "Economic analysis of the cost of inconsistencies in the implementation of ISDN network layer standards" (2002). Thesis. Rochester Institute of Technology. Accessed from This Thesis is brought to you for free and open access by RIT Scholar Works. It has been accepted for inclusion in Theses by an authorized administrator of RIT Scholar Works. For more information, please contact [email protected]. Economic Analysis of the Cost of Inconsistencies in the Implementation of ISDN Network Layer Standards By Thomas R. Bennett Thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Information Technology Rochester Institute of Technology B. Thomas Golisano College of Computing and Information Sciences March 2002 Thesis Reproduction Permission Form Rochester Institute of Technology B. Thomas Golisano College of Computing and Information Sciences Master of Science in Information Technology Economic Analysis of the Cost of Inconsistencies in the Implementation of ISDN Network Layer Standards I, Thomas R. Bennett, hereby grant permission to the Wallace Library of the Rochester Institute of Technology to reproduce my thesis in whole or in part. Any reproduction must not be for commercial use or profit. Date: ~) J&/JOQ;2.. Signature of Author: _ Rochester Institute of Technology B. Thomas Golisano College of Computing and Information Sciences Master of Science in Information Technology Thesis Approval Form Student Name: Thomas R. -

Telecom) Terms Glossary and Dictionary - A

Tele-Communication (Telecom) Terms Glossary and Dictionary - A A & B Bit A & B Bit is used in digital environments to convey signaling information. A bit equal to one generally corresponds to loop current flowing in an analog environment; A bit value of zero corresponds to no loop Current, i.e. to no connection. Other signals are made by changing bit values: for example, a flash-hook is sent by briefly setting the A bit to zero. A Links A Links, also known as SS7 access links, connect an end office or signal point to a mated pair of signal transfer points. They may also connect signal transfer points and signal control points at the regional level with the A-links assigned in a quad arrangement. A&B Bit Signaling A&B Bit Signaling, also called 24th channel signaling, is a procedure used in T1 transmission facilities in which each of the 24Â T1 subchannels devotes 1 bit of every sixth frame to the carrying of supervisory signaling information. On T1 lines that use Extended SuperFrame(ESF) framing, the signaling bits are robbed from the 6th, 12th, 18th, and 24th frame, resulting in "ABCD" signaling bits. ABAM cable ABAM cable refers to a type of T1 cable. This cable was a 22 gauge, 100 ohm insulated, twisted pair. ABAM cable is no longer available, but you can easily find cable that meets the technical requirements. Abandoned Call Abandoned Call is a call in which the call originator disconnects or cancels the call after a connection has been made, but before the call is established. -

5Ess Switching Equipment Assignment Rules

___________________________________________________________________________________________________________ DWG CD DWG CD DWG CD ___________________________________________________ ISS ISS ISS ISS ISS ISS ___________________________________________________ 1 1 2D 2D 3D 3D DWG CD DWG CD DWG CD ___________________________________________________ ISS ISS ISS ISS ISS ISS 5D 4A 4A 5D 5D 6B APPX ___________________________________________________ 1B DWG CD DWG CD DWG CD ___________________________________________________ ISS ISS ISS ISS ISS ISS 5D 7AC APPX 8D 6D 9D 7D ___________________________________________________ 2AC DWG CD DWG CD DWG CD ___________________________________________________ ISS ISS ISS ISS ISS ISS ___________________________________________________ 10D 8D 11M 9M 12A 10A DWG CD DWG CD DWG CD ___________________________________________________ ISS ISS ISS ISS ISS ISS ___________________________________________________ 13M 11M 14M 12M 15B 13B DWG CD DWG CD DWG CD ___________________________________________________ ISS ISS ISS ISS ISS ISS ___________________________________________________ 16M 14M 17A 15A 18M 16M DWG CD DWG CD DWG CD ___________________________________________________ ISS ISS ISS ISS ISS ISS ___________________________________________________ 19B 17B -

Verizon Safe Time Window Practice Contents

VERIZON PRACTICE VZ 220-000-001 Verizon Standard Issue 1, February 2003 Verizon Safe Time Window Practice Contents Subject Page 1. General.......................................................................................................................................................3 1.1 Purpose....................................................................................................................................................3 1.2 Supersedures ...........................................................................................................................................4 1.3 Responsibility ...........................................................................................................................................4 1.4 Disclaimer.................................................................................................................................................4 2.1 Definitions.................................................................................................................................................5 2.2 References ...............................................................................................................................................8 3. PAUSE........................................................................................................................................................9 3.1 Prevent All Unplanned Service Events Policy............................................................................................9 4. National -

Innovation Is in Ourdna Letter from Our Contents Page 12 Our Editor Features

Magazine for the Science & Technology Innovation Center in Middletown, NJ • Premier Edition Honoring the Past, Creating the Future Innovation is in ourDNA Letter from Our Contents page 12 our Editor Features 2 The History of AT&T 94 Data Transmssion — Fax Welcome to our Science & Technology Innovation Center of Middletown, New Jersey magazine premier edition. The new Innovation Center is a place 12 The Transistor 100 Cellular Phones of inspiration and learning from the history of AT&T and significant inventions that our company has created over the past 142+ years that contribute to 13 Bell Solar Cell 104 Project AirGig™ the advancement of humanity. Over my years at AT&T, I have spoken to many The Telstar Project Our Contributors people who never knew that AT&T had a history of innovation in so many 16 109 areas beyond the creation of the telephone by Alexander Graham Bell. Coax Cable 24 Throughout the years, AT&T has been a key player in local and long-distance 30 Fiber Optics in the AT&T Network voice telephony, motion pictures, computers, the cable industry, wireless, and Science & Technology broadband. AT&T has served the nation’s telecommunication needs and par- 34 Vitaphone and Western Electric ticipated in many technology partnerships in every industry throughout the globe. The breadth of technology and innovation goes on and on, but a 44 Picturephone Irwin Gerszberg few of the innovations you might see at our new Innovation Center include: Innovation ground-to-air radio telephony, motion picture sound, the Telstar satellite, Theseus Honoring the Past, Creating the Future AVP Advanced Technology Research 48 telephone switching, the facsimile machine, military radar systems, the AT&T Science & Technology transistor, undersea cable, fiber communications, Picturephone via T1’s, coin 50 A Short History of UNIX™ EDITOR-IN-CHIEF Innovation Center phones, touch-tone dialing, AMPS cellular phones, UNIX™ and C language Irwin Gerszberg programming. -

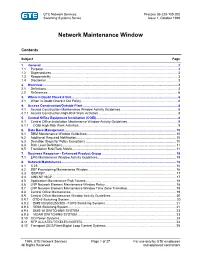

220-100-300 Switching Systems Series Issue 1, October 1999

GTE Network Services Practice 06-220-100-300 Switching Systems Series Issue 1, October 1999 Network Maintenance Window Contents Subject Page 1. General........................................................................................................................................................ 2 1.1 Purpose ..................................................................................................................................................... 2 1.2 Supersedures............................................................................................................................................ 3 1.3 Responsibility ............................................................................................................................................ 3 1.4 Disclaimer.................................................................................................................................................. 3 2. Overview ..................................................................................................................................................... 3 2.1 Definitions.................................................................................................................................................. 3 2.2 References................................................................................................................................................ 6 3. When in Doubt Check it Out..................................................................................................................... -

Software Fault Prevention by Language Choice: Why C Is Not My Favorite Language

Software Fault Prevention by Language Choice: Why C is Not My Favorite Language Richard Fateman Computer Science Division Electrical Engineering and Computer Sciences Dept. University of California, Berkeley June 15, 1999 Abstract How much does the choice of a programming language in¯uence the prevalence of bugs in the resulting code? It seems obvious that at the level at which individuals write new programs, a change of language can eliminate whole classes of errors, or make them possible. With few exceptions, recent literature on the engineering of large software systems seems to neglect language choice as a factor in overall quality metrics. As a point of comparison we review some interesting recent work which implicitly assumesa program must be written in C. We speculate on how reliability might be affected by changing the language, in particular if we were to use ANSI Common Lisp. 1 Introduction and Background In a recent paper, W. D. Yu [6] describes the kinds of errors committed by coders working on Lucent Technologies advanced 5ESS switching system. This system's reliability is now dependent on the correct functioning of several million lines of source code.1 Yu not only categorizes the errors, but enumerates within some categories the technical guidelines developed to overcome problems. Yu's paper's advice mirrors, in some respects, the recommendations in Maguire's Writing Solid Code [4], a book brought to my attention several years ago for source material in a software engineering undergraduate course. This ge- nial book explains techniques for avoiding pitfalls in programming in C, and contains valuable advice for intermediate or advanced C language programmers. -

6512766287.Pdf

• u .- Appendix C Bell Atlantic/NYNEX 1997-2000 Merger Cost Savings Summary of BA-NY Intrastate Savings ($ Millions) pescription 1997 1998 1999 2001 1. Total Bell Atlantic Merger Expense Savings (from K. O'Ouinn's Exhibit, Part I, Line 3) 122& ~ ~ 1QZ1Q 1,077.0 2. BA-NY Intrastate Regulated Merger Savings (from K. O'Ouinn's Exhibit, Part I, Line 7) 27.3 92.5 150.0 219.5 219.5 3. BA-NY Intrastate Regulated Merger Costs (from K. O'Ouinn's Exhibit, Part III) 47.2 43.2 38.2 Q.& Q.Q 4. BA-NY Intrastate Net Merger Savings (from K. O'Ouinn's Exhibit, Part IV) (19.9) 49.3 111.8 218.9 219.5 5. Costs Due to Additional Commitments (from K. O'Ouinn's Exhibit, Part V) (47.1) (84.m (116.0> illMl ~ t 6. Net Merger Savings per Company (67.0) (34.7) (4.2) 85.3 74.0 Staff Adlustments 7. Savings from MIT Analysis 3.5 11.0 18.3 26.7 26.7 8. Savings Related to Union Employees (112.6) (6.5) 96.6 100.5 9. Savings Related to Correct Loading Rate 0.7 3.9 8.4 10.7 11.0 10. Savings Related to Correct Allocation 3.7 12.0 20.7 29.1 29.2 11. Revenue Enhancements (from Staff's Testimony in Cases 96-C-0603/0599) 39.0 107.0 143.0 12. Costs Due to Additional Commitments (from above) 47.1 84.0 116.0 133.6 145.5 13. -

AUDIX® System Description Copyright 1995 AT&T All Rights Reserved Printed in U.S.A

AT&T 585-305-201 Issue 4 November 1993 Comcode 106917057 AUDIX® System Description Copyright 1995 AT&T All Rights Reserved Printed in U.S.A. Notice Ordering Information While reasonable efforts were made to ensure that the information The ordering number for this document is in this document was complete and accurate at the time of printing, 585-310-226. To order this document, call the GBCS AT&T can assume no responsibility for any errors. Changes and Publications Fulfillment Center at 1-800-457-1235 (International corrections to the information contained in this document may be callers use 1-317-361-5353). For more information about AT&T incorporated into future reissues. documents, refer to the Global Business Communications Systems Publications Catalog (555-000-010). Your Responsibility for Your System's Security You are responsible for the security of your system. AT&T does not warrant that this product is immune from or will prevent Comments unauthorized use of common-carrier telecommunication services or To comment on this document, return the comment facilities accessed through or connected to it. AT&T will not be card at the front of the document. responsible for any charges that result from such unauthorized use. Product administration to prevent unauthorized use is your Acknowledgment responsibility and your system administrator should read all This document was prepared by the AT&T Product Documentation documents provided with this product to fully understand the Development Department, Denver, CO 80234-2703. features available that may reduce your risk of incurring charges. Federal Communications Commission Statement Part 15: Class A Statement. -

Chapter 9 on the Early History and Impact of Unix Tools to Build the Tools for a New Millennium

Chapter 9 On the Early History and Impact of Unix Tools to Build the Tools for a New Millennium “When the barbarian, advancing step by step, had discovered the native metals, and learned to melt them in the crucible and to cast them in moulds; when he had alloyed native copper with tin and produced bronze; and, finally, when by a still greater effort of thought he had invented the furnace, and produced iron from the ore, nine tenths of the battle for civilization was gained. Furnished, with iron tools capable of holding both an edge and a point, mankind were certain of attaining to civilization.” Lewis Henry Morgan “When Unix evolved within Bell Laboratories, it was not a result of some deliberate management initiative. It spread through channels of technical need and technical contact.... This was typical of the way Unix spread around Bell Laboratories.... I brought out that little hunk of history to point out that the spread and success of Unix, first in the Bell organizations and then in the rest of the world, was due to the fact that it was used, modified, and tinkered up in a whole variety of organizations.” Victor Vyssotsky “UNIX is a lever for the intellect.” John R. Mashey Iron Tools and Software Tools Our era is witnessing the birth of an important new technology, different from any in the past. This new technology is the technology of software production. The new tools of our era are tools that make it possible to produce software. Unlike the tools forged in the past, software tools are not something you can grab or hold.