The 555 Timer IC (Adapted From

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

IC 555 Timer in the Contemporary World

International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume -4 Issue-6, August 2015 An Imprint of IC 555 Timer in t he Contemporary World Nanditha Nandanavanam Abstract- The paper deals with the basic principle of IC 555 There is also a flip flop element which gives high output Timer, its working and its application in the present world. 555 when ‘S’ is high and ‘R’ is low. It gives low when ‘R’ is Timer is part and parcel of almost every electronics project. It is high and ‘S’ is low. versatile IC whose applications range from simply making a light blink on and off to pulse-width modulation. From the time of its Pin configuration invention, a myriad of several novel and unique circuits have been developed and presented in several trade, professional , and hobby publications. Keywords: Monostable mode, A stable mode, Oscillator, Speed Detector, Hygrometer, Invertor, Patents. I. INTRODUCTION IC 555 timer is an integrated circuit(IC) or a chip used for various electronic applications. The IC was designed in 1971 by Hans R. Camenzind under a contract to Signetics, which was later acquired by Philips. It has b een in wide use ever since. It wa s the very first commercial timer IC to be designed. IC 555 timer got its name from three 5 kilo ohm resistors connec ted in series voltage divider. A single IC consists of several transistors, resistors, capacitors, diodes, flip flops and other elements. It is a highly stable device for Fig. 2 Pin diagram generating accurate time delays or oscillation [8]. -

Page 1 of 19 a Plethora of NE-555 Data

A Plethora Of NE-555 data - NE555 Tutorials Page Page 1 of 19 - - - - - - - - - - - - - - - - Copyright © January 28th 1996 ..... Brought to you by Unitech Electronics Pty. Ltd. Following in the footsteps of the "primitive" but quite successful 4 pin OM802 timer IC manufactured by Philips semiconductor way back in 1969, a new and very innovative IC known as the NE-555 timer IC was released to the masses, being introduced around May 1971 by the then Signetics Corporation, to become known as the NE-555 / SE-555. It was called "The Ubiquitous Timer chip" and was also the very first very mass-produced commercially produced timer IC available at that time.The designers had no real idea what product life it would have, nor how brilliantly successful it would be, lasting well over 25 years still in mass-production today. [1971- 1996 ] The NE-555 would prove to be a " hit " and provide Electronic Engineers, Circuit Designers and a host of "Hobby Tinkerers" with a relatively novel and highly economical timer chip that was indeed very stable at timing all the way up to its maximum timing or oscillating frequency of 200KHz and in a very short time proved to be a very "user-friendly" timer integrated circuit for both simple and complex monostable as well as brilliant astable applications. Invented by a clever Swiss born gentleman by the name of Hans R. Camenzind in 1970, the NE-555 went on to become a legend in the industry, Since this versatile device became commercially available in May 1971, a plethora of highly innovative and very unique and "ever-so-ingenious" circuits has emerged and many circuits have been developed and demonstrated to the "N-th" degree in a variety of reputed "trade-only" journals, professional "Engineering Monthly" Journals as well as the vast numbers of excellent hobbiest publications globally, the likes of SILICON CHIP (SC) and ELEKTOR , Practical Electronics (PE) , Electronics Australia (EA) and Electronics Today International (ETI) to name but just a few. -

Multivibrator Circuits

Multivibrator Circuits Bistable multivibrators Multivibrators Circuits characterized by the existence of some well defined states, amongst which take place fast transitions, called switching processes. A switching process is a fast change in value of a current or a voltage, the fast process implying the existence of positive reaction loops, or negative resistances. The switching can be triggered from outside, by means of command signals, or from inside, by slow charge accumulation and the reaching of a critical state by certain electrical quantities in the circuit. Circuits have two, well defined states, which can be either stable or unstable A stable state is a state, in which the circuit, in absence of a driving signal, can remain for an unlimited period of time The circuit can remain in an unstable state only for a limited period of time, after which, in the absence of any exterior command signals, it switches into the other state. The multivibrator circuits can be grouped, according to their number of stable (steady) states, into: - flip-flops (bistable circuits) with both states being stable - monostable circuits , having a stable and an unstable state - astable circuits , with both states being unstable Flip-flop circuits The main feature of the flip-flop circuits is the existence of two stable states, in which the circuit may remain for a long time. The switching from one state to the other is triggered by command signals Flip flop: an example for a sequential circuit (a circuit with outputs that present logical values depending on a certain sequence of signals, that have previously existed in the circuit). -

Op-Amp Comparators Model of a Schmitt Trigger

1 Electronic Instrumentation Experiment 6 -- Digital Switching Part A: Transistor Switches Part B: Comparators and Schmitt Triggers Part C: Digital Switching Part D: Switching a Relay Part A: Transistors Analog Circuits vs. Digital Circuits Bipolar Junction Transistors Transistor Characteristics Using Transistors as Switches 2 Analog Circuits vs. Digital Circuits An analog signal is an electric signal whose value varies continuously over time. A digital signal can take on only finite values as the input varies over time. 3 • A binary signal, the most common digital signal, is a signal that can take only one of two discrete values and is therefore characterized by transitions between two states. • In binary arithmetic, the two discrete values f1 and f0 are represented by the numbers 1 and 0, respectively. 4 • In binary voltage waveforms, these values are represented by two voltage levels. • In TTL convention, these values are nominally 5V and 0V, respectively. • Note that in a binary waveform, knowledge of the transition between one state and another is equivalent to knowledge of the state. Thus, digital logic circuits can operate by detecting transitions between voltage levels. The transitions are called edges and can be positive (f0 to f1) or negative (f1 to f0). 1 positive negative positive edge 0 edges edge 5 Bipolar Junction Transistors The bipolar junction transistor (BJT) is the salient invention that led to the electronic age, integrated circuits, and ultimately the entire digital world. The transistor is the principal active device in electrical circuits. When inputs are kept relatively small, the transistor serves as an amplifier. When the transistor is overdriven, it acts as a switch, a mode most useful in digital electronics. -

Npn Transistor Pnp Transistor

ELL 100 - Introduction to Electrical Engineering LECTURE 23: BIPOLAR JUNCTION TRANSISTOR (BJT) 1 CONTENTS • Introduction • Construction & working principle of BJT • Common-base and common-emitter circuits 2 BJT INTRODUCTION • Bipolar: Both electrons and holes (positively charged quasi- particles, absence of electron) contribute to current flow • Junction: Consists of an n- (or p-) type silicon sandwiched between two p- (or n-) type silicon regions • Transistor: 3-terminal device (Base, Emitter, Collector) Two types: npn & pnp 3 Bipolar Junction Transistor (BJT) 4 Various Types of General-Purpose or Switching Transistors: (a) Low Power (b) Medium Power (c) Medium to high power 5 First Working Transistor, Invented in 1947. Earliest Raytheon Blue transistors, Replica of 1st device made by first appearing in 1955 Shockley, Bardeen & Brattain at Bell Labs 6 Applications: Transistor As Switch 7 Applications: Transistor As Relay (Switch) Single channel 5V relay breakout board 8 Applications: Transistor As Amplifier TDA7297 Power Amplifier & Audio amplifier Module 9 Applications: Transistors in Radio 10 Applications: Transistor in Oscillator Colpitts Oscillator 11 Applications: Transistor in Oscillator Astable Multivibrator 12 Transistors in Timer Circuits 13 Transistor As NOT Gate 14 Transistors in NAND Gate 15 Bipolar Junction Transistor (BJT) The three terminals of the BJT are called the Base (B), the Collector (C) and the Emitter (E). n p p n n p npn transistor pnp transistor 16 Bipolar Junction Transistor (BJT) npn pnp 17 p-n-p Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 18 n-p-n Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 19 BJT Construction 20 Bipolar Junction Transistor (BJT) Basic Principle The voltage between two terminals (B and E) controls the current through the third terminal (C). -

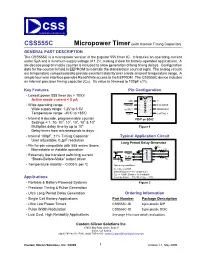

CSS555C Micropower Timer (With Internal Timing Capacitor) GENERAL PART DESCRIPTION the CSS555C Is a Micropower Version of the Popular 555 Timer IC

css Custom Silicon Solutions, Inc. CSS555C Micropower Timer (with Internal Timing Capacitor) GENERAL PART DESCRIPTION The CSS555C is a micropower version of the popular 555 timer IC. It features an operating current under 5µA and a minimum supply voltage of 1.2V, making it ideal for battery-operated applications. A six-decade programmable counter is included to allow generation of long timing delays. Configuration data for the counter is held in EEPROM to maintain the standard pin count of eight. The analog circuits are temperature compensated to provide excellent stability over a wide ambient temperature range. A simple four-wire interface provides Read/Write access to the EEPROM. The CSS555C device includes an internal precision timing capacitor (C TI ). Its value is trimmed to 100pF ±1%. Key Features Pin Configuration • Lowest power 555 timer (by > 10X)! Active mode current < 5 µA GND 1 CSS555C 8 V+ • Wide operating range TRIGGER 2 7 DISCHARGE Wide supply range: 1.2V to 5.5V OUTPUT 3 6 THRESHOLD Temperature range: -40°C to +85°C RESET 4 5 CONTROL V • Internal 6 decade, programmable counter PDIP or SOIC Settings = 1, 10, 10 2, 10 3, 10 4, 10 5 & 10 6 Multiplies delay time by up to 10 6 Figure 1 Delay times from microseconds to days • Internal 100pF, ±1% Timing Capacitor Typical Application Circuit User adjustable, 0.2pF resolution Long Period Delay Generator • Pin-for-pin compatible with 555 series timers VDD CSS555C RA Monostable or Astable operation 1 8 • Extremely low transient switching current Trigger 2 7 Output 3 6 RB “Break-Before-Make” -

PLC Based Timer Controller for Multiple Machines

International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 4, Issue 8, August (2016) www.ijeter.everscience.org PLC Based Timer Controller for Multiple Machines T.Vignesh, Assistant professor/Project Guide/EEE, Jay Shriram Group of Institutions, India. N.Lakshmanakumar, S.Sethu, P.Kumarasamy, S.Gowthamraj UG Scholar /EEE Jay Shriram group of Institutions, India. Abstract – This paper describes the design and development of a 2. PROGRAMMABLE LOGIC CONTROLLER feedback control system that maintains the time of a process at a desired set point. The system consists of a PLC-based timer The Programmable Logic Controller (PLC) is a relatively new controller unit that provides input and output interfaces between technology that uses a computer to process the information. the PLC and the man machine interface and computer system. The control task is incorporated into a graphical program called The main difference from other computers is that PLCs are the Ladder Logic Diagram. Any control task modifications are armoured for severe conditions such as dust, moisture, heat, cold done by changing the program. Today, PLCs are used in many etc., and have the facility for extensive input/output (I/O) "real world" applications such as machining, packaging, arrangements. The paper will provide details about the timer material handling, automated assembly or countless other control unit, shows the implementation of the controller unit, and industrial processes. present test results. Index Terms – PLC, Ladder Language, Functional Block Basic PLCs are available on a single printed circuit board .They Diagram (FBD), Automation. are sometimes called single board PLCs or open frame PLCs. -

Chapter 3: Oscillators and Waveform-Shaping Circuits

mywbut.com CHAPTER3:OSCILLATORSANDWAVEFORM-SHAPING CIRCUITS Inthedesignofelectronicsystems,theneed frequentlyarises forsignals havingprescribed standardwaveforms(e.g.,sinusoidal, square,triangle,pulse,etc).Thesewaveformsarecommonly usedincomputers,controlsystems,communicationsystemsandtestmeasurementsystems. Therearetwocommonwaysforgeneratingsinusoids: 1. Positivefeedbackloopwithnon-lineargainlimiting 2. Appropriatelyshapingotherwaveformssuchasatrianglewaves. Circuitsthatdirectlygeneratesquare,triangleandpulsewaveformsgenerallyemploycircuit blocksknownasmultivibrators.Threebasictypesarebistable,astableandmonostable. I.SINUSOIDALOSCILLATORS: Commonly referred to as linear sine-wave oscillators although some forms of non-linearity havetobeemployedtolimittheoutputamplitude.Analysisofthecircuitsismoredifficultass-plane analysis cannot be directly applied to the non-linear part of the circuit. The basic structure of a sinusoidal oscillator consists of an amplifier and a frequency selective network connected in a positivefeedbackloop. AmplifierA xS + Σ xO + xf Freq.Selective networkβ Figure1:Basicstructureofasinusoidaloscillator. Apositive-feedbackloopisformedbyanamplifierandafrequency-selectivenetwork.Inan actualoscillatorcircuit,noinputsignalwillbepresent;hereaninputsignalxsisemployedtohelp explaintheprincipleofoperation.NotethatthefeedbacksignalXFissummedwithapositivesign: A(s) A (s) = f 1− A(s) β (s) Theloopgainis: )s(L =A(s) β (s) Andthecharacteristicequationcanbewrittenas: 1-L(s)=0 If at a specific frequency -

Optically Operated Circuit to Sense the Intensity of the Surrounding Light

1 Optically Operated Circuit to Sense the Intensity of the surrounding Light PRUTHVI.K.S ,, ABHIRAM.RDr.AIT, Bangalore and , TEJUS. P , Dr.AIT [email protected] Abstract—The transistor is the key active component in II. BIPOLAR TRANSISTOR BIASING practically all modern electronics, and is considered by many to be A very proper biasing of transistor is a very crucial measure one of the greatest inventions of the twentieth century. Transistors are invariably used in tremendous applications but its use is mostly for any transistor operation that decides the performance and as integrated form. The essential usefulness of a transistor comes efficiency of the device. There are many ways of biasing a from its ability to use a small signal applied between one pair of its BJT but the very stable way of biasing is the voltage divider terminals to control a much larger signal at another pair of configuration and hence it is been implemented in our light terminals. This property is called gain. This is the only basic intensity sensing circuit. In this section we discuss on the principle used to make an Optically Operated Circuit. An LED various ways of biasing a BJT and finally conclude that the (Light Emitting Diode) connected at the output pair of terminals voltage divider way of biasing is the best. light whose intensity is proportional to the surrounding light intensity. Case 1(Using two supplies) Keywords—Transistor biasing, LDR, phototransistors, 555 timer circuit, relay. I. INTRODUCTION he transistor is the fundamental building block of modern T electronic devices, and is ubiquitous in modern electronic systems. -

Design of CMOS Schmitt Trigger Munish Kumar, Parminder Kaur, Sheenu Thapar

ISSN: 2277-3754 ISO 9001:2008 Certified International Journal of Engineering and Innovative Technology (IJEIT) Volume 2, Issue 1, July 2012 Design of CMOS Schmitt Trigger Munish Kumar, Parminder Kaur, Sheenu Thapar voltage is applied at the input, both M1 andM2 are in OFF Abstract— This paper presents comparison among various condition while M4 and M5 are in ON condition and output Schmitt triggers on the basis of their hysteresis width and is at high logic level. When the input reaches to threshold average power consumed. Hysteresis width is improved by using voltage of M1 transistor then M1 will be on , while M2 two feedback loops as compared to conventional CMOS Schmitt trigger whose hysteresis width is fixed. All Schmitt trigger remains OFF and at this time output will be high M3 will be circuits have been realized using .25um and .18µm CMOS on , so M1 Try to pull down the node between M1 and M2 technology and simulation results are presented. while M3 try to pulls up this node to voltage VDD-VT , so transistor M2 stays the output to HIGH logic level , now Index Terms— Hysteresis Width, Static Power Dissipation, Dynamic Power Dissipation. when the input rises up to the threshold voltage of M2 then output switches to low logic level, so effectively our I. INTRODUCTION switching point shifted to higher voltage referred as VIH. Similar in case when input is falling from higher logic level Schmitt triggers are bistable networks that are widely used then PMOS‘s comes into picture and switching point at to enhance the immunity of a circuit to noise and output is shifted to some lower voltage referred as VIH. -

I. Introduction

EXPERIMENT 7. SCHMITT TRIGGER AND MULTIVIBRATOR CIRCUITS I. Introduction I.I Objectives The purpose of this experiment is to get familiar with different types of Schmitt trigger and multivibrator circuits and their implementations. I.II. Prerequisites You are expected to get familiar with the basics of the Schmitt trigger and multivibrator circuits. You can start reading your lecture notes and the section titled “CMOS Schmitt Trigger Circuits,” from your text book by Thomas A. Demassa and Zack Ciccone (pages 437-439). These pages are the introduction parts, and they explain what basically hysteresis is, and why it may be needed. However, that chapter explains digital Schmitt trigger circuits. What we construct in the laboratory are analog ones. Detailed information on these analog Schmitt trigger circuits and multivibrator circuits can be found in “Microelectronics Circuits” by Adel S. Sedra, Kenneth C. Smith. Reading these two references and completing the preliminary work will help you to understand the topic prior to your actual lab session and also it will help you in interpreting your experiment results. Experiment 7: Schmitt Triggers and Multivibrator Circuits All Rights Reserved. (e-mail: [email protected] ) by Eren Aydın and Barış Bayram © 2015 Page 1 of 7 II. Preliminary Work 1) Draw IC. Explain the aim of the the internal block diagram of 555 timer components inside 555 timer. 2) Consider the monostable multivibrator circuit given in Fig. What kind of input signal should be applied to the circuit for proper operation? Explain operation principle of this circuit in detail drawing required graphs. Moreover1 design a circuit doing the same operation using NAND gates, an inductor and a resistor. -

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC 555 AIM To design and set up astable multivibrator of 1000 Hz frequency and 60% duty cycle using IC 555 THEORY IC 555 timer is an analog IC used for generating accurate time delay or oscillations. The entire circuit is usually housed in an 8-pin package as specified in figures 1 & 2 below. A series connection of three resistors inside the IC sets the reference voltage levels to the two 2 1 comparators at V and V , the output of these comparators setting or resetting the flip- 3 CC 3 CC flop unit. The output of the flip-flop circuit is then brought out through an output buffer stage. In the stable state the 푄 output of the flip-flop is high (ie Q low). This makes the output (pin 3) low because of the buffer which basically is an inverter.The flip-flop circuit also operates a transistor inside the IC, the transistor collector usually being driven low to discharge a timing capacitor connected at pin 7. The description of each pin s described below, Pin 1: (Ground): Supply ground is connected to this pin. Pin 2: (Trigger): This pin is used to give the trigger input in monostable multivibrator. When trigger of amplitude greater than (1/3)Vcc is applied to this terminal circuit switches to quasi-stable state. Pin 3: (Output) Pin 4 (Reset): This pin is used to reset the output irrespective of input. A logic low at this pin will reset output. For normal operation pin 4 is connected to Vcc.