Conversion from Linear to Circular Polarization in Fpga in Real Time

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Constraints on Black-Hole Charges with the 2017 EHT Observations of M87*

PHYSICAL REVIEW D 103, 104047 (2021) Constraints on black-hole charges with the 2017 EHT observations of M87* – Prashant Kocherlakota ,1 Luciano Rezzolla,1 3 Heino Falcke,4 Christian M. Fromm,5,6,1 Michael Kramer,7 Yosuke Mizuno,8,9 Antonios Nathanail,9,10 H´ector Olivares,4 Ziri Younsi,11,9 Kazunori Akiyama,12,13,5 Antxon Alberdi,14 Walter Alef,7 Juan Carlos Algaba,15 Richard Anantua,5,6,16 Keiichi Asada,17 Rebecca Azulay,18,19,7 Anne-Kathrin Baczko,7 David Ball,20 Mislav Baloković,5,6 John Barrett,12 Bradford A. Benson,21,22 Dan Bintley,23 Lindy Blackburn,5,6 Raymond Blundell,6 Wilfred Boland,24 Katherine L. Bouman,5,6,25 Geoffrey C. Bower,26 Hope Boyce,27,28 – Michael Bremer,29 Christiaan D. Brinkerink,4 Roger Brissenden,5,6 Silke Britzen,7 Avery E. Broderick,30 32 Dominique Broguiere,29 Thomas Bronzwaer,4 Do-Young Byun,33,34 John E. Carlstrom,35,22,36,37 Andrew Chael,38,39 Chi-kwan Chan,20,40 Shami Chatterjee,41 Koushik Chatterjee,42 Ming-Tang Chen,26 Yongjun Chen (陈永军),43,44 Paul M. Chesler,5 Ilje Cho,33,34 Pierre Christian,45 John E. Conway,46 James M. Cordes,41 Thomas M. Crawford,22,35 Geoffrey B. Crew,12 Alejandro Cruz-Osorio,9 Yuzhu Cui,47,48 Jordy Davelaar,49,16,4 Mariafelicia De Laurentis,50,9,51 – Roger Deane,52 54 Jessica Dempsey,23 Gregory Desvignes,55 Sheperd S. Doeleman,5,6 Ralph P. Eatough,56,7 Joseph Farah,6,5,57 Vincent L. -

Effelsberg Newsletter January 2012

Effelsberg Newsletter Volume 3 w Issue 1 w January 2012 Effelsberg Newsletter January 2012 Call for Proposals Deadline for Effelsberg Proposals is February 8, 2012, 13.00 UT. Page 2 Greetings from the Director Content Page 2 Call for Proposals It is a pleasure to wish you a very happy new year 2012! It has been a very busy last year, with lots of changes and new instrumentation Page 4 First results of the described in the past issues of this newsletter. Even more interesting Effelsberg-Bonn HI Survey changes lie ahead of us, and as usual, we will keep you posted about all the progress being made. We will also continue to give you a glimpse Page 6 Effelsberg delivers first of the science highlights achieved with the 100-m telescope, and it is fringes with Radioastron: also a pleasure to introduce you to further members of staff and to Space VLBI sets a new report on our outreach activities. world-record in radio interferometry. The output and the performance of the telescope is going strong, underlining its superb capabilities even 40 years after its inauguration. Page 7 Who is Who in Effelsberg? Peter Vogt This is not surprising, given that the telescope and its instruments are constantly upgraded. Still, we are only half-way through our activities Page 8 Public Outreach: celebrating these 40 years. Further highlights are still to follow - stay Extension of the tuned! We will give you further details in the upcoming issues of this Effelsberg Milky Way newsletter, which now has a new look. -

TWO POSTDOCTORAL POSITIONS in RADIO ASTRONOMY at the Mpifr in BONN, GERMANY Submission Address: Prof

TWO POSTDOCTORAL POSITIONS IN RADIO ASTRONOMY AT THE MPIfR IN BONN, GERMANY Submission address: Prof. Dr. J. Anton Zensus Max-Planck-Institut für Radioastronomie Auf dem Hügel 69 D-53123 Bonn, Germany Tel. +49 228 525 298 [email protected] Contact information for inquiries: Prof. Dr. Eduardo Ros Tel. +49 228 525 125 [email protected] Deadline: Dec 1st, 2017 The Max-Planck-Institut für Radioastronomie (MPIfR) is recruiting up to two postdoctoral reserachers in radio astronomy. These positions are based in the Radio Astronomy/VLBI department led by Prof. J. Anton Zensus. The department has a broad research portfolio. Research topics focus on the investigation of compact extragalactic objects (AGN) and their broad-band emission, with a special emphasis on very-high-resolution studies. These include mm- and space-VLBI imaging and blazar monitoring with F-GAMMA/MOJAVE/TANAMI. The MPIfR operates the 100-m radio telescope in Effelsberg (element of EVN and GMVA), and it is major partner of APEX in Chile (element of EHT). It also operates a state-of-the-art VLBI correlator and the LOFAR DE1 station, which is part of the International LOFAR Telescope. We are looking for researchers with a science interest matching our research topics. Technical mastery of radio interferometry techniques and VLBI is of advantage, as well as a good publication record. Candidates with complementary skills to our research portfolio are especially encouraged to apply. The appointee will be expected to engage in one or more of our research lines and to collaborate closely with other department members. The International Max Planck Research School for Astronomy and Astrophysics (IMPRS) offers the opportunity for joint research with PhD students, their supervision, and teaching in the program. -

Reaching an Agreement on UK Participation in Horizon Eu

Securing a strong outcome for research in the EU-UK future relationship: Reaching an agreement on UK participation in Horizon Europe The EU and UK have been discussing UK participation in Union Programmes, including Horizon Europe, as part of the negotiations on a future EU-UK relationship. It is encouraging that both sides have committed to the principle of UK participation in their mandates, recognising that collaboration between the UK and the EU in the framework programmes strengthens our ability to tackle shared challenges, such as cancer and climate change. It is vital that this commitment now translates quickly into an agreement on the terms of participation. Horizon Europe association should be a core part of the future relationship between the EU and the UK for research, underpinning valuable scientific partnerships that have been built up over many years. We have all reaped the health benefits of these collaborations. Clinical trials, particularly on diseases with limited patient populations, are reliant on EU-UK collaboration, while close research partnerships continue to accelerate life-changing medical research. Our ability to respond to the threat of climate change and outbreaks of new diseases like Covid-19 has also been greatly improved by close scientific and clinical partnerships across Europe. Knowledge and discovery do not stop at borders, and the shared global challenges we face require joint solutions. Collaboration through the research framework programmes is a springboard to productive partnerships across the world. We owe it to future generations in the UK, the EU and beyond to ensure that the new EU-UK relationship best serves them through research. -

A Portrait of a Black Hole

Overview_Black Holes A picture of a dark monster. The image is the first direct visual evidence of a black hole. This particularly massive specimen is at the center of the supergiant galaxy Messier 87 and was acquired by the Event Horizon Telescope (EHT), an array of eight ground-based radio telescopes distributed around the globe. A portrait of a black hole Black holes swallow all light, making them invisible. That’s what you’d think anyway, but astronomers thankfully know that this isn’t quite the case. They are, in fact, surrounded by a glowing disc of gas, which makes them visible against this bright background, like a black cat on a white sofa. And that’s how the Event Horizon Telescope has now succeeded in taking the first picture of a black hole. Researchers from the Max Planck Institute for Radio Astronomy in Bonn and the Institute for Radio Astronomy in the Millimeter Range (IRAM) in Grenoble, France, were among those making the observations. Photo: EHT Collaboration TEXT HELMUT HORNUNG n spring 2017, scientists linked up objects at extremely small angles of less tion of the Max Planck Institute for Ra- eight telescopes spread out over than 20 microarcseconds. With that dio Astronomy. In the 2017 observing one face of the globe for the first resolution, our eyes would see individ- session alone, the telescopes recorded time, forming a virtual telescope ual molecules on our own hands. approximately four petabytes of data. with an effective aperture close to This is such a huge volume that it was the Idiameter of the entire planet. -

Michal Zajaček – Curriculum Vitae

MPIfR Bonn Ph1, Universität zu Köln Michal Zajaček T +49(0)221/470-7788 u +49(0)221/470-6727 B [email protected] Curriculum Vitae Í www.astro.uni-koeln.de/∼zajacek Education September 17, PhD degree, IMPRS scholar at University of Cologne, 1. Physikalisches Institut and MPIfR, 2014– October Bonn, Germany, graduated as very good – sehr good with the grade 1.00. 12, 2017 December 15, Rigorosum examination – RNDr. (Czech Title for the Doctor of natural sciences), 2014 Charles University in Prague, Czech Republic. 2012–2014 Master of Science (Astronomy & Astrophysics), Charles University in Prague, Czech Republic, graduated with honours. 2009–2012 Bachelor of Science (General Physics), Charles University in Prague, Czech Republic, graduated with honours. 2004–2009 Abitur (Maturita), Evangelical Lyceum in Bratislava, Slovakia, all grades excellent. PhD Thesis Title Interaction between interstellar medium and black-hole environment Supervisor Prof. Dr. Andreas Eckart Advisors PD Dr. Silke Britzen, Prof. Dr. Vladimír Karas, Dr. Mónica Valencia-S., Prof. Dr. J. Anton Zensus Description The thesis deals with the transition region where the complex interstellar medium in the Galactic Centre meets a rather simple object at the very centre – most probably a black hole of 4 × 106 Solar masses characterized by only three classical parameters: mass, spin, and electric charge. Recently, a NIR-excess object named DSO/G2 was detected that is moving on a highly eccentric orbit, with the pericentre reached in 2014 at ∼ 2000 Schwarzschild radii. The monitoring, the analysis of NIR data, and the comparison with models have provided an unprecedented opportunity to constrain the properties of previously unexplored region around Sgr A* as well as to determine the nature of this enigmatic source. -

Radio Astronomy Infrastructures”

Community paper “Radio astronomy infrastructures” Eduardo Ros1, Dominik J. Schwarz2, & Christian Vocks3 on behalf of the German astronomical community 1: Max-Planck-Institut für Radioastronomie, Bonn; 2: Universität Bielefeld; 3: Leibniz-Institut für Astrophysik Potsdam Executive summary Radio astronomy has experienced phenomenal progress in recent years due to advances in digital technologies and processing speed, the development of new technologies, and the prospect for new powerful facilities A new generation of radio interferometers is opening new windows to the Universe. LOFAR, the world largest telescope, extended the classical radio window at low frequencies. ALMA started a new era at millimetre wavelengths and the planned SKA will revolutionize the sciences of the Universe, well beyond the traditional limits of astronomy. Radio astronomy research is making leaps with enhancements in resolution, sensitivity, and image fidelity. In Germany, the community has access to excellent facilities and training opportunities. The Effelsberg telescope remains the flagship of radio astronomical research at centimeter wavelengths and serves as a test bed for new technologies, LOFAR has notably expanded the German community and now includes six German stations and a LOFAR long term archive coordinated by the GLOW consortium. The SKA will be a transformational astronomical facility in the coming decade(s), and the German community is looking forward to broadly participate in SKA-enabled research. 1. Introduction Science and technique Radio astronomical techniques allow us to observe the sky at the largest accessible wavelength (or smallest accessible frequencies) of electromagnetic radiation (light). Radio astronomy was born in the 1930s and gave rise to several ground-breaking discoveries since, e.g. -

Event Horizon Telescope: the Black Hole Seen Round the World

EVENT HORIZON TELESCOPE: THE BLACK HOLE SEEN ROUND THE WORLD HEARING BEFORE THE COMMITTEE ON SCIENCE, SPACE, AND TECHNOLOGY HOUSE OF REPRESENTATIVES ONE HUNDRED SIXTEENTH CONGRESS FIRST SESSION MAY 16, 2019 Serial No. 116–19 Printed for the use of the Committee on Science, Space, and Technology ( Available via the World Wide Web: http://science.house.gov U.S. GOVERNMENT PUBLISHING OFFICE 36–301PDF WASHINGTON : 2019 COMMITTEE ON SCIENCE, SPACE, AND TECHNOLOGY HON. EDDIE BERNICE JOHNSON, Texas, Chairwoman ZOE LOFGREN, California FRANK D. LUCAS, Oklahoma, DANIEL LIPINSKI, Illinois Ranking Member SUZANNE BONAMICI, Oregon MO BROOKS, Alabama AMI BERA, California, BILL POSEY, Florida Vice Chair RANDY WEBER, Texas CONOR LAMB, Pennsylvania BRIAN BABIN, Texas LIZZIE FLETCHER, Texas ANDY BIGGS, Arizona HALEY STEVENS, Michigan ROGER MARSHALL, Kansas KENDRA HORN, Oklahoma RALPH NORMAN, South Carolina MIKIE SHERRILL, New Jersey MICHAEL CLOUD, Texas BRAD SHERMAN, California TROY BALDERSON, Ohio STEVE COHEN, Tennessee PETE OLSON, Texas JERRY MCNERNEY, California ANTHONY GONZALEZ, Ohio ED PERLMUTTER, Colorado MICHAEL WALTZ, Florida PAUL TONKO, New York JIM BAIRD, Indiana BILL FOSTER, Illinois JAIME HERRERA BEUTLER, Washington DON BEYER, Virginia JENNIFFER GONZA´ LEZ-COLO´ N, Puerto CHARLIE CRIST, Florida Rico SEAN CASTEN, Illinois VACANCY KATIE HILL, California BEN MCADAMS, Utah JENNIFER WEXTON, Virginia (II) CONTENTS May 16, 2019 Page Hearing Charter ..................................................................................................... -

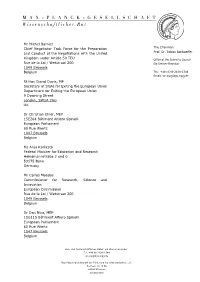

Mr Michel Barnier Chief Negotiator Task Force for the Preparation And

Mr Michel Barnier Chief Negotiator Task Force for the Preparation The Chairman and Conduct of the Negotiations with the United Prof. Dr. Tobias Bonhoeffer Kingdom under Article 50 TEU Office of the Scientific Council Rue de la Loi / Wetstraat 200 Ela Steiner-Brembor 1049 Brussels Belgium Tel.: +49 (0)89 2108-1349 Email: [email protected] Rt Hon David Davis, MP Secretary of State for Exiting the European Union Department for Exiting the European Union 9 Downing Street London, SW1A 2AG UK Dr Christian Ehler, MEP 15E264 Bâtiment Altiero Spinelli European Parliament 60 Rue Wiertz 1047 Brussels Belgium Ms Anja Karliczek Federal Minister for Education and Research Heinemannstraße 2 und 6 53175 Bonn Germany Mr Carlos Moedas Commissioner for Research, Science and Innovation European Commission Rue de la Loi / Wetstraat 200 1049 Brussels Belgium Dr Dan Nica, MEP 10G115 Bâtiment Altiero Spinelli European Parliament 60 Rue Wiertz 1047 Brussels Belgium Büro des Wissenschaftlichen Rates: Ela Steiner-Brembor Tel. +49 89 2108–1349 [email protected] Max-Planck-Gesellschaft zur Förderung der Wissenschaften e.V. Postfach 10 10 62 80084 München Deutschland - 2 - 19 June 2018 Dear Mr Michel Barnier, dear Rt Hon David Davis MP, dear Dr Christian Ehler MEP, dear Federal Minister Anja Karliczek, dear Commissioner Moedas, and dear Dr Dan Nica MEP, We the 153 undersigned Max Planck Directors write to share our view on the importance of securing a strong Brexit deal on science and innovation to support European science. It is important to find a way for the UK to participate in Horizon Europe as an associated country, and for researchers to move as freely as possible between the UK and EU. -

Broadband Multi-Wavelength Properties of M87 During the 2017 Event Horizon Telescope Campaign

The Astrophysical Journal Letters, 911:L11 (43pp), 2021 April 10 https://doi.org/10.3847/2041-8213/abef71 © 2021. The Author(s). Published by the American Astronomical Society. Broadband Multi-wavelength Properties of M87 during the 2017 Event Horizon Telescope Campaign J. C. Algaba1 , J. Anczarski2 , K. Asada3, M. Baloković4,5 , S. Chandra6 , Y.-Z. Cui7,8 , A. D. Falcone9 , M. Giroletti10 , C. Goddi11,12 , K. Hada7,8 , D. Haggard13,14 , S. Jorstad15,16 , A. Kaur9 , T. Kawashima17 , G. Keating18 , J.-Y. Kim19,20 , M. Kino21,22 , S. Komossa20 , E. V. Kravchenko10,23,24 , T. P. Krichbaum20 , S.-S. Lee19 , R.-S. Lu (路如森)20,25,26 , M. Lucchini27, S. Markoff27,28 , J. Neilsen2 , M. A. Nowak29 , J. Park30,31,244 , G. Principe10,32,33 , V. Ramakrishnan34 , M. T. Reynolds35 , M. Sasada21,36 , S. S. Savchenko37,38 , K. E. Williamson15 (The Event Horizon Telescope Collaboration) (The Fermi Large Area Telescope Collaboration) (H.E.S.S. Collaboration) (MAGIC Collaboration) (VERITAS Collaboration) (EAVN Collaboration) (See the end matter for the full list of authors including corresponding authors for the partner facilities.) Received 2020 December 25; revised 2021 March 14; accepted 2021 March 16; published 2021 April 14 Abstract In 2017, the Event Horizon Telescope (EHT) Collaboration succeeded in capturing the first direct image of the center of the M87 galaxy. The asymmetric ring morphology and size are consistent with theoretical expectations 9 for a weakly accreting supermassive black hole of mass ∼6.5 × 10 Me. The EHTC also partnered with several international facilities in space and on the ground, to arrange an extensive, quasi-simultaneous multi-wavelength campaign. -

Download (PDF)

HUMBOLDT No. 111 / 2020 No. KOSMOSResearch – Diplomacy – Internationality GERMAN CYBER VALLEYS DEUTSCHE Where the AI hotspots VERSION: are emerging BITTE WENDEN THE DESERT IS ALIVE How arid regions help to mitigate climate change Better connected! How cooperation benefits research KWEEN KONG: COMEDY AGAINST RACISM Photo: Humboldt Foundation / Nikolaus Brade HUMBOLDTIANS IN PRIVATE KWEEN KONG: COMEDY AGAINST RACISM The photo shows Lynette Mayowa Osinubi in a discussion was barrier-free access for people in wheelchairs and following a showing of her film, Acting White, in Berlin. translators for those who did not speak English. On stage, In the United States, “acting white” is a derogatory term Mayowa uses stand-up to expose the absurdities of a sex- used to refer to people of colour who supposedly betray ist and racist society and to discover the healing power of their own culture by fulfilling the behavioural norms laughter together with her audience. and expectations of white society. In the documentary, As a black woman living in Berlin, you are sometimes Mayowa, as she is known artistically, explores how this alienated from yourself, she feels, because you represent negative judgement affects one’s own identity and what the “other” in contrast to the majority white population. consequences it has for the psyche. During the fellowship, Mayowa came to the conclusion Mayowa comes from Atlanta, Georgia. In 2018, she that Berlin society is not as tolerant as many believe. She moved to Berlin as a German Chancellor Fellow to make intends to continue speaking out and encouraging people a documentary about the experiences of people of colour to find a voice for their very own stories – whether as a film in Germany. -

![Arxiv:1908.10767V3 [Astro-Ph.IM] 28 May 2021 Radboud University, Nijmegen, the Netherlands 2 Leonid I](https://docslib.b-cdn.net/cover/4802/arxiv-1908-10767v3-astro-ph-im-28-may-2021-radboud-university-nijmegen-the-netherlands-2-leonid-i-4144802.webp)

Arxiv:1908.10767V3 [Astro-Ph.IM] 28 May 2021 Radboud University, Nijmegen, the Netherlands 2 Leonid I

Experimental Astronomy manuscript No. (will be inserted by the editor) THEZA: TeraHertz Exploration and Zooming-in for Astrophysics An ESA Voyage 2050 White Paper Leonid I. Gurvits · Zsolt Paragi · Viviana Casasola · John Conway · Jordy Davelaar · Heino Falcke · Rob Fender · S´andorFrey · Christian M. Fromm · Cristina Garc´ıa Mir´o · Michael A. Garrett · Marcello Giroletti · Ciriaco Goddi · Jos´e-LuisG´omez · Jeffrey van der Gucht · Jos´eCarlos Guirado · Zolt´anHaiman · Frank Helmich · Elizabeth Humphreys · Violette Impellizzeri · Michael Kramer · Michael Lindqvist · Hendrik Linz · Elisabetta Liuzzo · Andrei P. Lobanov · Yosuke Mizuno · Luciano Rezzolla · Freek Roelofs · Eduardo Ros · Kazi L. J. Rygl · Tuomas Savolainen · Karl Schuster · Tiziana Venturi · Martina C. Wiedner · J. Anton Zensus Received: date / Accepted: date L.I. Gurvits Joint Institute for VLBI ERIC, Dwingeloo, EU / The Netherlands and Department of Astrodynamics and Space Missions, Delft University of Technology, The Netherlands E-mail: [email protected] ORCID: 0000-0002-0694-2459 Z. Paragi Joint Institute for VLBI ERIC, Dwingeloo, EU / The Netherlands V. Casasola INAF Institute of Radio Astronomy, Bologna, Italy J. Conway Onsala Space Observatory, Chalmers University, Sweden J. Davelaar Radboud University, Nijmegen, The Netherlands H. Falcke arXiv:1908.10767v3 [astro-ph.IM] 28 May 2021 Radboud University, Nijmegen, The Netherlands 2 Leonid I. Gurvits et al. R. Fender Oxford University, UK S. Frey Konkoly Observatory, Res. Centre for Astronomy and Earth Sciences, Budapest, Hungary and Institute of Physics, ELTE E¨otv¨osLor´andUniversity, Budapest, Hungary Ch.M. Fromm Goethe-Universit¨atFrankfurt, Germany C. Garc´ıaMir´o Joint Institute for VLBI ERIC, Madrid, EU / Spain M.A. Garrett Jodrell Bank Centre for Astrophysics, The University of Manchester, UK and Leiden Observatory, Leiden University, The Netherlands ORCID: 0000-0001-6714-9043 M.