Automotive Line Transient Protection Circuit

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Product Overview 6Pp 2012(Final Artwork) 29/10/2012 14:57 Page 2

DIO 3190 Product Overview 6pp 2012(Final Artwork) 29/10/2012 14:57 Page 2 DISCRETE PRODUCTS MOSFETS Broad range of N, P and complementary MOSFETs with BVDSS up to 450V IntelliFET range of self-protected MOSFETs packaged in a variety of leadless and surface mount packages RoHS and Halogen free materials to meet latest industry environmental requirements AECQ101 qualification to meet the high reliability demands of the automotive industry APPLICATIONS Discrete, Analog and Logic products SBR®(SUPER BARRIER RECTIFIER) from Diodes Incorporated provide Unique patented process that provides our customers with systems performance benefits over Schottky Diodes solutions and enable next generation PRODUCT VRRM up to 400V consumer, computer and IF up to 60A communication product designs. Low VF combined with high thermal Diodes Incorporated focuses on stability and reliability OVERVIEW high-growth end-markets including: Broad range of package options from tiny leadless packages to large through hole packages PC and notebooks Mobile phones LED TV and monitor Automotive BRINGING BIPOLAR TRANSISTORS CORPORATE HEADQUARTERS YOU NEXT Market leading technologies AND AMERICAS SALES OFFICE GENERATION Very low VCE(SAT) for improved efficiency in 4949 Hedgcoxe Road saturated switching applications Suite 200 Pre-build Transistors (digital) Plano, Texas 75024 DEVICES... 972-987-3900 USA Excellent gain hold up at high peak currents for improved driving of MOSFETs E-mail: [email protected] Low thermal resistance packaging for EUROPE SALES OFFICE space saving in linear operation Kustermann-Park Balanstrasse 59, 8th Floor D-81541 Munchen, Germany FUNCTION SPECIFIC ARRAYS Tel: (+49) 89 45 49 49 0 Relay Drivers E-mail: [email protected] Voltage Regulators ASIA SALES OFFICES Load Switches Email: [email protected] ASMCC's DIODES-TAIWAN (Application Specific Multi-Chip Circuits) 7F, No. -

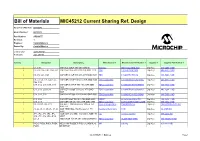

Bill of Materials MIC45212 Current Sharing Ref

Bill of Materials MIC45212 Current Sharing Ref. Design Document Number: 02-10570 Board Number: 04-10570 Part Number: ARD00777 Revision: 1 Engineer: Catalin Bibirica Drawn By: Catalin Bibirica M Creation Date: 12:45:31 PM Print Date: 2:21:20 PM Quantity Designator Description_ Manufacturer 1 Manufacturer Part Number 1 Supplier 1 Supplier Part Number 1 2 C1, C18 CAP ALU 220uF 35V 20% SMD E Nichicon UWT1V221MNL1GS Digi-Key 493-2205-1-ND 6 C2, C3, C36, C42, C50, C51 CAP CER 10uF 50V 20% X7S SMD 1210 TDK C3225X7S1H106M Digi-Key 445-4537-1-ND 4 C4, C5, C21, C23 CAP CER 0.1uF 50V 20% X7R SMD 0603 TDK C1608X7R1H104M Digi-Key 445-5098-1-ND 8 C6, C7, C8, C9, C24, C25, CAP CER 100uF 10V 20% X5R SMD 1206 TDK Corporation C3216X5R1A107M160AC Digi-Key 445-6007-1-ND C26, C32 5 C10, C12, C35, C44, C45 CAP CER 0.047uF 50V 10% X7R SMD TDK Corporation C1608X7R1H473K080AA Digi-Key 445-1313-1-ND 0603 4 C11, C13, C20, C33 CAP CER 1000pF 50V 20% X7R SMD TDK Corporation C1608X7R2A102K080AA Digi-Key 445-1298-1-ND 0603 3 C14, C19, C28 CAP CER 4700pF 50V 5% NP0 SMD 0603 TDK Corporation C1608C0G1H472J080AA Digi-Key 445-7400-1-ND 2 C15, C22 CAP CER 22pF 50V 5% C0G SMD 0603 KEMET C0603C220J5GACTU Digi-Key 399-1053-1-ND 2 C16, C17 CAP CER 1uF 35V 10% X7R SMD 0805 TDK Corporation CGA4J3X7R1V105K125AB Digi-Key 445-6962-1-ND 5 D3, D7, D8, D9, D10 DIO RECT 1N4148 855mV 300mA 75V Diodes Incorporated 1N4148WS-7-F Digi-Key 1N4148WS-FDICT-ND SOD-323 8 J1, J2, J3, J4, J5, J6, J7, J8 CON TERMINAL 15A Female 1x1 TH Keystone Electronics 8195 Digi-Key 36-8195-ND VERT 10 JP1, JP2, -

MM .1.20 Clking

CL King Market Maker List AAXN Axon Enterprise, Inc. CROX Crocs, Inc. HELE Helen of Troy Limited MPAA Motorcar Parts of America, Inc. SBAC SBA Communications Corporation ADBE Adobe Inc. CSCO Cisco Systems, Inc. HIBB Hibbett Sports, Inc. MRVL Marvell Technology Group Ltd. SBUX Starbucks Corporation ADSK Autodesk, Inc. CSOD Cornerstone OnDemand, Inc. HLIT Harmonic Inc. MSFT Microsoft Corporation SCVL Shoe Carnival, Inc. ADTN ADTRAN, Inc. CTAS Cintas Corporation HSIC Henry Schein, Inc. MU Micron Technology, Inc. SGMS Scientific Games Corp AGNC AGNC Investment Corp. CTSH Cognizant Technology Solutions Corporation HSII Heidrick & Struggles International, Inc. NDLS Noodles & Company SHOO Steven Madden, Ltd. AIMC Altra Industrial Motion Corp. CVLT Commvault Systems, Inc. HSKA Heska Corporation NEOG Neogen Corporation SMPL The Simply Good Foods Company ALGT Allegiant Travel Company DAKT Daktronics, Inc. HSON Hudson Global, Inc. NLOK NortonLifeLock Inc. SMRT Stein Mart, Inc. AMZN Amazon.com, Inc. DECK Deckers Outdoor Corporation IART Integra LifeSciences Holdings Corporation NTUS Natus Medical Incorporated SMSI Smith Micro Software, Inc. ANDE The Andersons, Inc. DENN Denny's Corporation ICON Iconix Brand Group, Inc. ON ON Semiconductor Corporation SNBR Sleep Number Corporation ANGO AngioDynamics, Inc. DIOD Diodes Incorporated IDXX IDEXX Laboratories, Inc. OSUR OraSure Technologies, Inc. SQBG Sequential Brands Group, Inc. ANSS ANSYS, Inc. DISCA Discovery, Inc. ILMN Illumina, Inc. Holdings PACB Pacific Biosciences of California, Inc. SRDX Surmodics, Inc. AOBC American Outdoor Brands Corporation DISH DISH Network Corporation IMBI iMedia Brands, Inc. PATK Patrick Industries, Inc. STAF Staffing 360 Solutions, Inc. AOSL Alpha and Omega Semiconductor Limited DLTR Dollar Tree, Inc. IOSP Innospec Inc. PDCO Patterson Companies, Inc. -

Analog | Discrete Logic | Mixed-Signal

Diodes Incorporated’s Discrete, Analog, Mixed-Signal and Logic products provide our customers with leading edge solutions for next generation systems. Discrete products include Bipolar Transistors, MOSFETs, Diodes and Rectifiers, Protection products and Functional Specific Arrays. Analog and Mixed-signal products cover these main areas: Power Management ICs, Standard Linear, LED Drivers, Sensors and Motor control, Switching, Signal Integrity, Connectivity and Timing products. Diodes Incorporated’s Logic products includes single gate, dual gate and standard logic gates as well as level translators, analog switches, registers and multiplexers. CORPORATE ASIA SALES OFFICES HEADQUARTERS AND Email: [email protected] AMERICAS SALES OFFICE 4949 Hedgcoxe Road DIODES-CHINA Suite 200 SHANGHAI OFFICE Plano, Texas 75024 Room 3001-3002, 972-987-3900 USA International Corporate City, Email: [email protected] No. 3000 Zhongshan North Road, Shanghai 200063, China ANA LOG | DISCRETE SILICON VALLEY OFFICE Tel: 86 21-5241-4882 1545 Barber Lane Milpitas, California 95035, USA SHENZHEN OFFICE Tel: 408-232-9100 16th Floor Skyworth Semiconductor LOGI C | MIXED -SIGNAL Design Building East Wing, EUROPE SALES OFFICE No.8 Gaoxin South 4th Road, Kustermann-Park Nanshan District, Shenzhen, Balanstrasse 59, 8th Floor China P.C: 518057 D-81541 Munchen, Germany Tel: 86 755-8828-4988 Tel: (+49) 89 45 49 49 0 Email: [email protected] DIODES-INDIA Email: [email protected] For information or DIODES-JAPAN literature, please visit Level 18, Yebisu Garden Place Tower www.diodes.com/contacts 4-20-3 Ebisu, Shibuya-ku Tokyo 150-6018 Japan Tel: 81-3-5789.5526 DIODES-KOREA 1601 ho, ParkView Tower Jeongja 1 dong, Bundang-gu Seongnam-si, Gyeonggi-do, Korea 463-811 Tel: 82-31-786-0434 DIODES-TAIWAN 7F, No. -

2020 Proxy Statement

DIODES INCORPORATED Notice of Annual Meeting of Stockholders To Be Held May 18, 2020 Notice is hereby given that the annual meeting (the “Meeting”) of the stockholders of Diodes Incorporated (the “Company”) will be held online via live audio webcast at www.proxydocs.com/DIOD on Monday, May 18, 2020, at 4:00 p.m. (Central Time). Due to the increasing public health impact of the Coronavirus outbreak and out of an abundance of caution to support the health and well-being of our employees, stockholders, and communities, the Meeting will be conducted completely virtually, via a live audio webcast; there will be no physical meeting location. Even though our Meeting is being held virtually, stockholders will still have the ability to participate in, hear others, and ask questions during the Meeting. The Meeting is being held for the following purposes: 1. Election of Directors. To elect seven persons to the Board of Directors of the Company, each to serve until the next annual meeting of stockholders and until their respective successors have been elected and qualified. The Board of Directors’ nominees are: C.H. Chen, Warren Chen, Michael R. Giordano, Keh-Shew Lu, Peter M. Menard, Christina Wen-Chi Sung and Michael K.C. Tsai. 2.Approval of Executive Compensation. To approve, on an advisory basis, the Company’s executive compensation. 3. Ratification of Appointment of Independent Registered Public Accounting Firm. To ratify the appointment of Moss Adams LLP as the Company’s independent registered public accounting firm for the fiscal year ending December 31, 2020. 4. Other Business. -

Published Schedule Exhibitors Forum 2018

Aussteller-Forum / Exhibitors' Forum Standnr. / stand no. Forum: 3A-610, 4-428 Dienstag - Tuesday, 27.02.2018 Mittwoch - Wednesday, 28.02.2018 Donnerstag - Thursday, 01.03.2018 Zeit - Time Halle 3A - hall 3A // Stand 3A-610 Halle 4- hall 4 // Stand 4-428 Halle 3A - hall 3A // Stand 3A-610 Halle 4- hall 4 // Stand 4-428 Halle 3A - hall 3A // Stand 3A-610 Halle 4- hall 4 // Stand 4-428 Affordable RF Tools, the ADALM-PLUTO When Iot Drives from Cost Saving to Extending Bluetooth with Mesh Networking Comprehensive USB Type-C™ SDR Revenue Boosting Semiconductor solutions from Diodes Incorporated including controllers, signal conditioners, high speed multiplexers, and 09.30 - power management devices 10.00 Uhr Robin Getz Scott Cooper Analog Devices, sponsored by Mouser Sarun Kub Silicon Labs, sponsored by Mouser Kay Annamalai Electronics Inc. Robustel Ltd. Electronics Inc. Diodes Incorporated 3A-111 3-333 3A-111 3A-431 Getting Agile in Embedded Development Measurement and Control Systems Software is eating the world. The Static Analysis++ Understanding processor security Mastering your Multicore project with using Simulation Converge: New Technologies to Enable Embedded World that is. technologies and how to apply them Silexica’s SLX The IIoT 10.00 - 10.30 Uhr Dr. Jakob Engblom Sunaina Kavi Art Dahnert Mark Hermeling Joseph Yiu Max Odendahl Intel Corp. National Instruments Germany GmbH Synopsys Inc. GrammaTech, Inc Arm Ltd. Silexica GmbH 1-338 4-108 4-520 4-328 4-140 4-358 OPC UA TSN in der industriellen Get ready for Automated Debugging and Towards the Zero-Delay Supply Chain Agiles Testing – Den Letzten beißen die Achieve accurate and fast power integrity Linux - Started as server operating system Kommunikation Test of production code with Universal Solution Hunde nicht mehr measurements with the right oscilloscope and finally established as universal platform Debug Engine and power rail probe solution for embedded systems 10.30 - 11.00 Uhr Armin Pühringer Jens Braunes Dr. -

Precision Timing & Connectivity

A PRODUCT LINE OF DIODES INCORPORATED E NABLING SERIAL CONNECTIVITY PRECISION TIMING & CONNECTIVITY diodes.com PRECISION TIMING & CONNECTIVITY COMPANY OVERVIEW Diodes Incorporated enables serial connectivity with the industry’s most complete solutions for the computing, communications, consumer, embedded, and automotive market segments with products spanning analog, digital and mixed-signal integrated DIODES INCORPORATED’S PRODUCTS circuits, power management solutions and quartz-based frequency control products ARE DESIGNED FOR HIGH PERFORMANCE, (FCP). Pericom, a product line of Diodes Incorporated, supplies essential solutions for ACROSS A WIDE RANGE OF EXISTING the timing, switching, bridging and conditioning of high-speed signals required by AND EMERGING APPLICATIONS. today’s ever increasing speed and bandwidth demanding applications. Diodes Incorporated is a leading global manufacturer and supplier of high-quality WHY DIODES? application specific standard products § Broad portfolio of vertically integrated connectivity, signal integrity switching within the broad discrete, logic, analog and and timing solutions mixed-signal semiconductor markets. § Standards compliance, increased system reliability, and lowered system costs Diodes serves the consumer electronics, computing, communications, industrial, § Unique signal conditioning solutions enable the full potential of the latest and automotive markets. high-speed serial protocols § Total “Segment Solutions” approach offers multiple products optimized Diodes’ products include diodes, rectifiers, for specific market segments transistors, MOSFETs, protection devices, function-specific arrays, single gate logic, amplifiers and comparators, Hall-effect and TIMING CONNECTIVITY temperature sensors, power management Diodes Incorporated’s broad offering Our portfolio of ICs with protocol specific devices, including LED drivers, of timing products enables us to be your functionality for high-speed standards AC-DC converters and controllers, DC-DC complete timing solution partner. -

Design Tips Design Tips

Empowering Global Innovation December 2008 Design Tips Special Report - Renewable Energy ISSN: 1613-6365 Organic LED Drivers Dilbert – 64 Viewpoint Enhanced Image Quality, Energy-Effi cient Displays Gloom is not an option, By Cliff Keys, Editor-in-Chief, PSDE ...................................................................................................................................4 High-Performance Analog>>Your Way™ Industry News Tony Armstrong Appointed as Linear’s Director of Product Marketing .....................................................................................................................6 CamSemi named ‘Start-Up of the Year’ 2008 ...........................................................................................................................................................6 Digi-Key Agreement with Tyco Expanded Worldwide ...............................................................................................................................................6 Applications Diodes Incorporated Wins Environmental Award ......................................................................................................................................................8 Fuji Electric and Semikron Team-Up .........................................................................................................................................................................8 – OLED displays up to 2.5” Inauguration of Solar Roof at Goethe-Institut, Bangalore .........................................................................................................................................8 -

HV9805 230VAC SEPIC Evaluation Board User's Guide

HV9805 230VAC SEPIC Evaluation Board User’s Guide 2015 Microchip Technology Inc. DS50002362A Note the following details of the code protection feature on Microchip devices: • Microchip products meet the specification contained in their particular Microchip Data Sheet. • Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions. • There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property. • Microchip is willing to work with the customer who is concerned about the integrity of their code. • Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as “unbreakable.” Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act. Information contained in this publication regarding device Trademarks applications and the like is provided only for your convenience The Microchip name and logo, the Microchip logo, dsPIC, and may be superseded by updates. -

Circuit for Protecting Ads131m0x ADC from Electrical Overstress

www.ti.com Analog Engineer's Circuit Circuit for protecting ADS131M0x ADC from electrical overstress Data Converters Dale Li Specifications on ADS131M0x Minimum (AGND = Maximum (AVDD = 0V) 3.3V) Absolute Maximum Ratings Analog Input Voltage (VIN_Abs) –1.6V +3.6V Analog Input Current (IIN_Abs) –10mA +10mA Analog Input Range Differential Input –1.2V +1.2V (VIN at Gain=1 and VREF=1.2 V) Single-ended Input –1.2V +1.2V Design Description This circuit shows an external solution to protect ADS131M02, ADS131M03, ADS131M04, ADS131M06, and ADS131M08 Delta-Sigma ADCs from electrical overstress (EOS). The protection is implemented with external Schottky diodes and switching diodes. This document shows how the Schottky diodes and switching diodes can be used with current-limiting resistors to implement the external protection clamp for the overstress signal and maintain a minimum impact on performance, especially signal-to-noise ratio (SNR) and total harmonic distortion (THD). This circuit is useful in the following end equipment: Battery test, Semiconductor test, Electricity meter, Power quality analyzer, and Power quality meter. For protecting high-voltage SAR ADCs from electrical overstress, see Input protection for high-voltage ADC circuit with TVS diode and Circuit for protecting ADC with TVS diode and PTC fuse. For protecting low-voltage SAR ADC from electrical overstress, see Circuit for protecting low-voltage SAR ADCs from electrical overstress with minimal impact on performance. The following figure comes from the Digital Control Reference Design for Cost-Optimized Battery Test Systems Reference Design in the Battery Test application. During an electrical overstress event, this circuit can potentially apply damaging voltages and currents to the inputs of the ADS131M08 ADC: the voltage from the amplifiers (INA821 and TLV171) can reach the power supply voltages (+10V or –5V), and the overstress current from the amplifiers can be as high as the short-circuit current for each respective amplifier. -

Investor Overview

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 SCHEDULE 14A INFORMATION Proxy Statement Pursuant to Section 14(a) of the Securities Exchange Act of 1934 (Amendment No. ) Filed by the Registrant ☒ Filed by a Party other than the Registrant ☐ Check the appropriate box: ☐ Preliminary Proxy Statement ☐ Confidential, for Use of the Commission Only (as permitted by Rule 14a-6(e)(2)) ☒ Definitive Proxy Statement ☐ Definitive Additional Materials ☐ Soliciting Material under Rule 14a-12 DIODES INCORPORATED (Name of registrant as specified in its charter) (Name of person(s) filing proxy statement, if other than the registrant) Payment of Filing Fee (Check the appropriate box): ☒ No fee required. ☐ Fee computed on table below per Exchange Act Rules 14a-6(i)(4) and 0-11. (1) Title of each class of securities to which transaction applies: (2) Aggregate number of securities to which transaction applies: (3) Per unit price or other underlying value of transacon computed pursuant to Exchange Act Rule 0-11 (set forth the amount on which the filing fee is calculated and state how it was determined): (4) Proposed maximum aggregate value of transaction: (5) Total fee paid: ☐ Fee paid previously with preliminary materials. ☐ Check box if any part of the fee is offset as provided by Exchange Act Rule 0-11(a)(2) and idenfy the filing for which the offseng fee was paid previously. Identify the previous filing by registration statement number, or the Form or Schedule and the date of its filing. (1) Amount Previously Paid: (2) Form, Schedule or Registration Statement No.: (3) Filing Party: (4) Date Filed: DIODES INCORPORATED Notice of Annual Meeting of Stockholders To Be Held May 22, 2018 Noce is hereby given that the annual meeng (the “Meeng”) of the stockholders of Diodes Incorporated (the “Company”) will be held at the Company’s corporate headquarters, located at 4949 Hedgcoxe Road, Plano, Texas 75024, on Tuesday, May 22, 2018, at 10:00 a.m. -

Investor Overview

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 8-K CURRENT REPORT Pursuant to Section 13 or 15(d) of the Securities Exchange Act of 1934 February 9, 2009 Date of Report (Date of earliest event reported) DIODES INCORPORATED (Exact name of registrant as specified in its charter) Delaware 002-25577 95-2039518 (State or other (Commission File Number) (I.R.S. Employer jurisdiction of Identification No.) incorporation) 15660 North Dallas Parkway, Suite 850 75248 Dallas, TX (Zip Code) (Address of principal executive offices) (972) 385-2810 (Registrant’s telephone number, including area code) Check the appropriate box below if the Form 8-K filing is intended to simultaneously satisfy the filing obligation of the registrant under any of the following provisions: o Written communications pursuant to Rule 425 under the Securities Act (17 CFR 230.425) o Soliciting material pursuant to Rule 14a-12 under the Exchange Act (17 CFR 240.14a-12) o Pre-commencement communications pursuant to Rule 14d-2(b) under the Exchange Act (17 CFR 240.14d-2(b)) o Pre-commencement communications pursuant to Rule 13e-4(c) under the Exchange Act (17 CFR 240.13e-4(c)) Item 2.02 Results of Operations and Financial Condition. On February 9, 2009, Diodes Incorporated issued a press release announcing fourth quarter 2008 results. A copy of the press release is attached as Exhibit 99.1. On February 9, 2009, Diodes Incorporated hosted a conference call to discuss its fourth quarter 2008 results. A recording of the conference call has been posted on its website at www.diodes.com.