PHY Interface for the PCI Express*, SATA, USB 3.1, Displayport

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

TUSB1046-DCI USB Type-C™ Displayport™ ALT Mode 10 Gbps Linear Redriver Crosspoint Switch 1 Features 2 Applications

Product Order Technical Tools & Support & Folder Now Documents Software Community TUSB1046-DCI SLLSEW2D –AUGUST 2016–REVISED APRIL 2019 TUSB1046-DCI USB Type-C™ DisplayPort™ ALT Mode 10 Gbps Linear Redriver Crosspoint Switch 1 Features 2 Applications 1• USB Type-C crosspoint switch supporting • Tablets – USB 3.1 SSP + 2 DisplayPort lanes • Notebooks – 4 DisplayPort lanes • Desktops • USB 3.1 Gen 1/Gen 2 up to 10 Gbps • Docking stations • DisplayPort 1.4 up to 8.1 Gbps (HBR3) • VESA® DisplayPort Alt mode DFP redriving 3 Description crosspoint switch supporting C, D, E and F The TUSB1046-DCI is a VESA USB Type-C™ Alt configurations Mode redriving switch supporting USB 3.1 data rates up to 10 Gbps and DisplayPort 1.4 up to 8.1 Gbps for • Ultra-low-power architecture downstream facing port (Host). The device is used for • Linear redriver with up to 14 dB equalization configurations C, D, E, and F from the VESA • Transparent to DisplayPort link training DisplayPort Alt Mode on USB Type-C Standard Version 1.1. This protocol-agnostic linear redriver is • Automatic LFPS de-emphasis control to meet also capable of supporting other USB Type-C Alt USB 3.1 certification requirements Mode interfaces. • Configuration through GPIO or I2C The TUSB1046-DCI provides several levels of • Hot-plug capable receive linear equalization to compensate for cable • Industrial temperature range: -40ºC to 85ºC and board trace loss due to inter-symbol interference (TUSB1046I-DCI) (ISI). The device operates on a single 3.3 V supply • Commercial temperature range: 0ºC to 70ºC and comes in a commercial temperature range and industrial temperature range. -

USB-C to Displayport Adapter with Alternate Mode

USB-C to Displayport Adapter with Alternate Highlights Mode - DP 1.2, 4K60 ● Supports USB DisplayPort Alternate Mode for transmitting MODEL NUMBER: U444-06N-DP-AM audio/video ● Delivers UHD picture quality at resolutions up to 4096 x 2160 (4K) @ 60 Hz ● Compact and easy to carry in a pocket, purse or laptop bag ● Reversible USB-C plug connects in either direction ● Plug-and-play operation with no software or drivers required System Requirements ● Source device with USB-C or Connects your existing 4K DisplayPort TV, monitor or projector to the USB-C or Thunderbolt 3 port on Thunderbolt 3 port that supports your tablet, laptop, notebook, MacBook, Chromebook, smartphone or PC. USB DisplayPort Alternate Mode Description The U444-06N-DP-AM USB 3.1 Gen 1 USB-C to DisplayPort 4K Adapter (M/F) helps you transmit digital ● Display device with DisplayPort audio and 4K video from your tablet, laptop, Chromebook, MacBook, smartphone or PC to a DisplayPort- enabled television, monitor or projector. It’s an ideal tool for giving video presentations in conference input rooms and classrooms, editing multiple documents on a larger screen, or streaming video for digital signage in crystal-clear 4K. Package Includes With a source device that also supports USB DisplayPort Alternate Mode, you can extend video from your primary display to another, duplicate the same video on both displays, or change the second display to ● U444-06N-DP-AM USB 3.1 Gen your primary. 1 USB-C to DisplayPort 4K The plug-and-play U444-06N-DP-AM requires no software, drivers or external power. -

USB Type-C® System Overview Enabling Connections for Data, Display and Power

USB Type-C® System Overview Enabling connections for data, display and power Brad Saunders – Co-Chair, USB Type-C Working Group USB Developer Days 2019 – Taipei, Taiwan November 19, 2019 USB Type-C®, USB-C® and USB4™ are trademarks of the Universal Serial Bus Implementers Forum (USB-IF). Thunderbolt™ is a trademark of Intel Corporation. All product names are trademarks, registered trademarks, or service marks of their respective owners. USB Implementers Forum © 2019 Performance Power Delivers up to 40 Gbps – Delivers up to 100W – USB 2.0, supporting all of your data USB Power power and charging for transfer and display needs USB 3.2 and all your devices Delivery USB4™ USB Type-C® Cable & Connector Convenience Robust, slim connector with reversible plug orientation and cable direction 2 USB Implementers Forum © 2019 USB4™ – Extending USB on Multiple Vectors • Enables the next generation of USB performance over existing USB Type-C cable plug/wires • Doubles performance and extends protocol to display and load/store applications • New signaling rates and encoding for use on existing cables • Gen2 (10 Gbps) works over all existing full-featured cables including Gen1 cables • Gen3 (20 Gbps) requires higher performance Gen3 cables View into the plug • USB4 builds on USB 3.2 • Enhanced SuperSpeed USB tunneling on a new USB4-specific transport • DisplayPort and PCIe supported via separate tunnels with configurable bandwidth management Lane 1 Lane 0 • USB4 discovery and entry relies on USB PD protocol Dual-lane operation • USB4 power requires -

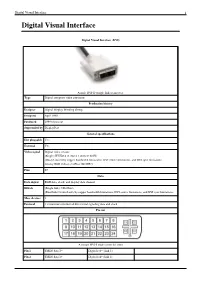

Digital Visual Interface (DVI)

Digital Visual Interface 1 Digital Visual Interface Digital Visual Interface (DVI) A male DVI-D (single link) connector. Type Digital computer video connector Production history Designer Digital Display Working Group Designed April 1999 Produced 1999 to present Superseded by DisplayPort General specifications Hot pluggable Yes External Yes Video signal Digital video stream: (Single) WUXGA (1,920 × 1,200) @ 60 Hz (Dual) Limited by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Analog RGB video (−3 dB at 400 MHz) Pins 29 Data Data signal RGB data, clock, and display data channel Bitrate (Single link) 3.96 Gbit/s (Dual link) Limited only by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Max. devices 1 Protocol 3 × transition minimized differential signaling data and clock Pin out A female DVI-I socket from the front Pin 1 TMDS data 2− Digital red− (link 1) Pin 2 TMDS data 2+ Digital red+ (link 1) Digital Visual Interface 2 Pin 3 TMDS data 2/4 shield Pin 4 TMDS data 4− Digital green− (link 2) Pin 5 TMDS data 4+ Digital green+ (link 2) Pin 6 DDC clock Pin 7 DDC data Pin 8 Analog vertical sync Pin 9 TMDS data 1− Digital green− (link 1) Pin 10 TMDS data 1+ Digital green+ (link 1) Pin 11 TMDS data 1/3 shield Pin 12 TMDS data 3- Digital blue− (link 2) Pin 13 TMDS data 3+ Digital blue+ (link 2) Pin 14 +5 V Power for monitor when in standby Pin 15 Ground Return for pin 14 and analog sync Pin 16 Hot plug detect Pin 17 TMDS data 0− Digital blue− (link 1) and digital sync Pin 18 TMDS data 0+ Digital blue+ (link 1) and digital sync Pin 19 TMDS data 0/5 shield Pin 20 TMDS data 5− Digital red− (link 2) Pin 21 TMDS data 5+ Digital red+ (link 2) Pin 22 TMDS clock shield Pin 23 TMDS clock+ Digital clock+ (links 1 and 2) Pin 24 TMDS clock− Digital clock− (links 1 and 2) C1 Analog red C2 Analog green C3 Analog blue C4 Analog horizontal sync C5 Analog ground Return for R, G, and B signals Digital Visual Interface (DVI) is a video display interface developed by the Digital Display Working Group (DDWG). -

Multiport M.2 NGFF PS/2 HDMI Firewire Network SATA IDE Mini

Connection-Know-How www.delock.com RF Memory SATA Displayport Graphics / Video radio frequency technology Cards SATA SATA male female Dualport HDMI + Displayport Cinch Video Cinch Video Cfast female female male female N plug F plug eSATA SATA male female S-Video female Compact Flash female Sub-D Displayport Displayport male female eSATAp eSATAp TNC Coaxial NEW male female Scart male plug plug Serial Serial mini mini 9 pin 9 pin Displayport Displayport Contact Golden Strip male female male female eSATApd male SD SD 4.0 DMS male DMS female female female RP-TNC RP-TNC UHS-I-Card UHS-II-Card plug jack Slim SATA 13 pin male Null Modem 8 pin male HDMI VGA Micro SATA 16 pin VGA Parallel 25 pin male female M.2 NGFF male male HDMI A HDMI A FME FME male female plug jack M.2 NGFF Key B+M Micro SATA 16 pin female Parallel 25 pin female VHDCI-68 male HDMI HDMI mini-C mini-C M.2 NGFF Key B male female SATA 22 pin male BNC BNC Sub-D 15 pin Gameport VHDCI-68 female plug jack male M.2 NGFF Key M SATA 22 pin female HDMI HDMI micro-D micro-D male female Sub-D 15 pin Gameport SMA SMA female LFH 60 male plug jack mini PCIe SAS male Multiport Sub-D 37 pin male PS/2 miniPCIe female mSATA female RP-SMA RP-SMA NEU plug jack BNC Stecker miniPCIe male mSATA male Sub-D 37 pin female Multiport female BNC Buchse PS/2 female SMB SMB plug jack Audio USB Mobile DVI FireWire MCX MCX plug jack Audio Stereo iPhone 30 pin female DVI-D Dual Link 24+1 USB 2.0 A USB 2.0 A FireWire A FireWire A female male male female 6 pin 6 pin male female UHF UHF Stereo 3 pin Stereo 3 pin -

GUD3C05 Datasheet

GUD3C05 USB-C Docking Station with Power Delivery 3.0 Instantly dock up to 10 devices Charge laptop & devices with up to100W pass-through1&2 Fast Role Swap provides safe operation for connected devices during power changes Versatile video options: HDMI (4K), Mini DisplayPort (4K) or VGA (1080p) Dual video outputs available via HDMI & Mini DisplayPort for up to 1080p @60Hz3 Laptop Expandability for up to 10 Devices Connect and expand your USB-C laptop to accommodate up to 10 must-need devices. Quickly turn your MacBook or Windows laptop or tablet into a powerhouse of productivity through a single USB-C cable. Connect a wide variety of devices such as a full- sized keyboard and mouse, an external hard drive, a printer, a microphone, headphones or speaker set, and transfer files through its built-in SD/MicroSD card reader. Enjoy the flexibility of the dock's versatile video options including 4K resolutions through the HDMI or Mini DisplayPort connections or 1080p video through the VGA port. Quickly connect up to 10 devices through one USB-C cable Works with the latest USB-C iPad Pro (2018 late) under mirror-mode Charge laptop & devices with up to100W pass-through1&2 Fast Role Swap provides safe operation for connected devices during 1 Power Delivery 3.0 pass0through offers up to 100W of charging power power changes utilizing the laptop's USB-C power adapter. USB-C power adapter not Versatile video options: HDMI (4K), Mini DisplayPort (4K) or VGA included. (1080p) 2 Maximum of up to 85W of power can be delivered to the laptop after Dual video outputs available via HDMI & Mini DisplayPort for up to deduction of 15W used by the docking station. -

Thunderbolt™-To- 8Gb/S Fibre Channel Desklink™ Device Thunderlink™ FC 1082

Tech Sheet Thunderbolt™-to- 8Gb/s Fibre Channel Desklink™ Device ThunderLink™ FC 1082 ATTO’s 8Gb/s Fibre Channel to Thunderbolt Desklink Technical Features Device product provides the highest performing SAN • Dual 8Gb/s Fibre Channel Ports storage connectivity for content creation, streaming • (2) Optical SFPs+ included media and high performance and low latency workflows. • Dual 10Gbps Thunderbolt with Display Industry Proven Technology Port and PCIe Support ATTO has over 25 years of experience developing first-to-market high performance and • Thunderbolt certified for Mac and PC reliable storage connectivity solutions for customers. ATTO ThunderLink Fibre Channel products now provide creative professionals using Thunderbolt-enabled hosts, cost • Dual ports enable daisy-chaining up effective access to storage not previously available using FireWire or USB. The integrated to six devices family of ThunderLink products boasts an extensive list of customer design wins and • Exclusive Advanced Data Streaming certifications with respected industry partners. (ADS™) Technology Flexible Connectivity Solutions • ATTO ConfigTool for customized performance settings With dual channel configuration, and support for load balancing and failover, the 8Gb/s Fibre Channel Desklink Devices are an ideal solution for users looking to achieve the highest • Proven interoperable with leading I/O and data throughput for advanced video and access to IT applications. ThunderLink storage hardware and software 8Gb/s Fibre Channel Desklink Devices offer driver support for Mac OS® X 10.6.8 and later vendors and Windows® 7 and 8.1 (Linux® when Thunderbolt enabled platforms become available), • Complete SAN connectivity when providing a single connectivity solution for customers with heterogeneous operating combined with ATTO FibreConnect system environments. -

USB4 Interop Test Specification

USB Implementers Forum USB4 Interoperability Test Procedures Revision 1.0 – June 2020 Copyright © 2020, USB Implementers Forum, Inc. All rights reserved THIS SPECIFICATION IS PROVIDED TO YOU “AS IS” WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON- INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OR IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. THE PROVISION OF THIS SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS. USB Type-C™, USB-C™ and USB4™ are trademarks of the Universal Serial Bus Implementers Forum (USB-IF). Thunderbolt™ is a trademark of Intel Corporation. All product names are trademarks, registered trademarks, or service marks of their respective owners. 2 Contents SUMMARY OF CHANGES........................................................................................................................ 6 RELATED DOCUMENTS .......................................................................................................................... 7 TERMS AND ABBREVIATIONS .............................................................................................................. 8 1. INTEROPERABILITY TESTING ................................................................................................... 9 1.1. EQUIPMENT .................................................................................................................................10 -

Drivestation™ Ultra Series PERFORMANCE MATTERS HD-D/R6, HD-HN/R6

DriveStation™ Ultra Series PERFORMANCE MATTERS HD-D/R6, HD-HN/R6 BLAZING FAST SPEEDS & LARGEST CAPACITY DESKTOP DAS IN THE INDUSTRY Bualo's DriveStationTM Ultra is a high performance, high capacity direct attached storage solution ideal for businesses that demand fast data transfer speeds for large les, such as 4k high resolution video. The DriveStation Ultra is available in either a ten-drive or six-drive desktop model, with capacities ranging from 12 TB to 80 TB, the largest capacity desktop DAS available today. With multi-interface support, Mac® users can experience blazing fast speeds using a Thunderbolt 2 connector, while PC users can also connect through high-speed USB 3.0 and eSATA interfaces. RAID 6 support provides extra protection that allows up to two hard drives to fail without data loss. The DriveStation Ultra is equipped with either enterprise or NAS hard drives designed for continuous operation. Extremely fast data transfers for both Mac and PCs and safe data storage with RAID options make the DriveStation Ultra an ideal solution for storing large les quickly and safely. FEATURES THUNDERBOLT 2 SPEEDS HIGH PERFORMANCE HARD DRIVES The DriveStation Ultra comes equipped with two The DriveStation Ultra features 10 helium-lled enterprise Thunderbolt 2 connectors, allowing Mac users to experience hard drives for the 80 TB model, and 6 or 10 NAS hard drives write speeds up to 1243 MB/s using RAID 0. With the fastest for the 12 TB, 24 TB & 40 TB models. These high performance connection available, it’s an ideal solution for transferring hard drives are optimized for continuous 24/7/365 operation and storing large les such as 4k high resolution videos. -

PPC7A10 at Our Website: Click HERE Powerx Product Manual PPC7A

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the Abaco Systems / Radstone PPC7A10 at our website: Click HERE PowerX Product Manual PPC7A Appendix C - PPC7A This appendix contains hardware information for PPC7A boards. The information contained in this document must be used in conjunction with PowerX Quick Start, PowerX User Guides and/or the PowerX product Manual. Link Settings...................................................................................................................................... C-3 Default Link Settings............................................................................................................................... C-3 RTC Standby Supply Voltage Link (E1)................................................................................................. C-4 FLASH Write Enable Links (E3 and E9)............................................................................................... -

HP Z440, Z640, and Z840 Workstation Series Maintenance and Service Guide

HP Z440, Z640, and Z840 Workstation Series Maintenance and Service Guide Copyright Information Warranty Trademark Credits © Copyright 2014, 2016 HP Development The information contained herein is subject to Microsoft and Windows are U.S. registered Company, L.P. change without notice. The only warranties for trademarks of the Microsoft group of HP products and services are set forth in the companies. Third Edition: November 2016 express warranty statements accompanying such products and services. Nothing herein Intel, Intel Xeon, and Thunderbolt are First Edition: October 2014 should be construed as constituting an trademarks of Intel Corporation in the U.S. and other countries. Part Number: 748721-004 additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein. Bluetooth is a trademark owned by its proprietor and used by Hewlett-Packard Windows 8: Not all features are available in all Company under license. editions of Windows 8. This workstation may require upgraded and/or separately purchased ENERGY STAR is a registered trademark owned hardware, drivers, and/or software to take full by the U.S. Environmental Protection Agency advantage of Windows 8 functionality. Go to (EPA). http://www.microsoft.com for details. Red Hat is a registered trademark of Red Hat, Windows 7: This workstation may require Inc. in the United States and other countries. upgraded and/or separately purchased hardware and/or a DVD drive to install the Windows 7 software and take full advantage of Windows 7 functionality. Go to http://www.microsoft.com for details. About this guide This guide provides service and maintenance information, technical details and configuration guidance for the HP Z440, Z640, and Z840 Workstations. -

Apogee Ensemble Thunderbolt Audio Interface

Apogee Ensemble Thunderbolt Audio Interface User’s Guide Fall 2014 Contents Overview!...........................................................................................................5 Introduction!................................................................................................................5 Features!.......................................................................................................................5 Package Contents!......................................................................................................6 Ensemble Thunderbolt Panel Tour!...........................................................................7 Front Panel!.................................................................................................................7 Rear Panel!..................................................................................................................8 Display!........................................................................................................................9 Input Settings Display Screen!..................................................................................9 Getting Started!...............................................................................................10 Precautions when powering Ensemble On/Off!......................................................10 Thunderbolt Notes!....................................................................................................10 Ensemble Software!..................................................................................................11