Fundamental Performance Differences Between CMOS and CCD Imagers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Return of Organization Exempt from Income Tax

0• • -19/ OMB No 1545-0047 Return of Organization Exempt From Income Tax 009 Form 990 Under section 501(c), 527, or 4947 (a)(1) of the Internal Revenue Code (except black lung benefit trust or private foundation ) • . - . Department of the Treasury Internal Revenue Service ► The organization may have to use a copy of this return to satisfy state reporting requirements . A For the 2009 calendar year or tax year beg inning 7/1/2009 and endin 6/30/2010 Please B Check if applicable C Name of organization Trustees of Princeton Universi ty-Alumni Organizations and Classes D Employer identification number - use IRS q Address change label or Doing Business As 22-2711242 q Name change print or Number and street (or P 0 box if mall is not delivered to street address) Room/suite E Telephone number typ q Initial return See c/o Princeton Universi ty, 701 Carneg ie Center 438 (609) 258-3080 q Terminated Specific City or town , state or country, and ZIP + 4 lnstruc- q Amended return tions Princeton NJ 08540 G Gross receipts $ 5 , 529 , 459 q Application pending F Name and address of principal officer H(a) Is this a group return for affiliates? qX No IShirley M . Tilg hman , One Nassau Hall , Princeton , NJ 08544 H(b) Are all affiliates Included? q Yes 191 No I Tax-exempt status q 501 (c) ( 3) ' (Insert no) q 4947 (a)(1) or q 527 If "No," attach a list (see instructions) J Website : ► www p rinceton edu H(c) Grou exem ption number ► 9126 q q q q K Form of organization Corporation Trust Association Other ► L Year of formation M State of legal domicile Summa ry 1 Briefly describe the organization ' s mission or most significant activities . -

Alumni Gather Under the Tuscan Sun

FALL/WINTER 2007 the Alumni Magazine of NYU Stern STERNbusiness ALUMNI GATHER UNDER THE TUSCAN SUN The Business of Business Education ■ The Alchemy of Private Equity ■ Guidance on Earnings Guidance ■ Global Attitudes on Capitalism ■ Fashioning an Apparel Business ■ Showtime’s Program for Success a letter fro m the dean The end of summer pro- we’ve seen that sharp insights can bear fruit in unan- vides us with an opportuni- ticipated ways. That’s certainly been the case with the ty to take a breath, to look long-running collaboration of Professors Marty back, and to prepare for the Gruber and Ned Elton (page 52), whose portfolio academic year. As I start my research has yielded countless applications. For sixth year as dean at NYU another example of how the research we conduct does Stern, I realize that I now work in the broader world, I’d direct you to Professor have a great deal to look back on – and a great deal to Robert Engle’s five-part series on volatility (page 22) look forward to. In recent years, one of our goals has that first appeared this summer on the Financial been to build a greater sense of community – among Times’ website – FT.com. It’s a brilliant short course students, faculty, and alumni. And the Global Alumni taught to a massive audience by a Nobel laureate. Conference, which we held in June in Florence (page Research allows Stern to function as an ideas incu- 12), highlighted how far we’ve come. The conference bator, cultivating new insights into the business world. -

Resume of Dr. D. Misra August 2020

Resume of Dr. D. Misra August 2020 Durgamadhab (Durga) Misra Department of Electrical and Computer Engineering, New Jersey Institute of Technology, University Heights Newark, NJ 07102, Email: [email protected] Phone: (973) 596-5739 Fax: (973) 596-5680 Fellow of the Electrochemical Society Fellow of IEEE Education Ph.D., Electrical Engineering, University of Waterloo, Waterloo, Canada, 1988 M.S., Management, New Jersey Institute of Technology, 1997 M.A.Sc., Electrical Engineering, University of Waterloo, Waterloo, Canada, 1985 M.Tech., Solid-State, IIT Delhi, India, 1983 M.S., Physics, Utkal University, Bhubaneswar, India, 1981 B.S., Physics, Utkal University, Bhubaneswar, India, 1978 Academic Experience New Jersey Institute of Technology, 2011- Associate Chair for Graduate Studies, ECE Dept Newark, NJ 2006 – 2008 Associate Chair for Graduate Studies, ECE Dept 2002 - Professor, Electrical & Computer Eng. Dept. 2002 – Director, Graduate Program: MS Electrical Eng 1993 - 2002 Associate Professor, Elect & Comp Eng Dept 1996 - 1997 Director, Microelectronics Research Center, 1988 - 1993 Assistant Professor, Elect & Comp Eng Dept Indian Institute of Science, Bangalore, India 2017 Prof. Ramakrishna Rao Visiting Endowed Chair Professor at Center for Nano Science and Engineering (CeNSE) Furtwangen University, Furtwngen, Germany 3/2016-5/2016 Visiting Professor, Inst. for Applied Research Indian Institute of Science, Bangalore, India 1/2016-3/2016 Visiting Professor, Center for Nano Sc. & Eng. IIT Bombay, Mumbai, India 1/2009-5/2009 Visiting Professor, -

Sarnoff Europe Expands ESD Services with Low Threshold Consulting and TLP/HBM Testing

For media information contact: Henk De Blaere +32-59-275.915 [email protected] Sarnoff Europe Expands ESD Services With Low Threshold Consulting And TLP/HBM Testing GISTEL, BELGIUM (December 3, 2008) – Sarnoff Europe (www.sarnoffeurope.com) today announced complementary low threshold consulting and testing services to its TakeCharge® silicon IP-based Electrostatic Discharge (ESD) portfolio licensing. The new consulting service leverages Sarnoff Europe’s experience in providing silicon and product proven ESD solutions over 8 consecutive CMOS generations (0.5um down to 40nm) in multiple foundries. A team of 14 engineers uses advanced, proprietary tools to achieve quick turnaround for customer ESD risk assessment, design and layout review, debugging, ESD rules and guidelines, GDSII cells, IO/IC integration, calculation, and optimization. Sarnoff Europe and client engineers work closely together throughout the design cycle to ensure successful ESD protection of the product under study. The resulting full chip solution typically consists of a combination of public- and customer’s in-house developed solutions and foundry supplied guidelines, complemented upon necessity by Sarnoff proprietary ESD solutions. “A so comprehensive and detailed work-through of the ESD strategy and actual physical ESD triggering mechanisms has surpassed our expectations. Sarnoff’s ESD support has helped increase our confidence to exceed our customer’s specialized requirements,” said Erik Fossum Færevaag, Analog Manager, Energy Micro AS of Norway. Sarnoff Europe’s ESD testing service provides both standard and customized ESD measurements. Expert testing engineers use Sarnoff Europe’s state of the art, in-house ESD test laboratory which includes a DC parametric analyzer, TLP, HBM and MM test equipment as well as VF-TLP and customized pulse setups. -

Spring 2009 1 College News

Virtuoso Dr. Arthur C. Brooks ‘94 INSIDE: ̈ Alumni Profile: Col. Dennis Devery: Prepared To Lead ̈ NJ State Nurses Honor College President ̈ Honor Roll of Donors 2008 2 6 Honor ROLL of Donors 4 10 ContenStPs RING 2009 1 Message from the President College News: 2 ̈ Dr. Pruitt Earns New Jersey State Nurses Association President’s Award ̈ College and UPS Honored Invention is published by 3 ̈ College Dean Named to Foundation for Child Development Board Thomas Edison State College ̈ Business Dean Earns 2009 Emerald Award DR. GEORGE A. PRUITT 4 Alumni Profile: President ̈ Col. Dennis Devery: Prepared To Lead JOE GUZZARDO Editor 6 Feature: ̈ Dr. Arthur C. Brooks: Virtuoso CHRIS MILLER Art Director Page 12 10 Foundation: KELLY SACCOMANNO ̈ Honor Roll of Donors 2008 LINDA SOLTIS Contributors Inside Back Cover Applause, Applause : ̈ Alumni News Cover Story: 6 Dr. Arthur C. Brooks of the American Enterprise Institute MESSAGE FROM THE PRESIDENT Dear Alumni, Students and Friends, Barbara Bush said, “Giving frees us from the familiar territory of our own needs by opening our mind to the unexplained worlds occupied by the needs of others.” This issue of Invention is dedicated to the people and organizations who, through their support of Thomas Edison State College, illustrate what the former first lady is talking about. We are very fortunate to receive the financial support of many individuals, businesses, corporations and employees of the College, especially in today’s challenging economic climate. The annual support we receive helps the College continue to increase enrollment, expand educational programs and maintain our commitment to academic excellence. -

The 2004 Wharton MBA Career Report

51381 12/10/04 10:15 AM Page 2 The 2004 MBA Career Report careers 51381 12/10/04 10:15 AM Page 3 Who recruits Wharton MBAs? “When it comes to making the most of the intern experience, Wharton students arrive with professionalism, knowledge, and preparation that significantly advantages them over students from other schools. They come in with an attitude and work ethic that reflects their understanding of the unique opportunity before them. They have done the homework about our company and industry that positions them to add value instantly. From my perspective as both a professional and a manager, Wharton works.” Al Meyers, Vice President of Strategic Planning, TBS, Inc. IN THIS REPORT page Administration How to Hire at Wharton 2 Peter J. Degnan Director Offer Sources 2 Jennifer Savoie Head of Administration Class of 2004 C. Lyndon Brown Front Desk/Job Board Profile 4 Industry & Function Choices 5 Alice Branch Budget/Finance Compensation 6 Tiya McIver On-Campus Recruiting Location Choices 7 Class of 2005 Profile 8 Area of Expertise Associate Director Recruiting Relationship Manager Industry & Function Choices 9 Alumni Ursula Maul Varies based on industry Compensation 10 Consulting Michelle Antonio Heather Perkins Location Choices 11 Consumer Products & Retail Christopher Morris Victoria Abadir Top Hirers 12 Energy Chris HigginsHeather Perkins Employers 2004 14 Health Care/Pharma/Biotech Elissa Harris Victoria Abadir CONTACTS Insurance Sara Simons Jennifer Tarcelli Wharton MBA Career Management International Ursula Maul Varies based on industry -

TOWNSHIP of WEST WINDSOR, in the County of Mercer, New Jersey

OFFICIAL STATEMENT DATED SEPTEMBER 19, 2018 NEW ISSUE SERIAL BONDS Rating: S&P: “AAA” (See “RATING” herein) In the opinion of McManimon, Scotland & Baumann, LLC, Bond Counsel, assuming compliance by the Township (as defined herein) with certain tax covenants described herein, under existing law, interest on the Bonds (as defined herein) is excluded from gross income of the owners thereof for federal income tax purposes pursuant to Section 103 of the Internal Revenue Code of 1986, as amended (the “Code”), and interest on the Bonds is not an item of tax preference under Section 57 of the Code for purposes of computing alternative minimum tax; however, interest paid to certain corporate holders of the Bonds indirectly may be subject to alternative minimum tax under circumstances described under “TAX MATTERS” herein. Based upon existing law, interest on the Bonds and any gain on the sale thereof are not included in gross income under the New Jersey Gross Income Tax Act. See “TAX MATTERS” herein. TOWNSHIP OF WEST WINDSOR, In the County of Mercer, New Jersey $10,500,000 GENERAL IMPROVEMENT BONDS, SERIES 2018 (Book-Entry Issue) (Callable) Dated Date: Date of Delivery Due: October 1, as shown on the inside front cover hereof The $10,500,000 General Improvement Bonds, Series 2018 (the “Bonds”) of the Township of West Windsor, in the County of Mercer, New Jersey (the “Township”), will be issued in the form of one certificate for the principal amount of the Bonds maturing in each year and when issued will be registered in the name of Cede & Co., as nominee of The Depository Trust Company, New York, New York (“DTC”), which will act as the “securities depository”. -

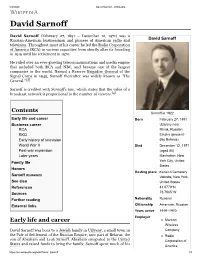

David Sarnoff - Wikipedia

4/3/2020 David Sarnoff - Wikipedia David Sarnoff David Sarnoff (February 27, 1891 – December 12, 1971) was a Russian-American businessman and pioneer of American radio and David Sarnoff television. Throughout most of his career he led the Radio Corporation of America (RCA) in various capacities from shortly after its founding in 1919 until his retirement in 1970. He ruled over an ever-growing telecommunications and media empire that included both RCA and NBC, and became one of the largest companies in the world. Named a Reserve Brigadier General of the Signal Corps in 1945, Sarnoff thereafter was widely known as "The General."[3] Sarnoff is credited with Sarnoff's law, which states that the value of a broadcast network is proportional to the number of viewers.[4] Contents Sarnoff in 1922 Early life and career Born February 27, 1891 Business career Uzlyany near RCA Minsk, Russian RKO Empire (present- Early history of television day Belarus) World War II Died December 12, 1971 Post-war expansion (aged 80) Later years Manhattan, New Family life York City, United States Honors Resting place Kensico Cemetery Sarnoff museum Valhalla, New York, See also United States References 41.0779°N Sources 73.7865°W Further reading Nationality Russian External links Citizenship American, Russian Years active 1919–1970 Employer Early life and career Marconi Wireless David Sarnoff was born to a Jewish family in Uzlyany, a small town in Company the Pale of Settlement of the Russian Empire, now part of Belarus, the Radio son of Abraham and Leah Sarnoff. Abraham emigrated to the United Corporation of States and raised funds to bring the family. -

Con Edison, Sarnoff Engineers Earn Global Honor for GPS-Based System to Bring Substation on Line

Con Edison, Sarnoff Engineers Earn Global Honor For GPS-Based System to Bring Substation On Line August 11, 2003 Named to '50 Key IT Players in Energy' Annual Honors List; Invention Solved Problem of Rebuilding Electric Infrastructure After 9/11 Attack NEW YORK and PRINCETON, N.J., Aug. 11 /PRNewswire-FirstCall/ -- Paul V. Stergiou, a senior engineer at Consolidated Edison of New York, and David Kalokitis, a member of the technical staff at Sarnoff Corporation, have been named to the list of "50 Key Information Technology Players in Energy," a global honors program run by RaderEnergy, a Houston-based consultancy. The list, published in the June issue of Commodities Now magazine, recognizes outstanding IT achievements in the energy industry during 2002. Stergiou and Kalokitis were honored for leading the development of system that allowed Con Edison to bring a new power substation on line in just four hours instead of the normal 72 hours. The system was first used last March in the replacement of a substation destroyed in the terrorist attack on New York's World Trade Center on September 11, 2001. It uses GPS (global positioning satellite) technology to match the power sine-wave phasing of the substation with that of the electrical grid. "This system applies space-age digital technology to Edison-era infrastructure," said Stergiou. "It speeds up the intermeshing of a new substation with the grid, which is crucial when you're trying to recover from disasters. "It's also a digital solution to a digital problem. Much of the telecommunications industry has replaced its analog lines with all-digital circuits. -

Augmented Outdoor Scene

Augmented Reality and its application to maintaining and repairing vehicles. Rakesh (Teddy) Kumar Vision and Robotics Laboratory SRI International Sarnoff Email: [email protected] Phone: 1-609-734-2832 April 12th, 2011 © 2011 SRI International ‐ Company Proprietary Information Talk Overview 1. Introduction to SRI 2. Augmented Reality for Military Defense Training 3. Other Applications of Augmented Reality 4. Augmented Reality for Vehicle Repair and Maintenance 5. Conclusions Who We Are SRI is a world‐leading R&D organization • An independent, nonprofit corporation – Founded by Stanford University in 1946 – Independent in 1970; changed name from Stanford Research Institute to SRI International in 1977 – Sarnoff Corporation acquired as a subsidiary in 1987; integrated into SRI in 2011 • 2,100 staff members Silicon Valley ‐ Headquarters • More than 20 locations worldwide • 2009 revenues: approximately $470 million Washington, D.C. Tokyo, Japan VirginiaPennsylvania Florida New Jersey OPPORTUNITIES PROFILE INNOVATIONS CAPABILITIES PARTNERSHIPS Our Focus Areas MltidiiliMultidisciplinary teams leverage core thtechno logy and research areas Information Technology Health, Education, Engineering and and Economic Policy Systems SRI’s Value Creation Process™ Biotechnology Advanced Materials, Microsystems, and Nanotechnology OPPORTUNITIES PROFILE INNOVATIONS CAPABILITIES PARTNERSHIPS Clients throughout the World Providing value to our clients worldwide Mission: SRI is committed to discovery and to the application of science and technology for knowledgg,e, -

Misra March 2017

Resume of Dr. D. Misra March 2017 Durgamadhab (Durga) Misra Department of Electrical and Computer Engineering, New Jersey Institute of Technology, University Heights Newark, NJ 07102, Email: [email protected] Phone: (973) 596-5739 Fax: (973) 596-5680 Fellow of the Electrochemical Society Education Ph.D., Electrical Engineering, University of Waterloo, Waterloo, Canada, 1988 M.S., Management, New Jersey Institute of Technology, 1997 M.A.Sc., Electrical Engineering, University of Waterloo, Waterloo, Canada, 1985 M.Tech., Solid-State, IIT Delhi, India, 1983 M.S., Physics, Utkal University, Bhubaneswar, India, 1981 B.S., Physics, Utkal University, Bhubaneswar, India, 1978 Academic Experience New Jersey Institute of Technology, 2011- Associate Chair for Graduate Studies, ECE Dept Newark, NJ 2006 – 2008 Associate Chair for Graduate Studies, ECE Dept 2002 - Professor, Electrical & Computer Eng. Dept. 2002 – Director, Graduate Program: MS Electrical Eng 1993 - 2002 Associate Professor, Elect & Comp Eng Dept 1996 - 1997 Director, Microelectronics Research Center, 1988 - 1993 Assistant Professor, Elect & Comp Eng Dept Indian Institute of Science, Bangalore, India 2017 Prof. Ramakrishna Rao Visiting Chair Position at Center for Nano Science and Engineering (CeNSE) Furtwangen University, Furtwngen, Germany 3/2016-5/2016 Visiting Professor, Inst. for Applied Research Indian Institute of Science, Bangalore, India 1/2016-3/2016 Visiting Professor, Center for Nano Sc. & Eng. IIT Bombay, Mumbai, India 1/2009-5/2009 Visiting Professor, Electrical Engineering -

Evaluated from Two Perspectives: the Appearance of the Project from the Surrounding Areas, and the Appearance of the Surrounding Areas from the Project (FHWA, 1988)

Environmental Consequences and Mitigation Chapter 4 Environmental Consequences and Mitigation Chapter 4 4.12 Aesthetics The Federal Highway Administration guidelines specify that impacts to visual resources be evaluated from two perspectives: the appearance of the project from the surrounding areas, and the appearance of the surrounding areas from the project (FHWA, 1988). Viewers from the surrounding areas include residents of the Penns Neck and Lower Harrison Street neighborhoods, customers and employees of the businesses in the area. Other viewers might be users of the Princeton recreation fields and pedestrians along Washington Road or users of the D&R Canal Park. Viewers of the surrounding area from the project include drivers along Route 1, Washington Road, Harrison Street and new roadways contemplated under the Action Alternatives. These drivers would be comprised of local users, including residents of area neighborhoods and customers of area businesses and regional users, including commuters along Route that work in or outside of the study area. Potential visual impacts could include encroachment of new roadways on existing viewsheds, visual compatibility of a new roadway design with the surroundings, and views created by construction of a new roadway, both from the roadway and of the roadway. 4.12.1 No-Action Alternative, Aesthetics The No-Action Alternative would preserve existing roadways and travel patterns, and would involve no new construction. The only potential visual impact would be increased traffic on existing roadways. The No-Action Alternative is expected to increase peak period congestion and queues on Washington Road, Harrison Street, and Alexander Road which would have an added visual impact on the D&R Canal Park and elm allee compared to existing conditions.