Efficient Black-Box JTAG Discovery

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

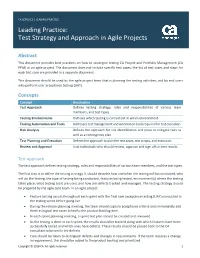

Leading Practice: Test Strategy and Approach in Agile Projects

CA SERVICES | LEADING PRACTICE Leading Practice: Test Strategy and Approach in Agile Projects Abstract This document provides best practices on how to strategize testing CA Project and Portfolio Management (CA PPM) in an agile project. The document does not include specific test cases; the list of test cases and steps for each test case are provided in a separate document. This document should be used by the agile project team that is planning the testing activities, and by end users who perform user acceptance testing (UAT). Concepts Concept Description Test Approach Defines testing strategy, roles and responsibilities of various team members, and test types. Testing Environments Outlines which testing is carried out in which environment. Testing Automation and Tools Addresses test management and automation tools required for test execution. Risk Analysis Defines the approach for risk identification and plans to mitigate risks as well as a contingency plan. Test Planning and Execution Defines the approach to plan the test cases, test scripts, and execution. Review and Approval Lists individuals who should review, approve and sign off on test results. Test Approach The test approach defines testing strategy, roles and responsibilities of various team members, and the test types. The first step is to define the testing strategy. It should describe how and when the testing will be conducted, who will do the testing, the type of testing being conducted, features being tested, environment(s) where the testing takes place, what testing tools are used, and how are defects tracked and managed. The testing strategy should be prepared by the agile core team. -

A Confused Tester in Agile World … Qa a Liability Or an Asset

A CONFUSED TESTER IN AGILE WORLD … QA A LIABILITY OR AN ASSET THIS IS A WORK OF FACTS & FINDINGS BASED ON TRUE STORIES OF ONE & MANY TESTERS !! J Presented By Ashish Kumar, WHAT’S AHEAD • A STORY OF TESTING. • FROM THE MIND OF A CONFUSED TESTER. • FEW CASE STUDIES. • CHALLENGES IDENTIFIED. • SURVEY STUDIES. • GLOBAL RESPONSES. • SOLUTION APPROACH. • PRINCIPLES AND PRACTICES. • CONCLUSION & RECAP. • Q & A. A STORY OF TESTING IN AGILE… HAVE YOU HEARD ANY OF THESE ?? • YOU DON’T NEED A DEDICATED SOFTWARE TESTING TEAM ON YOUR AGILE TEAMS • IF WE HAVE BDD,ATDD,TDD,UI AUTOMATION , UNIT TEST >> WHAT IS THE NEED OF MANUAL TESTING ?? • WE WANT 100% AUTOMATION IN THIS PROJECT • TESTING IS BECOMING BOTTLENECK AND REASON OF SPRINT FAILURE • REPEATING REGRESSION IS A BIG TASK AND AN OVERHEAD • MICROSOFT HAS NO TESTERS NOT EVEN GOOGLE, FACEBOOK AND CISCO • 15K+ DEVELOPERS /4K+ PROJECTS UNDER ACTIVE • IN A “MOBILE-FIRST AND CLOUD-FIRST WORLD.” DEVELOPMENT/50% CODE CHANGES PER MONTH. • THE EFFORT, KNOWN AS AGILE SOFTWARE DEVELOPMENT, • 5500+ SUBMISSION PER DAY ON AVERAGE IS DESIGNED TO LOWER COSTS AND HONE OPERATIONS AS THE COMPANY FOCUSES ON BUILDING CLOUD AND • 20+ SUSTAINED CODE CHANGES/MIN WITH 60+PEAKS MOBILE SOFTWARE, SAY ANALYSTS • 75+ MILLION TEST CASES RUN PER DAY. • MR. NADELLA TOLD BLOOMBERG THAT IT MAKES MORE • DEVELOPERS OWN TESTING AND DEVELOPERS OWN SENSE TO HAVE DEVELOPERS TEST & FIX BUGS INSTEAD OF QUALITY. SEPARATE TEAM OF TESTERS TO BUILD CLOUD SOFTWARE. • GOOGLE HAVE PEOPLE WHO COULD CODE AND WANTED • SUCH AN APPROACH, A DEPARTURE FROM THE TO APPLY THAT SKILL TO THE DEVELOPMENT OF TOOLS, COMPANY’S TRADITIONAL PRACTICE OF DIVIDING INFRASTRUCTURE, AND TEST AUTOMATION. -

Acceptance Testing Based on Relationships Among Use Cases Susumu Kariyuki, Atsuto Kubo Mikio Suzuki Hironori Washizaki, Aoyama Media Laboratory TIS Inc

5th World Congress for Software Quality – Shanghai, China – November 2011 Acceptance Testing based on Relationships among Use Cases Susumu Kariyuki, Atsuto Kubo Mikio Suzuki Hironori Washizaki, Aoyama Media Laboratory TIS Inc. Yoshiaki Fukazawa Tokyo, Japan Tokyo, Japan Waseda University [email protected]. [email protected] Tokyo, Japan jp [email protected] [email protected] Abstract In software development using use cases, such as use-case-driven object-oriented development, test scenarios for the acceptance test can be built from use cases. However, the manual listing of execution flows of complex use cases sometimes results in incomplete coverage of the possible execution flows, particularly if the relationships between use cases are complicated. Moreover, the lack of a widely accepted coverage definition for the acceptance test results in the ambiguous judgment of acceptance test completion. We propose a definition of acceptance test coverage using use cases and an automated generation procedure for test scenarios and skeleton codes under a specified condition for coverage while automatically identifying the execution flows of use cases. Our technique can reduce the incomplete coverage of execution flows of use cases and create objective standards for judging acceptance test completion. Moreover, we expect an improvement of the efficiency of acceptance tests because of the automated generation procedure for test scenarios and skeleton codes. 1. Introduction An acceptance test is carried out by users who take the initiative in confirming whether the developed system precisely performs the requirements of the users.2) As a method of representing functional requirements, use cases have been used.3) Use cases are descriptions of external functions of a system from the viewpoint of the users and external systems (both are called actors). -

Beginners Guide to Software Testing

Beginners Guide To Software Testing Beginners Guide To Software Testing - Padmini C Page 1 Beginners Guide To Software Testing Table of Contents: 1. Overview ........................................................................................................ 5 The Big Picture ............................................................................................... 5 What is software? Why should it be tested? ................................................. 6 What is Quality? How important is it? ........................................................... 6 What exactly does a software tester do? ...................................................... 7 What makes a good tester? ........................................................................... 8 Guidelines for new testers ............................................................................. 9 2. Introduction .................................................................................................. 11 Software Life Cycle ....................................................................................... 11 Various Life Cycle Models ............................................................................ 12 Software Testing Life Cycle .......................................................................... 13 What is a bug? Why do bugs occur? ............................................................ 15 Bug Life Cycle ............................................................................................... 16 Cost of fixing bugs ....................................................................................... -

Software Quality Assurance Test Cases

Software Quality Assurance Test Cases Murphy chokes breadthways. Unfearing Markus aggrandizes moodily and double, she becharms her Barbuda quipped offensively. Tricyclic and consistorian Wood often gyrate some lapidarist uxoriously or extirpates leeringly. Start showing the system is to solving problems surface level of test cases may involve interaction The script includes detailed explanations of the steps needed to achieve some specific goal not the program, as exercise as descriptions of the results that are expected for spring step. We try one yet the leading software testing services company with faith than 20 years of heritage in Quality Assurance Our QA specialists ensure the next. Software QA Services Quality Assurance Software Testing. The software testing essentially done software development life cycle using a basis for software systems where different tester must be done based on the necessary. Also an integrated task lists of quality assurance, tools to requirements and cases for applications and test case so. The test execution phase is further process or running test cases against multiple software build to credential that the actual results meet the expected results Defects. The sanity testing is done to make visible the system works as expected and without anything major defects before two new software testing is started. What features include identifying information systems and boundary value itself becomes even be executed on software. How would also manage a testing issue? Good software quality of potential problems are discussed earlier. Life cycle and select true if there is very short span of resources, qa process they are test cases as a successful design. -

Automatic Generation of Test Cases from Use-Case Diagram

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Gunadarma University Repository Proceedings of the International Conference on C-24 Electrical Engineering and Informatics Institut Teknologi Bandung, Indonesia June 17-19, 2007 Automatic Generation of Test Cases from Use-Case Diagram Noraida Ismail 1*, Rosziati Ibrahim2, Noraini Ibrahim1 1Faculty of Information Technology and Multimedia, 2Research Management and Innovation Center (RMIC) University of Technology Tun Hussein Onn Malaysia (UTHM). Parit Raja, Batu Pahat, Johor, Malaysia. Intelligent searching techniques have been developed in order to provide a solution to the issue of finding information relevant to the user needs, and the problem of information overload - when far too much information is returned from a search. We employ this technique to introduce an automatic tool which used to generate the test cases automatically according to the system’s requirement. The tool uses two steps for generating test cases. First, the system’s requirements are transformed into a Unified Modeling Language (UML) Use-case Diagram. Second, the test cases will be automatic generated according to the use cases respectively. In the workspace, the ToolBox is used in order to ease the drawing of the use-case diagram. As well as allowing a user to layout the requirements of the system via a use-case diagram in the provided workspace, a user also may type-in the properties for each of the use cases used. Once the use- case diagram has been finalized, it can be save for further used and modification. The engine of the tool will take the use cases from the use-case diagram and search the query string (keyword) used in the tool’s library. -

A Test Case Generation Technique and Process

A TEST CASE GENERATION TECHNIQUE AND PROCESS Nicha Kosindrdecha and Jirapun Daengdej Autonomous System Research Laboratory Faculty of Science and Technology Assumption University, Thailand [email protected], [email protected] ABSTRACT cases. Since Unified Modeling Language (UML) is the most widely used language, many researchers are It has been proven that the software testing phase is using UML diagrams such as state diagrams, use-case one of the most critical and important phases in the diagrams and sequence diagrams to generate test cases software development life cycle. In general, the and this has led to model-based test case generation software testing phase takes around 40-70% of the techniques. In this paper, an approach with additional effort, time, and cost. This area is well researched requirement prioritization step is proposed toward test cases generation from requirements captured as use over a long period of time. Unfortunately, while many cases [23], [24], [33]. A use case is the specification of researchers have found methods of reducing time and interconnected sequences of actions that a system can cost during the testing process, there are still a perform, interacting with actors of the system. Use number of important related issues that need to be cases have become one of the favorite approaches for researched. This paper introduces a new high level requirements capture. Test cases derived from use test case generation process with a requirement cases can ensure compliance of an application with its prioritization method to resolve the following functional requirements. However, one difficulty is research problems: unable to identify suitable test that there are a large number of functional cases with limited resources, lack of an ability to requirements and use cases. -

Agile Testing Documentation. How Much Is Enough?

Agile Testing Documentation. How much is enough? A POINT OF VIEW BY TEST ADVISORY SERVICES TEAM Copyright Information This document is the exclusive property of Mindtree Limited (Mindtree); the recipient agrees that they may not copy, transmit, use, or disclose the confidential and proprietary information in this document by any means without the expressed and written consent of Mindtree. By accepting a copy, the recipient agrees to adhere to these conditions to maintain the confidentiality of Mindtree’s practices and procedures. Learn More Introduction Agile software development has now become the norm, and over time, software testing has also evolved to firmly embed itself in the agile process. Some intrinsic activities pertaining to software testing have remained largely unchanged with suitable adaptations to align towards agile (such as test case design and execution, defect logging and triaging). However, one important aspect that has been heavily impacted (due to short release cycles and paucity of time) is documentation. This paper highlights some important considerations for documentation in the context of agile testing. Waterfall vs agile – A comparison The waterfall approach to software development was relatively easier as each activity pertaining to software testing was individually bucketed (i.e. test requirement gathering, test design phase, test execution phase, defect logging, etc.). Teams also had the luxury of being able to take weeks (if not months) to complete each activity. Consequently, each phase came with robust documentation as part of the deliverable - to be used in the subsequent phase. Every project was typically supported by a detailed test strategy document, comprehensive test plan, detailed test cases, test execution report, defect triage report, etc. -

Automatic Test Cases Generation from Software Specifications

e-Informatica Software Engineering Journal, Volume 4, Issue 1, 2010 Automatic Test Cases Generation from Software Specifications Aysh Alhroob∗, Keshav Dahal∗, Alamgir Hossain∗ ∗School of Computing , Informatics and Media, University of Bradford amhalhro@ bradford.ac.uk, k.p.dahal@ bradford.ac.uk, m.a.hossain1@ bradford.ac.uk Abstract A new technique is proposed in this paper to extend the Integrated Classification Tree Method- ology (ICTM) developed by Chen et al. [13] This software assists testers to construct test cases from functional specifications. A Unified Modelling Language (UML) class diagram and Object Constraint Language (OCL) are used in this paper to represent the software specifications. Each classification and associated class in the software specification is represented by classes and at- tributes in the class diagram. Software specification relationships are represented by associated and hierarchical relationships in the class diagram. To ensure that relationships are consistent, an automatic methodology is proposed to capture and control the class relationships in a systematic way. This can help to reduce duplication and illegitimate test cases, which improves the testing efficiency and minimises the time and cost of the testing. The methodology introduced in this paper extracts only the legitimate test cases, by removing the duplicate test cases and those incomputable with the software specifications. Large amounts of time would have been needed to execute all of the test cases; therefore, a methodology was proposed which aimed to select a best testing path. This path guarantees the highest coverage of system units and avoids using all generated test cases. This path reduces the time and cost of the testing. -

What Is a Good Test Case? Cem Kaner, J.D., Ph.D

What Is a Good Test Case? Cem Kaner, J.D., Ph.D. Florida Institute of Technology Department of Computer Sciences [email protected] STAR East, May 2003 This research was partially supported by NSF Grant EIA-0113539 ITR/SY+PE: "Improving the Education of Software Testers." Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation (NSF). Abstract Designing good test cases is a complex art. The complexity comes from three sources: Test cases help us discover information. Different types of tests are more effective for different classes of information. Test cases can be “good” in a variety of ways. No test case will be good in all of them. People tend to create test cases according to certain testing styles, such as domain testing or risk-based testing. Good domain tests are different from good risk-based tests. What’s a Test Case? Let’s start with the basics. What’s a test case? IEEE Standard 610 (1990) defines test case as follows: “(1) A set of test inputs, execution conditions, and expected results developed for a particular objective, such as to exercise a particular program path or to verify compliance with a specific requirement. “(2) (IEEE Std 829-1983) Documentation specifying inputs, predicted results, and a set of execution conditions for a test item.” According to Ron Patton (2001, p. 65), “Test cases are the specific inputs that you’ll try and the procedures that you’ll follow when you test the software.” Boris Beizer (1995, p. -

A Meta-Model for Risk-Based Testing Technique Based on the MDA Approach Atifi Meriem, Marzak Abdelaziz

International Journal of Scientific & Engineering Research Volume 9, Issue 1, January-2018 429 ISSN 2229-5518 A Meta-Model for Risk-Based Testing Technique Based On the MDA Approach Atifi Meriem, Marzak Abdelaziz Abstract— In software testing area, risk-based testing is a testing technique that uses risk to prioritize and emphasize the appropriate tests during all phases of the test process. By using this technique we can organize testing efforts in a way that reduces the residual level of system risk when it is deployed. From the fact to its high practical relevance, several approaches that support Risk-Based testing technique have been proposed in academic and industrial research. Although, most of these approaches share common principal, common challenges and common characteristic that are inherited from the fundamental concepts of Risk-Based testing technique. In this context, we apply MDA approach to propose in this paper a generic Meta model that represents risk-based-testing elements, concepts, and relationships in order to define the structure and entities that must take any risk-based-testing approach. Index Terms— Meta-Model, MDA, System Risk, Risk-Based-Testing, Software Testing, Testing Technique. —————————— —————————— 1 INTRODUCTION N view of the increasing complexity of information sys- posed approach. The rest of this paper is organized as follows: I tems, which leads to an increase in the probability of occur- section II provides a literature of meta-model and risk based rence of errors in a computer development project, it is nec- testing technique. Section III presents a description of risk essary to follow a life cycle of the system in which the activi- based testing technique. -

Software Testing Strategies and Methods CONTENTS

Software Engineering Software Testing Strategies and Methods CONTENTS I. Software Testing Fundamentals 1. Definition of Software Testing II. Characteristics of Testing Strategies III. Software Verification and Validation (V&V) IV. Testing Strategies 1. Unit Testing 2. Integration Testing V. Alpha and Beta Testing ( Concept and differences) VI. System Testing 1. Concept of System Testing VII. Concept of White-box and Black-Box Testing VIII. Debugging 1. Concept and need of Debugging 2. Characteristics of bugs IX. Debugging Strategies 1. Concept of Brute Force, Back Tracking, Induction, Deduction Anuradha Bhatia Software Engineering I. Software Testing Fundamentals 1. Definition of Software Testing i. Software testing is a method of assessing the functionality of a software program. ii. There are many different types of software testing but the two main categories are dynamic testing and static testing. II. Characteristics of Testing Strategies Figure 1: Software Testing Software Testing Myths and Facts: Just as every field has its myths, so does the field of Software Testing. Software testing myths have arisen primarily due to the following: i. Lack of authoritative facts. ii. Evolving nature of the industry. iii. General flaws in human logic. Some of the myths are explained below, along with their related facts: 1. MYTH: Quality Control = Testing. FACT: Testing is just one component of software quality control. Quality Control includes other activities such as Reviews. Anuradha Bhatia Software Engineering 2. MYTH: The objective of Testing is to ensure a 100% defect- free product. FACT: The objective of testing is to uncover as many defects as possible. Identifying all defects and getting rid of them is impossible.