Macintosh Quadra 700 Developer Note

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Holiday Catalog

Brilliant for what’s next. With the power to achieve anything. AirPods Pro AppleCare+ Protection Plan†* $29 Key Features • Active Noise Cancellation for immersive sound • Transparency mode for hearing and connecting with the world around you • Three sizes of soft, tapered silicone tips for a customizable fit • Sweat and water resistant1 • Adaptive EQ automatically tunes music to the shape of your ear • Easy setup for all your Apple devices2 • Quick access to Siri by saying “Hey Siri”3 • The Wireless Charging Case delivers more than 24 hours of battery life4 AirPods Pro. Magic amplified. Noise nullified. Active Noise Cancellation for immersive sound. Transparency mode for hearing what’s happening around you. Sweat and water resistant.1 And a more customizable fit for all-day comfort. AirPods® AirPods AirPods Pro with Charging Case with Wireless Charging Case with Wireless Charging Case $159 $199 $249 1 AirPods Pro are sweat and water resistant for non-water sports and exercise and are IPX4 rated. Sweat and water resistance are not permanent conditions. The charging case is not sweat or water resistant. 2 Requires an iCloud account and macOS 10.14.4, iOS 12.2, iPadOS, watchOS 5.2, or tvOS 13.2 or later. 3Siri may not be available in all languages or in all areas, and features may vary by area. 4 Battery life varies by use and configuration. See apple.com/batteries for details. Our business is part of a select group of independent Apple® Resellers and Service Providers who have a strong commitment to Apple’s Mac® and iOS platforms and have met or exceeded Apple’s highest training and sales certifications. -

Power Macintosh 6100/ WS 6150

K Service Source Power Macintosh 6100/ WS 6150 Power Macintosh 6100/60, 6100/60AV, 6100/66, 6100/66AV, 6100/DOS Compatible, and Workgroup Server 6150 K Service Source Basics Power Macintosh 6100/WS 6150 Basics Power Macintosh System Overview - 1 Power Macintosh System Overview PowerPC microprocessors are a family of processors built on reduced instruction-set computing (RISC) technology. RISC processors streamline the internal workings of computers. Whereas traditional (complex instruction-set computing, or CISC) processors contain a wide variety of instructions to handle many different tasks, RISC processors contain only those instructions that are used most often. When a complex instruction is needed, a RISC processor builds it from a combination of basic instructions. RISC processors are designed to execute these basic instructions extremely quickly. The performance gains achieved by speeding up the most-used instructions more than compensate for the time spent creating less-used instructions. Basics Power Macintosh System Overview - 2 Previously, RISC technology had been used only in high-end workstations and commercial database servers. With the introduction of Macintosh PowerPC computers, Apple succeeded in bringing RISC technology to personal computing. Key Points Three key points to remember about a PowerPC processor- based Macintosh system: It's a Macintosh; it's compatible; it offers tremendous performance. Apple's PowerPC computers feature the same user interface as their 680x0-based predecessors. Users can mix RISC- based and 680x0-based Macintosh systems on the same net- work and exchange files and disks between them. In addition, users can run both 680x0 and native PowerPC applications on the same Power Macintosh system simultaneously. -

The Apple Effect

The Apple Effect 5 Apple Revolutions: Personal Computing Publishing Imaging Video Audio The world changed when it became possible for Once upon a time, electronics enthusiasts to assemble components to computers were make their own personal computer. Altair was the first to market components together in kit form, complex, rare and but two guys named Steve Jobs and Steve Wozniak, operating from a garage in California, were not far expensive machines behind with a kit that is now known as the Apple I. that companies – even About 200 were produced, but that convinced the two Steves to found Apple Computer Inc countries – struggled to and work on a computer that did not require electronics knowledge to assemble and use. It afford to build, buy or was the release of this model in 1977, the Apple ][, use. which heralded the widespread leap of electronics from the mainframe to personal computing. Suddenly business, home and schools had access Two guys in a garage precipitated a shift in our to computing power previously available only with universe to one where computers are simple to use, mainframes. yet more powerful than many dreamed possible. The evolution of software The company they started, Apple Computer Inc, Early mainframe computers had to be programmed has consistently led the way in personal computing by methods which amounted to rewiring the innovations and in developing many of the tools circuits. Personal computers made the jump and technologies we take for granted. to programming languages—even the Apple I The Apple Effect is a story of five revolutions in included Apple Basic—which evolved into ‘software’ computing history. -

Circuit-Cellar-017.Pdf

EDITOR’S INK CASE is Coming Curtis Franklin, Jr. I t’s fun to watch events come together to form a trend. A and the programmer’s “quality of life” improved. Finally, there while back, I told you that events were coming together that came the trend that would tie everything together. would result in a trend toward using “PC-compatible” platforms Intel pushed to merge desktop microcomputer and embed- for control applications in ever-increasing numbers. Things are ded controllerarchitectureswiththe80186. Here wasa micropro- still rolling along with that trend, and I feel pretty good about the cessor that was code-compatible with the popular 8088 and 80% prediction. I feel so good, in fact, that I’m going to hit you with microprocessors, yet had I/O features more typical of embedded another prediction this time: I predict that most of the people controllers. Through time, the price of IBM PC/XT-clone moth- reading this will be using CASEKomputer-Aided Software erboards dropped to a point where the same I/O, operating Engineering-within the next five years. It doesn’t matter whether system, and memory architectures could be economically used most of your programming time is spent on desktop computer for both desktop computing and control applications. Engineers applications or embedded control, I believe you will start using and control programmers have been introduced to the wonders CASE tools. I’m making this prediction based, not on any sort of of the modern desktop development environment, and the steps blazing insight, but on the logical progression of several industry are short between (for example) the Borland Turbo-language trends. -

Apple Multiple Scan 15 Display

K Service Source Apple Multiple Scan 15 Display K Service Source Basics Apple Multiple Scan 15 Display Basics Overview - 1 Overview The Apple Multiple Scan 15 Display is a color monitor that supports a variety of resolutions, and has a flat, square screen for clear, sharp images. The Apple Multiple Scan 15 Display has a diagonal viewable image size of 13.3 inches. Basics Overview - 2 The Apple Multiple Scan 15 Display features • Optimized screen resolutions (640x480, 800x600, 832x624) • A tilt-swivel base that allows the monitor to be positioned for optimal viewing comfort • MPR II compliance for low electrical and magnetic emissions • Energy Star power conservation compliance K Service Source Specifications Apple Multiple Scan 15 Display Specifications Characteristics - 1 Characteristics Picture Tube 15-in. diagonal flat square shadow mask (13.3-in. viewable image) Multiple scan Polished surface treatment Screen Resolution 640x480, 800x600, or 832x624 1024x768 (only PC and PC-compatibles with a Mac/PC adapter) 0.28-mm dot pitch Scan Rates Vertical refresh rate: 60–75 Hz Horizontal scan rate: 31.77–56.5 kHz Macintosh, VGA, and SVGA compatible Specifications Characteristics - 2 Cable Connector 15-pin miniature D-type Input Signals Video: red, green, and blue analog signals; RS-343A standard; .714 V peak to peak; positive-going Sync on green: RS-343A compatible level; .286 V ± 10% negative-going during blanking intervals Separate Sync: 1 to 5 V peak to peak; negative- or positive-going Composite Sync: 1 to 5 V peak to peak; negative- or positive-going Specifications Characteristics - 3 System Power Macintosh, Macintosh Centris, Macintosh Quadra, some Requirements Macintosh Performas, or any NuBus compatible Macintosh with a Macintosh Display Card 24AC. -

From 128K to Quadra: Model by Model

Chapter 12 From 128K to Quadra: Model by Model IN THIS CHAPTER: I What the specs mean I The specs for every Mac model ever made I Secrets of the pre-PowerPC Mac models I Just how much your Mac has devalued Yes, we’ve already been told that we’re nuts to attempt the next two chapters of this book. Since 1984, Apple has created more than 140 different Mac models — including 35 different PowerBooks and 53 different Performas! Each year, Apple piles on another dozen or so new models. By the time you finish reading this page, another Performa model probably will have been born. So, writing a couple of chapters that are supposed to describe every model is an exercise in futility. But we’re going to attempt it anyway, taking the models one by one and tracking their speeds, specs, and life cycles. This chapter will cover all the Apple Macs — both desktop and portable models — from the birth of the original Macintosh 128K to the release of the PowerBook 190, the last Mac ever made that was based on Motorola’s 68000-series processor chip. When you’re finished reading this chapter, you will be one of the few people on Earth who actually knows the difference between a Performa 550, 560, 575, 577, 578, 580, and 588. 375 376 Part II: Secrets of the Machine Chapter 13 will cover every Power Mac — or, more accurately, every PowerPC-based machine (those with four-digit model numbers) — from the first ones released in 1994 to the models released just minutes before this book was printed. -

Macintosh Quadra 800/WS 80

K Service Source Macintosh Quadra 800/WS 80 Macintosh Quadra 800 Workgroup Server 80 K Service Source Specifications Quadra 800/WS 80 Specifications Processor - 2 Processor CPU Motorola 68040 microprocessor 33 MHz Built-in paged memory management unit (PMMU), floating-point unit (FPU), and 8K memory cache Addressing 32-bit registers 32-bit address/data bus Specifications Memory - 3 Memory DRAM 8 MB (soldered DRAM) or 24 MB (8 MB soldered DRAM plus four 4 MB SIMMs) standard; expandable to 136 MB 72-pin SIMMs 60 ns access time ROM 1 MB soldered on logic board PRAM 256 bytes of parameter memory Specifications Memory - 4 VRAM 512K or 1 MB standard, expandable to 1 MB (80 ns or faster VRAM SIMMs) Maximum pixel depths for 512K / 1 MB VRAM: 12-inch color (512 x 384) - 16 / 16 bits per pixel 12-inch monochrome (640 x 480) - 8 / 8 bits per pixel 13-inch color (640 x 480) - 8 / 16 bits per pixel 15-inch portrait (640 x 870) - 4 / 8 bits per pixel 16-inch color (832 x 624) - 8 / 16 bits per pixel 19-inch color (1024 x 768) - 4 / 8 bits per pixel 21-inch monochrome (1152 x 870) - 4 / 8 bits per pixel 21-inch color (1152 x 870) - 4 / 8 bits per pixel VGA (640 x 480) - 8 / 16 bits per pixel SVGA (800 x 600) - 8 / 16 bits per pixel Clock/Calendar CMOS custom chip with long-life lithium battery Specifications Disk Storage - 5 Disk Storage Floppy Drive Internal, 1.4 MB Apple SuperDrive Hard Drive Internal, 3.5 in. -

8 News and Help

News and Help The plan is to collate any news in this document. I’ll then archive the content to another document so we can still access it but we only need to access the same document for all the new news. August 2020 Apple Updates, Improvements and Company News macOS Catalina 10.15.6 includes improvements to Apple News, a new option to optimise video streaming on HDR-compatible Mac notebooks for improved battery life, improvements to USB mouse and trackpad handling, and a fix for an issue that could cause the software update process to change the computer's name. 10.15.6 and the corresponding security updates for Mojave and High Sierra address a variety of serious vulnerabilities. Safari 13.1.2 is part of Catalina 10.15.6 and is also available for Mojave and High Sierra. It addresses 11 security issues, some of which can be remotely exploited to execute arbitrary code. iOS 13.6 brings the much-heralded digital car keys feature (initially for very recently made BMWs, and including key sharing via Messages and a 'power reserve' allowing keys to be used up to five hours after the phone's battery runs out). iOS 13.6 and iPadOS 13.6 include Apple News improvements (including audio news), a 'symptoms' category in the Health app, and various changes and fixes relating to software updates, iCloud Drive, Wi-Fi calling, and other features. The updates also address a total of 29 issues that could be variously exploited to execute arbitrary code, view sensitive information, and allow cross-site scripting, among others. -

October 1993 $2.95

October 1993 $2.95 The Journal of Washington Apple Pi, Ltd. Volmne 15, Number 10 Great printquality. aroatprice. LOOKING GOOD The HP DeskWriter: FOR LESS. $365. It looks like laser printing. But its :::::~:,;::.~=-~~-= priced like a dot matriX. ltcoold only --to-- 1\1 --..... """"'bOO"\I•"·'~'~· c.HQ_.._.._ ........,U•"'l· ,_,lall1<t...,,....,,._... ., """"' · • be a DeskWrllcr black and.white .,.,.,l)o __ flt'(loAjfMW'i..• ..... 'f;k.r~•o...-.(•Y•.. •• •th.uJ printer from Hewlett-Packard. · ~~ t;io~•'Ll(•.,.. ....., • .,.._ ,u,,. IW!>tnl"<>,......,,,,.'°-.. ._.. ,. .. ............ ,_ ....... tlit>:'r-&C.-..l'W'--7Wll>o• The HP DeskWriter for Macintosh --. r._·.~·'"° .., ,.,1,..,.,...,. .. .,.,.,,.......... ............... """ ,,:.i,....v.c., - ~-Y'-1"'"... ~·.,·-· IPs _,,,,t-W••·~lo(jllo -·~-.oq..,,....., . ...., uses I exclusive inltjct tech .......... "..... ,..,.. .. ,,,_,.~ .. r....._..,,_...,., c_~ Dl.djllll~__ .....,.._., ..... nology for laser-sharp text and .,,,,, .. __,_ "'°'~t-- -.. -~.-.. .. _, .._,_or_... graphics. The kind of print quality and spc.«I you expect from HP. At a price you have to see to believe. F<1rjlist $365• yo1,1 get high-quality, water-resistant print outpul, com patibility with most popular soft ware, and HPs three-year limited warranty, the longestIn the industry. ow the only thing you could possibly want is the name of your nearby authorized HP dealer. 1b get that too,just<:all t-800-5F>2-8500.t See what you can do. Desk.Jct Printers Make it happPn. ·. F//Q9 HEWLETT ~~PACKARD .. Washington Apple Pi General Meeting 4th Saturday• 9:00 a.m. • Sept. & Nov.: Community & Cultural Center Northern VA Community College, 8333 Little River Turnpike, Annandale, VA Oct.: Holiday Inn, 8120 Wisconsin Ave., Bethesda, MD Sept. -

La Posición Y Evolución Del Product Placement De La Empresa Apple En El Sector Cinematográfico

UNIVERSIDAD DE EXTREMADURA FACULTAD DE CIENCIAS DE LA DOCUMENTACIÓN Y LA COMUNICACIÓN DEPARTAMENTO DE INFORMACIÓN Y COMUNICACIÓN LA POSICIÓN Y EVOLUCIÓN DEL PRODUCT PLACEMENT DE LA EMPRESA APPLE EN EL SECTOR CINEMATOGRÁFICO TRABAJO DE FIN DE GRADO Trabajo presentado por D. Manuel Flores Sánchez para la obtención del título de Grado en Información y Documentación, bajo la dirección del profesor D. Antonio García Díez BADAJOZ 2016 “La posición y evolución del product placement de la empresa Apple en el sector cinematográfico” Trabajo presentado por D. Manuel Flores Sánchez para la superación de la asignatura Trabajo Fin de Grado (Código 502297), del título de Información y Documentación (curso 2015-2016), bajo la dirección de D. Antonio García Díez, profesor del Departamento de Información y Comunicación de la Universidad de Extremadura. El alumno Vº Bº del Director Fdo. Manuel Flores Sánchez. Fdo. Antonio García Díez. “La posición y evolución del product placement de la empresa Apple en el sector cinematográfico”. Resumen El product placement es una técnica publicitaria que hoy en día se usa en todo tipo de obras artísticas, pero sin duda el cine es el sector donde más está presente este tipo de publicidad de la que participan las empresas para promocionar sus productos y servicios. Este tipo de publicidad ha ido adquiriendo una gran importancia a lo largo de los años, lo que provoca que actualmente haya una dura demanda y competitividad por parte de las empresas que la utilizan para poder emplazar sus productos en las producciones cinematográficas más taquilleras con el claro fin de conseguir más clientes que estén dispuesto a comprar sus productos. -

Macintosh Quadra 900

Macintosh Quadra 900 â Maximum power . expansion . LocalTalk networks without having Macintosh Quadra 900 Features â â flexibility—the Apple Macintosh to buy additional cards. Built-in Power and speed ä Quadra 900 personal computer support for all Apple displays makes it > 25 MHz 68040 microprocessor runs applica- delivers all three in the most powerful easy to connect your display without tions up to twice as fast as the Macintosh IIfx. Macintosh ever. adding video cards. And thanks to Memory With its ultrafast Motorola 68040 built-in support for up to 24 bits of > 4 megabytes RAM, expandable to 64 microprocessor, faster graphics color, you can work with photo- Expansion > Ten built-in ports for peripherals architecture, and improved SCSI and graphic-quality images. Ten built-in > Up to four storage devices NuBusä capabilities, the Quadra 900 ports give you instant access to print- > Five NuBus expansion slots runs applications up to twice as fast ers, scanners, high-capacity disk Display as the Macintosh IIfx. You will drives, and more. > Built-in support for all Apple monitors appreciate its speed every time you In the Quadra 900, you’ll also > Up to 32 bits per pixel for true color scroll, search, and sort—and even find the ultimate in flexibility. The more when the computer redraws Quadra 900 supports up to 64 mega- Features Built Into Every Macintosh complex graphics, recalculates intri- bytes of RAM, so you can work with Usability > Runs thousands of Macintosh applications cate spreadsheets, or reformats large larger files and many open applica- > Easy to set up, learn, and use documents. -

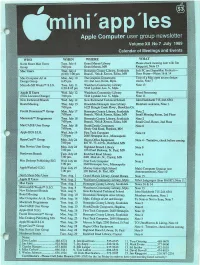

Apple Computer User Group Newsletter Volume XII No 7 July 1989 Calendar of Meetings and Events

""rxr$MyJmx<ww<&m8m5m "\Y??%m Apple Computer user group newsletter Volume XII No 7 July 1989 Calendar of Meetings and Events . -■■: j j ^ l : . .■;v;v:v;v.yiy.v.-.y. WHO WHEN WHERE WHAT North Shore Mac Users Tues. July 4 Grand Marais Library Please check meeting date with Jim Group 7:00 pm Grand Marais, MN Ringquist, Note 15 Mac Users Thur. July 6 Hennepin County Library, Southdale Soft PC and SuperMac Products (6:30) 7:00 pm Branch, 70th & Xerxes, Edina, MN Door Prizes—Notes 16 & 14 Mac Computer Art & Mon. July 10 The Graphics Department Tour of a Mac open access design Design Group 6:45 pm 411 2nd Ave. North, Mpls. studio, Note 7 MicroSoft® Works™ S.l.G. Tues. July 11 Washburn Community Library Note 13 6:30-8:45 pm 5244 Lyndale Ave. S.. Mpls. Apple II Users Wed. July 12 Washburn Community Library Word Processing (Note Location Change) 7:00 pm 5244 Lyndale Ave. S., Mpls. Note 11 New Richmond Branch Wed. July 12 New Richmond Technical School John Hackbarth 715-246-6561 Board Meeting Thur. July 13 Brookdale Hennepin Area Library Members welcome, Note 1. 7:00 pm 6125 Shingle Creek Pkwy., Brooklyn Ctr. Fourth Dimension™ Group Mon. July 17 Hennepin County Library, Southdale Note 2 7:00 pm Branch, 70th & Xerxes, Edina, MN Small Meeting Room, 2nd Floor Macintosh™ Programmer Tues. July 18 Hennepin County Library, Southdale Note 2 7:00 pm. Branch, 70th & Xerxes, Edina, MN Small Conf. Room, 2nd Floor MacCAD/E User Group Tues. July 18 Heath/Zenith Computers Note 8 7:00 pm.