Validation of a LISP Simulator

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

LISP Working Group S. Barkai Internet-Draft B

LISP Working Group S. Barkai Internet-Draft B. Fernandez-Ruiz Intended status: Experimental S. ZionB Expires: March 10, 2020 R. Tamir Nexar Inc. A. Rodriguez-Natal F. Maino Cisco Systems A. Cabellos-Aparicio J. Paillissé Vilanova Technical University of Catalonia D. Farinacci lispers.net October 10, 2019 Network-Hexagons: H3-LISP Based Mobility Network draft-barkai-lisp-nexagon-11 Abstract This document specifies combined use of H3 and LISP for mobility-networks: - Enabling real-time tile by tile indexed annotation of public roads - For sharing: hazards, blockages, conditions, maintenance, furniture.. - Between MobilityClients producing-consuming road geo-state information - Using addressable grid of channels of physical world state representation Status of This Memo This Internet-Draft is submitted in full conformance with the provisions of BCP 78 and BCP 79. Internet-Drafts are working documents of the Internet Engineering Task Force (IETF). Note that other groups may also distribute working documents as Internet-Drafts. The list of current Internet- Drafts is at https://datatracker.ietf.org/drafts/current/. Internet-Drafts are draft documents valid for a maximum of six months and may be updated, replaced, or obsoleted by other documents at any time. It is inappropriate to use Internet-Drafts as reference material or to cite them other than as "work in progress." This Internet-Draft will expire on October 4, 2019. Copyright Notice Copyright (c) 2019 IETF Trust and the persons identified as the document authors. All rights reserved. This document is subject to BCP 78 and the IETF Trust’s Legal Provisions Relating to IETF Documents (https://trustee.ietf.org/license-info) in effect on the date of publication of this document. -

ITC - Loc/ID Separation SIG Report 2014

ITC - Loc/ID Separation SIG Report 2014 In the framework of ITC Special Interest Groups activities, the Locator/ID Separation SIG has been created in 2012, aiming at gathering and disseminating activities about the Locator/ Identifier Separation paradigm. The paradigm is instantiated in LISP (Locator/Identifier Separation Protocol) and the highlights of 2013/2014 activities concern the advances in the IETF LISP WG, the evolution of the OpenLISP implementation, and the growth of the LISP Beta Network. The LISP WG at the IETF, in the last year, has worked in order to complete the milestones in its charter. The WG gave priority to the document aiming at describing the overall LISP architecture to newbies (draft-ietf-lisp-introduction). The document was lingering without real progress, until mid-2014, when new editors have been assigned to carry on the work. As of November 2014, the document just went over Working Group Last Call, which makes it ready to be forwarded to the IESG (Internet Engineering Steering Group) for evaluation and publication. Another main work item has been the request to IANA (Internet Assigned Numbers Authority) of an IPv6 address space reserved for LISP. Such work has been split in two documents, a first one - draft-ietf-lisp-eid-block - just simply requesting to IANA to reserve the addressing space for experimental purposes for at least 3 years; a second one - draft-ietf-lisp-eid-block-mgmnt - providing policy guidelines on how such dressing space has to be administered. The first document already went through Working Group Last Call and is now waiting the second document in order to move together forward to the IESG. -

Interdomain Traffic Engineering in a Locator/Identifier Separation Context

1 Interdomain Traffic Engineering in a Locator/Identifier Separation Context Damien Saucez, Benoit Donnet, Luigi Iannone, Olivier Bonaventure Universite´ catholique de Louvain, Belgium Abstract— The Routing Research Group (RRG) of the Internet In this paper, we propose a service helping an ISP, using Research Task Force (IRTF) is currently discussing several archi- identifier/locator separation, to deploy a traffic engineering tectural solutions to build an interdomain routing architecture service controlling both incoming and outgoing packet flows. that scales better than the existing one. The solutions family currently being discussed concerns the addresses separation This service is contacted by clients (i.e., LISP routers in this into locators and identifiers, LISP being one of them. Such a paper) for ranking paths between locators of the source and separation provides opportunities in terms of traffic engineering. the destination. The service performs the ranking using cost In this paper, we propose an open and flexible solution that functions that return a value characterizing a path according allows an ISP using identifier/locator separation to engineer its to one or more metrics. One of the main advantages of the interdomain traffic. Our solution relies on the utilization of a service that transparently ranks paths using cost functions. We cost functions is that they can be combined in order to form implement a prototype server and demonstrate its benefits in a a more complex function. Clients receive the list of ranked LISP testbed. paths so that the first path in the list is the most preferable while the last one is the least desirable. We implement our path selection mechanism in a tool I. -

LISP-EC: Enhancing LISP with Egress Control

LISP-EC: Enhancing LISP with Egress Control Ho Dac Duy Nguyen, Stefano Secci Sorbonne Universités, UPMC Univ Paris 06, UMR 7606, LIP6. Email: {ho-dac-duy.nguyen, stefano.secci}@upmc.fr Abstract—The Locator/Identifier Separation Protocol (LISP) indeed, LISP allows to associate to each prefix (announced was specified a few years ago by the Internet Engineering Task via BGP) a preferred routing locator, among many possible Force (IETF) to enhance the Internet architecture with novel ones, by means of a mapping system (independent of BGP). inbound control capabilities. Such capabilities are particularly needed for multihomed networks that dispose of multiple public In this way, a multihomed network can perform egress traffic IP routing locators for their IP networks, and that are willing engineering using BGP, while using LISP for ingress traffic to exploit them in a better way than what possible with the engineering. However, to dispose of both ingress and egress legacy Border Gateway Protocol (BGP) [8]. In this work, we traffic engineering for a given multihomed network, the two specify how to enhance the LISP routing system to perform protocols are supposed to inter-work, which is not specified in egress control too. Our goal is to give the highest possible routing optimization degree to LISP networks, so that ingress and egress the standard. More precisely, it is not explicitly specified how traffic engineering strategies can be jointly performed, without LISP and BGP should run in a same node, or how physically requiring coordination between LISP and BGP. We design the separated LISP and BGP routers should be interconnected, etc. -

A Deep Dive Into the LISP Cache and What Isps Should Know About It Juhoon Kim, Luigi Iannone, Anja Feldmann

A Deep Dive into the LISP Cache and What ISPs Should Know about It Juhoon Kim, Luigi Iannone, Anja Feldmann To cite this version: Juhoon Kim, Luigi Iannone, Anja Feldmann. A Deep Dive into the LISP Cache and What ISPs Should Know about It. 10th IFIP Networking Conference (NETWORKING), May 2011, Valencia, Spain. pp.367-378, 10.1007/978-3-642-20757-0_29. hal-01583403 HAL Id: hal-01583403 https://hal.inria.fr/hal-01583403 Submitted on 7 Sep 2017 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Distributed under a Creative Commons Attribution| 4.0 International License ADeepDiveintotheLISPCache and what ISPs should know about it Juhoon Kim!, Luigi Iannone, and Anja Feldmann Deutsche Telekom Laboratories – Technische Universit¨at Berlin Ernst-Reuter-Platz 7, 10587 Berlin, Germany Abstract. Due to scalability issues that the current Internet is facing, the research community has re-discovered the Locator/ID Split paradigm. As the name suggests, this paradigm is based on the idea of separating the identity from the location of end-systems, in order to increase the scalability of the Internet architecture. One of the most successful pro- posals, currently under discussion at the IETF, is LISP (Locator/ID Separation Protocol). -

Strategic Path Diversity Management Across Internet Layers

LABORATOIRE D'INFORMATIQUE DE PARIS 6 STRATEGIC PATH DIVERSITY MANAGEMENT ACROSS INTERNET LAYERS Advisor: Doctoral Dissertation of: Prof. Stefano SECCI Ho Dac Duy NGUYEN 2018 Th`ese Pr´esent´eepour obtenir le grand de docteur de la Sorbonne Universit´e Sp´ecialit´e:Informatique Ho Dac Duy NGUYEN STRATEGIC PATH DIVERSITY MANAGEMENT ACROSS INTERNET LAYERS Soutenue le 22 octobre 2018 devant le jury compos´ede : Rapporteurs: Prof. Fabio MARTIGNON Univ. Bergamo. Prof. Sidi-Mohamed SENOUCI Univ. Bourgogne. Examinateurs: Dr. Geraldine TEXIER Institut Mines-T´el´ecom. Dr. Luigi IANNONE Institut Mines-T´el´ecom. Prof. Maria POTOP BUTUCARU Sorbonne Universit´e. Directeur de th`ese: Prof. Stefano SECCI Cnam. LABORATOIRE D'INFORMATIQUE DE PARIS 6 STRATEGIC PATH DIVERSITY MANAGEMENT ACROSS INTERNET LAYERS Author: Ho Dac Duy NGUYEN. Defended on October 22, 2018, in front of the committee composed of: Referees: Prof. Fabio MARTIGNON Univ. Bergamo. Prof. Sidi-Mohamed SENOUCI Univ. Bourgogne. Examiners: Dr. Geraldine TEXIER Institut Mines-T´el´ecom. Dr. Luigi IANNONE Institut Mines-T´el´ecom. Prof. Maria POTOP BUTUCARU Sorbonne Universit´e. Advisor: Prof. Stefano SECCI Cnam. I To my family! Abstract We present in this thesis novel routing protocols able to take into consideration strategic aspects when deciding which path among many to take, and that at the Internet com- munication network scale. The standpoint adopted in this study is that novel routing architectures are exposing a higher path diversity to networks and applications so that networks and applications can be made capable to more intelligently select their strat- egy when selecting toward which path to forward their traffic, taking into consideration operational costs as well as performance goals. -

LISP-Click: a Click Implementation of the Locator/ID Separation Protocol

LISP-Click: A Click implementation of the Locator/ID Separation Protocol Damien Saucez Van Nam Nguyen Universite catholique de Louvain Universite catholique de Louvain Louvain-la-Neuve, Belgium Louvain-la-Neuve, Belgium 1. INTRODUCTION The network research community has recently started to work on the design of an alternate Internet Architec- ture aiming at solving some scalability issues that the current Internet is facing. The Locator/ID separation paradigm seems to well fit the requirements for this new Internet Architecture. The principle of this paradigm is to separate the identification part from the localization one. In today’s Internet, nodes are identified by their IP address and the same IP address is used to localize the node in the Internet. In the Locator/ID separation Figure 1: LISP-Click Architecture proposals, locators are used to localize the nodes on the Internet (i.e., packets are routed towards the Locator) while the identification of the node is let independent of the routing infrastructure thanks to the ID. In this sifier. If the packet is related to LISP, it is pushed in work, we only consider LISP (Locator/ID Separation a LISP element. Both encapsulation and decapsulation Protocol), proposed by Cisco [1]. can be performed by the element (by LISPEncap and LISP is a map-and-encap solution where the inner LISPDecap, respectively). header addresses are identifiers and outer header ad- Mappings are at the core of LISP and are maintained dresses are locators. A set of locators is associate to by LISPCache that can be queried by LISPEncap and each identifier via a mapping. -

An Open Source Implementation of the Locator/ID Separation Protocol

OpenLISP: An Open Source Implementation of the Locator/ID Separation Protocol L. Iannone D. Saucez O. Bonaventure TUB – Deutsche Telekom Laboratories AG, Universit´ecatholique de Louvain Universit´ecatholique de Louvain [email protected] [email protected] [email protected] Abstract—The network research community has recently description of the encapsulation and decapsulation operations, started to work on the design of an alternate Internet Archi- the forwarding operation and offer several options as mapping tecture aiming at solving some scalability issues that the current system. Nevertheless there is no specification of an API to Internet is facing. The Locator/ID separation paradigm seems to well fit the requirements for this new Internet Architecture. allow the mapping system to interact with the forwarding Among the various solutions, LISP (Locator/ID Separation Pro- engine. In OpenLISP we proposed and implemented a new tocol), proposed by Cisco, has gained attention due to the fact socket based solution in order to overcome this issue: the that it is incrementally deployable. In the present paper we give Mapping Sockets. Mapping sockets make OpenLISP an open a short overview on OpenLISP, an open-source implementation and flexible solution, where different approaches for the lo- of LISP. Beside LISP’s basic specifications, OpenLISP provides a new socket-based API, namely the Mapping Sockets, which makes cator/ID separation paradigm can be experimented, even if OpenLISP an ideal experimentation platform for LISP, but also not strictly related to LISP. To the best of our knowledge, other related protocols. OpenLISP is the only existing effort in developing an open source Locator/ID separation approach. -

LISP Designers

QuickTime™ and a decompressor are needed to see this picture. LISP:LISP: AnAn ArchitecturalArchitectural SolutionSolution toto MultiMulti--homing,homing, TrafficTraffic Engineering,Engineering, andand InternetInternet RouteRoute ScalingScaling Dave Meyer & Dino Farinacci LISP Designers: Dave Meyer, Vince Fuller, Darrel Lewis, Andrew Partan, John Zwiebel, Scott Brim, Noel Chiappa & Dino Farinacci AgendaAgenda • Problem Statement • Architectural Concepts – Separating Identity and Location – Map-n-Encap to Implement Level of Indirection • Unicast & Multicast Data Plane Operation • Mapping Database Mechanism – LISP-ALT • Locator Reachability • Interworking LISP Sites and Legacy Sites • Deployment Status – Present Prototype Implementation – Present World-Wide LISP Pilot Network • Q&A LISP Architecture Nanog 45 - Jan 2009 Slide 2 ProblemProblem StatementStatement • What provoked this? – Stimulated by problem statement effort at the Amsterdam IAB Routing Workshop on October 2006 • RFC 4984 – More info on problem statement: • http://www.vaf.net/~vaf/apricot-plenary.pdf LISP Architecture Nanog 45 - Jan 2009 Slide 3 ScalingScaling InternetInternet RoutingRouting StateState LISP Architecture Nanog 45 - Jan 2009 Slide 4 RoutingRouting TableTable SizeSize ProblemProblem Before LISP - all this state in red circle After LISP - this amount in red circle 10^7 routes A 16-bit number! LISP Architecture Nanog 45 - Jan 2009 Slide 5 GrowthGrowth inin MultiMulti--HomingHoming Provider A Provider B 10.0.0.0/8 11.0.0.0/8 (1) Improve site multi-homing a) Can control -

LISP Working Group S. Barkai Internet-Draft Contextream Inc

LISP Working Group S. Barkai Internet-Draft ConteXtream Inc. Intended status: Experimental D. Farinacci Expires: April 30, 2015 lispers.net D. Meyer Brocade F. Maino V. Ermagan Cisco Systems A. Rodriguez-Natal A. Cabellos-Aparicio Technical University of Catalonia October 27, 2014 LISP Based FlowMapping for Scaling NFV draft-barkai-lisp-nfv-05 Abstract This draft describes an RFC 6830 Locator ID Separation Protocol (LISP) based distributed flow-mapping-fabric for dynamic scaling of virtualized network functions (NFV). Network functions such as subscriber-management, content-optimization, security and quality of service, are typically delivered using proprietary hardware appliances embedded into the network as turn-key service-nodes or service-blades within routers. Next generation network functions are being implemented as pure software instances running on standard servers - unbundled virtualized components of capacity and functionality. LISP-SDN based flow-mapping, dynamically assembles these components to whole solutions by steering the right traffic in the right sequence to the right virtual function instance. Requirements Language The key words "MUST", "MUST NOT", "REQUIRED", "SHALL", "SHALL NOT", "SHOULD", "SHOULD NOT", "RECOMMENDED", "MAY", and "OPTIONAL" in this document are to be interpreted as described in [RFC2119] Status of This Memo This Internet-Draft is submitted in full conformance with the provisions of BCP 78 and BCP 79. Internet-Drafts are working documents of the Internet Engineering Task Force (IETF). Note that other groups may also distribute working documents as Internet-Drafts. The list of current Internet- Drafts is at http://datatracker.ietf.org/drafts/current/. Barkai, et al. Expires April 30, 2015 [Page 1] Internet-Draft October 2014 Internet-Drafts are draft documents valid for a maximum of six months and may be updated, replaced, or obsoleted by other documents at any time. -

Le Protocole LISP ( Locator/ID Separation Protocol )

Vers un renforcement de l’architecture Internet : le protocole LISP (“Locator/ID Separation Protocol”) JCSA 2013" " " Luigi Iannone! Institut Mines-Télécom 1 Road Map" -" Why LISP???! -" LISP Data Plane! •" RFC 6830! -" LISP Control Plane! •" RFC 6833; RFC 6836; draft-ietf-lisp-ddt-01.txt! -" The Big Picture! Luigi Iannone! Telecom ParisTech! LISP - JCSA 2013! 2! Why LISP?????! Luigi Iannone! Telecom ParisTech! LISP - JCSA 2013! 3! Internet’s Scaling Issues" “It is commonly recognized that today’s Internet routing and addressing system is facing serious scaling problems.” -" D. Meyer, L. Zhang, K. Fall, “Report from IAB Workshop on Routing and Addressing”, RFC 4984, IETF, September 2007.! Luigi Iannone! Telecom ParisTech! LISP - JCSA 2013! 4! The BGP’s FIB inflation problem! No... it is not just natural Internet growth" 01-Jan-94 to 14-March-11 Source: http://bgp.potaroo.net/index-bgp.html IPv4 IPv6 Peak PrefixUpdate Rate per Second BGP Forwarding Information Base (FIB) and Churn Explosion: •"PI (Provider Independent) prefix Churn can have peaks of thousands per assignment! seconds •" Multi-homing! Churn increases the need processing power •" Traffic-Engineering! •" Security ! #"Remember the YouTube incident?! Luigi Iannone! Telecom ParisTech! LISP - JCSA 2013! 5! Cause: The overloaded IP address semantic" -" An IP Address tells:! •" Who you are! #"Hi! I am Luigi Iannone 46 Rue Barreault 75013 Paris France ! •" Where you are! #".... and I am in Luigi Iannone 46 Rue Barreault 75013 Paris France! -" This design was OK in the 70s-80s! •" Because was easier to implement! •" Because the Internet was a small academic network of networks ! Luigi Iannone! Telecom ParisTech! LISP - JCSA 2013! 6! From “Divide and Conquer” ....! ....to “Split and Scale”! “The Research Group has rough consensus that separating identity from location is desirable and technically feasible. -

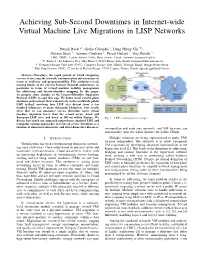

Achieving Sub-Second Downtimes in Internet-Wide Virtual Machine Live Migrations in LISP Networks

Achieving Sub-Second Downtimes in Internet-wide Virtual Machine Live Migrations in LISP Networks Patrick Raad ∗‡, Giulio Colombo y, Dung Phung Chi #∗, Stefano Secci ∗, Antonio Cianfrani y, Pascal Gallard z, Guy Pujolle ∗ ∗ LIP6, UPMC, 4 place Jussieu 75005, Paris, France. Email: fi[email protected] y U. Roma I - La Sapienza, P.za Aldo Moro 5, 00185 Rome, Italy. Email: [email protected] # Vietnam National University (VNU), Computer Science dept., Hanoi, Vietnam. Email: [email protected] z Non Stop Systems (NSS), 27 rue de la Maison Rouge, 77185 Lognes, France. Email: fpraad, [email protected] Abstract—Nowadays, the rapid growth of Cloud computing services is stressing the network communication infrastructure in terms of resiliency and programmability. This evolution reveals missing blocks of the current Internet Protocol architecture, in particular in terms of virtual machine mobility management for addressing and locator-identifier mapping. In this paper, we propose some changes to the Locator/Identifier Separation Protocol (LISP) to cope this gap. We define novel control-plane functions and evaluate them exhaustively in the worldwide public LISP testbed, involving four LISP sites distant from a few hundred kilometers to many thousands kilometers. Our results show that we can guarantee service downtime upon virtual machine migration lower than the second across Asian and European LISP sites, and down to 300 ms within Europe. We Fig. 1. LISP communications example discuss how much our approach outperforms standard LISP and triangular routing approaches in terms of service downtime as a function of datacenter-datacenter and client-datacenter distances. metropolitan and wide area networks, and VM locations can consequently span the whole Internet for public Clouds.