EMC-Compliant 10/100-Mbps Ethernet PHY

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Power Over Ethernet

How To | Power over Ethernet Introduction Power over Ethernet (PoE) is a technology allowing devices such as IP telephones to receive power over existing LAN cabling. This technical note is in four parts as follows: • PoE Technology • How PoE works • Allied Telesyn PoE implementation • Command Reference What information will you find in this document? The first two parts of this document describe the PoE technology, and the installation and management advantages that PoE can provide. This is followed by an overview of how PoE works, Power Device(PD) discovery, PD classification, and the delivery of power to PD data cables. The third part of this document focuses on Allied Telesyn’s implementation of PoE on the AT-8624PoE switch. The document concludes with a list of configuration and monitoring commands. Which product and software version does this information apply to? The information provided here applies to: • Products: AT8624PoE switch • Software version: 2.6.5 C613-16048-00 REV C www.alliedtelesyn.com PoE Technology Power over Ethernet is a mechanism for supplying power to network devices over the same cabling used to carry network traffic. PoE allows devices that require power, called Powered Devices (PDs), such as IP telephones, wireless LAN Access Points, and network cameras to receive power in addition to data, over existing infrastructure without needing to upgrade it. This feature can simplify network installation and maintenance by using the switch as a central power source for other network devices. A device that can source power such as an Ethernet switch is termed Power Sourcing Equipment (PSE). Power Sourcing Equipment can provide power, along with data, over existing LAN cabling to Powered Devices. -

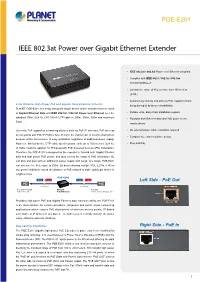

IEEE 802.3At Power Over Gigabit Ethernet Extender

POE-E201 IEEE 802.3at Power over Gigabit Ethernet Extender • IEEE 802.3at / 802.3af Power over Ethernet compliant • Complies with IEEE 802.3 / 802.3u / 802.3ab 10/100/1000Base-T • Extends the range of PoE to more than 100 meters (328ft.). • Automatically detects and protects PoE equipment from Long Distance High Power PoE and Gigabit Data Extension Solution being damaged by incorrect installation PLANET POE-E201 is a newly designed simple device which extends both the reach of Gigabit Ethernet Data and IEEE 802.3at / 802.3af Power over Ethernet over the • Multiple units, daisy-chain installation support standard 100m (328 ft.) CAT. 5/5e/6 UTP cable to 200m, 300m, 400m and maximum • Forwards both Ethernet data and PoE power to the 500m. remote device Currently, PoE supported networking devices such as PoE IP cameras, PoE wireless • No external power cable installation required access points and PoE IP Phones have become the mainstream of network deployment • Compact size, wall-mountable design because of the convenience of easy installation regardless of additional power supply. However, limited by the UTP cable specifications, only up to 100 meters (328 ft.) • Plug and Play of cable could be applied for IP-based and PoE powered devices (PD) installation. Therefore, the POE-E201 is designed as the repeater to forward both Gigabit Ethernet data and high power PoE power, and thus extend the range of PoE installation. By just plug and play without additional power supply and setup, one single POE-E201 can increase the PoE range to 200m. By daisy-chaining multiple POE-E201s, it offers you great flexibility to extend the distance of PoE network to triple, quadruple further in length or more. -

Total Networking Solutions for IT/OT Convergence

Total Networking Solutions for IT/OT Convergence Total networking solutions that can improve security, productivity and operational efficiency today, while laying the foundations for tomorrow‘s intelligent manufacturing opportunities. Edition 2020 Belden Total Networking Solutions Belden combines the strength of Hirschmann & Hirschmann IT switches, Tripwire traffic trend tracking and risk management systems and Belden Ethernet cables for comprehensive networking solutions for IT/OT convergence. You can depend on us to keep your mission-critical systems running steady and securely. Easy to implement, intelligent and secured IT/OT converged solutions for networks ranging from small to large size. Belden IT/OT converged solutions Belden has over 30 year’s experiences on • We offer the broadest selection of products, We will consult with you to develop a strategy or offering integrated network solutions for for a complete, end-to-end network we will develop and implement your full design complex industrial facilities and systems. solution. – either way our staff is available to you. As the size of industrial facility network • Our sales and engineering professionals can and demand for higher efficiency increase, audit, recommend/design, configure and Training the IT network is required to converge with assemble the products and systems to your Backed by years of meeting and exceeding industrial network. At the same time, lots specific requirements. the needs of a broad range of end-user of IT technologies, including big-data, AI, • Our global manufacturing, distribution and applications, Belden is ideally suited to offer visual identity and robotics, keep pushing the support network makes our products and beginners and networking experts alike the industrial network evolution forward. -

Ethernet at New Speeds, Deterministic Networking, and Power Over Everything!

Ethernet Evolving: Ethernet at New Speeds, Deterministic Networking, and Power over Everything! Dave Zacks Distinguished System Engineer @DaveZacks Peter Jones Principal Engineer @petergjones #NBASET BRKCRS-3900 #HighBitrate Ethernet Evolving: Ethernet at New Speeds, Deterministic Networking, and Power over Everything! BRKCRS-3900 – Session Overview We have a great session for you today … so sit back, buckle in, and let’s get started! Come to this session to get geared up on the latest developments in Ethernet for Campus and Branch networks. The Ethernet we all know and love is evolving at a rapid pace. With the release of MultiGigabit Ethernet on Cisco's latest Catalyst access switching platforms, you can connect new devices that support MultiGigabit connections at 2.5Gb/s and 5Gb/s over Cat5e/6 copper. No longer are 1Gbps and 10Gbps the only connectivity options – intermediate speeds are now possible. Cisco’s Multigigabit Technology is a key enabler for upcoming 802.11ac Wave 2 wireless deployments, where the Ethernet bandwidth required per AP exceeds 1Gb/s. Multigigabit switches also support other high-bandwidth devices in the Ethernet access layer without requiring expensive and time-consuming re-cabling for 10GBASE-T. We will talk about how Cisco MultiGigabit switches work, and how they will change your network. As well, we will discuss work being done in (and out of) the standards bodies to broaden the footprint for Ethernet, and enable the Internet of Everything. This includes additional Ethernet speeds, capabilities for deterministic networking functionality over an Ethernet infrastructure (precision timing, pre-emption, time scheduling, etc), and of course we need to provide more Power over Ethernet to more devices, in more places, than ever. -

2.5Gbase-T & 5Gbase-T

Structured Cabling Considerations for 2.5GBASE-T & 5GBASE-T While most data centers are prepared for current bandwidth demands and maintain up-to-date backbones, some enterprise networks are in danger of falling behind. Increased wireless traffic has already taxed many enterprise environments. IEEE 802.11ac Wave 1 and Wave 2 standards, along with bring-your-own-device (BYOD) policies, encourage increased Wi-Fi activity and place significant strain on existing 1000BASE-T systems. And it’s not just businesses that are feeling the pressure to upgrade. Hospitals and schools are seeing significant jumps in data growth. Across the health care industry there is a huge push to support staff, patients, and visitors with reliable wireless access. High-speed internet is also vital for supporting student education at all levels. Whether performing online research for papers, giving in-class presentations, or engaging in extracurricular learning, students need greater bandwidth for quick access to information in order to achieve their goals. Both hospitals and schools will fail to meet the growing demand for reliable network performance without the right cabling infrastructure in place. 2.5GBASE-T and 5GBASE-T Increased wireless demand has pushed network speed requirements beyond 1 Gb/s. To support faster data rates, upgrading to a Cat 6A infrastructure is inevitable. However, with more than 70 billion meters of Cat 5e and Cat 6 cable installed over the last 12 years, many facilities and IT managers are hesitant to spend the resources on a complete Cat 6A upgrade. Both IEEE and TIA attempted to address this issue by developing standards for 2.5GBASE-T and 5GBASE-T. -

4 Port Gigabit Power Over Ethernet Pcie Network Card - PSE / Poe PCI Express NIC Startech ID: ST4000PEXPSE

4 Port Gigabit Power over Ethernet PCIe Network Card - PSE / PoE PCI Express NIC StarTech ID: ST4000PEXPSE The ST4000PEXPSE 4-Port PoE NIC lets you add four Gigabit Power over Ethernet ports through a single PCI Express slot. Each port can provide up to 25.5W of power, combining network data and power over a single Ethernet cable for reduced cable clutter and added convenience for remote PoE devices. The PCI express PoE card supports the IEEE 802.3at (Type 1 and 2) standard for Power Sourcing Equipment (PSE), and can deliver up to 48V DC power to compliant Powered Devices (PD). This eliminates the need for a separate power source and data connection for PoE devices such as IP cameras, IP phones or wireless access points. Suitable for any standard profile PCIe-enabled client, server or workstation, the PoE network card supports features such as Jumbo Frames (up to 9KB), VLAN tagging and Wake on LAN (WoL). Backed by a StarTech.com 2-year warranty and free lifetime technical support. Applications Create a host computer for networked security cameras situated in remote areas, where standard power connection is not possible Install PoE-powered Wireless Access Points (WAP) or repeaters in industrial, warehousing or business environments Enable remote installation of touchscreens or information kiosks www.startech.com 1 800 265 1844 Features Four 10/100/1000 Mbps compatible PoE RJ45 ports Fully compliant with IEEE 802.3at (Type 1 & 2) Power over Ethernet standards Power Sourcing Equipment (PSE) supports up to 48V, 25.5 Watts max. output per port -

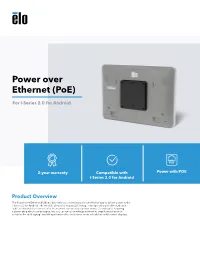

Power Over Ethernet (Poe)

Power over Ethernet (PoE) For I-Series 2.0 for Android 2-year warranty Compatible with Power with POE I-Series 2.0 for Android Product Overview The Power-over-Ethernet (POE) module offers a convenient and cost effective way to deliver power to the I-Series 2.0 for Android. The module allows you to put a DC voltage onto specific pairs of the Ethernet cable so that devices connected to the network can use it as a power source. So instead of requiring a power drop which can be expensive, you can run a low voltage network to simplify installation of solutions for shelf signage and AV applications like conference room schedulers or AV control displays. Power over Ethernet (PoE) Specifications Color Black Compatibility I-Series 2.0 for Android POE Standard Protocols IEEE802.3, 10BASE T/1000BASE-T IEEE802.3u,100BASE-TX, IEEE802.3at, Power over Ethernet Input Connection POE+ (30W) - Warning: Please do not use other types of PoE such as PoE (15.4W) or UPoE (65W) Dimensions 3.5" x 3.5" x 0.8" / 89.2 mm x 89.2 mm x 20.5 mm Shipping Dimensions 6.5" x 6.3" x 2.5" / 165 mm x 160 mm x 63.5 mm Unpackaged – 0.35 lbs / 0.16 kgs Weight Packaged – 0.70 lbs / 0.32 kgs Temperature Operating: 0°C to 40°C (32°F to 104°F) Storage: -20°C to 50°C (-4°F to 122°F) Operating: 20% to 80% Humidity (Non-Condensing) Storage: 5% to 95% POE Module only: UL/cUL (US), IC (Canada), CE (Europe), CB (International), VCCI (Japan), RCM (Australia) Regulatory Approvals and Declarations Tested with I-Series 2.0 for Android - FCC (US), China RoHS (China) Adding a spacer bracket will allow 100 mm x 100 mm VESA mounting. -

Introduction Basic Principles of Poe Power Over Ethernet IEEE 802.3Af

Introduction White Paper The networking of industrial installations is an important and steadily expanding topic in the field of automation. Just as office networking once did, Ethernet networking is now advancing Power over Ethernet into industry and making strides to replace existing standards such as Profibus. A number of companies now offer networking solutions under the name Industrial Ethernet. Their offers range from small entry level switches through modular Gigabit switches right up to wireless IEEE 802.3af LAN (WLAN) access points. The IEEE 802.3af standard, which supports the simultaneous network transfer of data and power, was introduced to reduce installation costs and provide more flexible networking facilities. It means that, instead of separate network cables for data, power and telephones (VoIP), everything can now be conveyed via a single LAN cable. Many offices are already successfully using equipment such as IP telephones and access points with PoE functionality. Unlike office networks with their star-shaped network structures, industrial applications generally use a linear arrangement. The industrial use of Power over Ethernet (PoE) is somewhat restricted by the fact that the PoE standard describes only point-to-point connections. Basic principles of PoE The Power over Ethernet (PoE) facility, which is standardized under IEEE 802.3af, was developed to reduce the cost of network planning, cabling and installation. The equipment is powered Contents directly over the data line (e.g. for distances up to 100m via a CAT 5/5e cable). PoE makes Introduction 1 network planning flexible and independent of switch cabinets and power sources, and also saves Basic principles of PoE 1 additional outlay for power and telephone networks (VoIP). -

Power Over Ethernet (Poe) Switch

Power over Ethernet (PoE) Switch SPECIFICATION The PoE Switch, sourced from Netgear and certified by Enlighted, powers the Enlighted Gateway and provides data switching power for the Enlighted Control network. OVERVIEW The PoE Switch provides power and data from a single point, using Power over Ethernet via a single CAT-5 or 6 cable. The eight Fast Ethernet ports can be used for PoE Switch any 10/100 Mbps link and four of these ports can supply industry-standard IEEE L 9.3" 235 mm 802.3af power. The advanced auto-sensing algorithm gives power only to 802.3af end W 4.1" 103 mm devices, ensuring no damage to proprietary PoE or non-PoE equipment. In addition, the H 1.1" 27 mm switch discontinues the power when PoE devices are disconnected. Easy and reliable, Weight 27.2 oz .77 kg the device automatically determines PoE requirements, speed, duplex, and cable type. TECHNICAL SPECIFICATION Network Ports • Storage temperature: 14° to 158° F • 8 auto speed-sensing 10/100 RJ-45 (–10° to 70° C) ports • Operating humidity: 90% maximum relative humidity, noncondensing Network Protocol and Standards • Storage humidity: 95% maximum • IEEE 802.3i 10BASE-T relative humidity, noncondensing • IEEE 802.3u 100BASE-TX • Operating altitude: 10,000 ft. • IEEE 802.3x Flow Control (3,000 m) maximum • IEEE 802.3af DTE Power via MDI • Storage altitude: 10,000 ft. Performance Specifications (3,000 m) maximum • Forwarding modes: Store-and-forward Electromagnetic Immunity • Bandwidth: 1.6 Gbps • EN 55024 • Network latency: Less than 20 µs for 64-byte frames in store-and-forward -

POWER OVER ETHERNET (POE) on the Same Conductors As Data

Benefits of PoE include increased mobility for end devices, added safety (no AC power involved), simplicity of installation, reliability, security and cost savings. Alternative A implements a simplex, or ‘phantom feeding’ method for delivering power to the end device. Power is carried POWER OVER ETHERNET (POE) on the same conductors as data. CAT-5 cabling for standard 10BaseT and 100Base-TX Ethernet uses two data/signal pairs connected to pins 1 and 2 and pins 3 and 6 on RJ-45 connectors. With the introduction of new Ethernet-enabled devices expanding Power sourcing equipment superimposes power onto these pins geometrically, the need to power these devices from standard AC via the center tap of internal signal coupling transformers. In the power outlets has become a limiting factor. IP telephones, powered device (PD) the power is derived from these lines using wireless access points, IP cameras and device servers are the reverse technique. examples of devices limited by the need to have an AC power outlet nearby to plug in a DC power adapter. At best, power supply installation and wiring adds labor and results in the mess of extra wiring; worst case, the lack of nearby AC power means devices cannot be installed where they are needed. In response to this need, IEEE developed IEEE802.3af to standardize a system of supplying low voltage power to networked devices via the communications line. Released in mid- 2003, the standard was entitled, Data Terminal Equipment (DTE) Power via Media Dependant Interface (MDI). It is more commonly referred to as Power over Ethernet (POE). -

Ethernet at New Speeds, Deterministic Networking, and Power Over Everything!

Ethernet Evolving: Ethernet at New Speeds, Deterministic Networking, and Power over Everything! Dave Zacks Distinguished System Engineer @DaveZacks Peter Jones Principal Engineer @petergjones #NBASET #HighBitrate Ethernet Evolving: Ethernet at New Speeds, Deterministic Networking, and Power over Everything! BRKCRS-3900 – Session Overview We have a great session for you today … so sit back, buckle in, and let’s get started! Come to this session to get geared up on the latest developments in Ethernet for Campus and Branch networks. The Ethernet we all know and love is evolving at a rapid pace. With the release of MultiGigabit Ethernet on Cisco's latest Catalyst access switching platforms, you can connect new devices that support MultiGigabit connections at 2.5Gb/s and 5Gb/s over Cat5e/6 copper. No longer are 1Gbps and 10Gbps the only connectivity options – intermediate speeds are now possible. Cisco’s Multigigabit Technology is a key enabler for upcoming 802.11ac Wave 2 wireless deployments, where the Ethernet bandwidth required per AP exceeds 1Gb/s. Multigigabit switches also support other high-bandwidth devices in the Ethernet access layer without requiring expensive and time-consuming re-cabling for 10GBASE-T. We will talk about how Cisco MultiGigabit switches work, and how they will change your network. As well, we will discuss work being done in (and out of) the standards bodies to broaden the footprint for Ethernet, and enable the Internet of Everything. This includes additional Ethernet speeds, capabilities for deterministic networking functionality over an Ethernet infrastructure (precision timing, pre-emption, time scheduling, etc), and of course we need to provide more Power over Ethernet to more devices, in more places, than ever. -

24-Port Gigabit Ethernet Poe+ Switch with 10 Gbe Uplink

24-Port Gigabit Ethernet PoE+ Switch with 10 GbE Uplink 24 x PoE ports, IEEE 802.3at Power over Ethernet (PoE+), 2 x 10 GbE SFP+ open slots, Endspan, 19" Rackmount Part No.: 561143 The new backbone for your video surveillance! The Intellinet 24-Port Gigabit Ethernet PoE+ Switch with 2 SFP+ Ports (561143) is designed to pass both data and electrical power to a number of PoE-compatible devices via standard Cat5e or Cat6 network cables. Equipped with 24 Gigabit Ethernet ports, all of which support 802.3at/af Power over Ethernet (PoE/PoE+), this switch can power IP surveillance cameras, Wireless LAN access points and bridges, VoIP (Voice over Internet Protocol) telephones and more while providing a total switching capacity of 88 Gbps for your network. Everything you need for your video surveillance network Intellinet's 24-Port Gigabit Ethernet PoE+ Switch can comfortably power up to 24 PoE-enabled network cameras, but it does not end there. Thanks to its 10 GbE uplink ports, the switch is well-equipped to create a high-speed connection to your NVR solution. There will never be a shortage of available bandwidth, bottlenecks are a thing of the past, and there is plenty of PoE power to go around. And all of that comes with a low price previously thought impossible for a 10 GbE networking solution. Power over Ethernet 802.3at The Intellinet 24-Port Gigabit Ethernet PoE+ Switch with 2 SFP+ 10 Gigabit Uplink Ports supports the IEEE 802.3at protocol and is designed to deliver up to 30 watts of power per port*.