Implementation of AC-3 Decoder on Tms320c62x

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Ts 103 190-2 V1.2.1 (2018-02)

ETSI TS 103 190-2 V1.2.1 (2018-02) TECHNICAL SPECIFICATION Digital Audio Compression (AC-4) Standard; Part 2: Immersive and personalized audio 2 ETSI TS 103 190-2 V1.2.1 (2018-02) Reference RTS/JTC-043-2 Keywords audio, broadcasting, codec, content, digital, distribution, object audio, personalization ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the only prevailing document is the print of the Portable Document Format (PDF) version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at https://portal.etsi.org/TB/ETSIDeliverableStatus.aspx If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommiteeSupportStaff.aspx Copyright Notification No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI. -

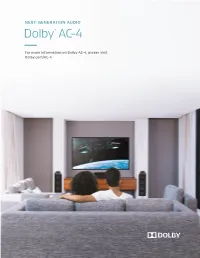

Dolby AC-4, Please Visit Dolby.Com/AC-4

NEXT-GENERATION AUDIO Dolby ® AC-4 For more information on Dolby AC-4, please visit Dolby.com/AC-4. ® ® NEX T-GENERATION AUDIO ED2 OR Dolby AC-4 PCM & METADATA AC-3 AC-4 PCM Integrating Personalized and Immersive Programming into Broadcast Operations The diagram below outlines a representative end-to-end signal flow for live and post-produced content through the broadcast ecosystem. PRODUCTION OPEN STANDARDS OUTSIDE BROADCAST BROADCASTER PAY TV OPERATOR CONFIDENCE MONITOR OUTPUT LEGACY RENDERER/ OBJECT AUDIO PROCESSOR ENCODER CHANNEL AUDIO OBJECT METADATA AUDIO MONITORING METADATA ANALYSIS GENERATION DISTRIBUTION INTEGRATED ENCODER RECEIVER/ MASTER DECODER CONTROL CHANNEL METADATA & OBJECT CHANNEL / GROUPING EMISSION INTEGRATED EMISSION OBJECT ROUTER AND OBJECT AUDIO ENCODER RECEIVER/ ENCODER DEFINITION DECODER PASSTHROUGH ANALYSIS PCM RENDERING AND PROCESSING INGEST PLAYOUT AUDIO SERVER SERVER MONITORING METADATA PCM MEZZANINE CONTRIBUTION AD STREAMING TRANSPORT FORMAT ENCODER MODULATOR/ SERVER ENCODER ENCODING FIBER MUX MUX/ SPLICER STREAMING ENCODER POSTPRODUCTION CDN ANTENNA CDN CONFIDENCE MONITOR OUTPUT OBJECT AUDIO PROCESSOR IN THE HOME SET-TOP BOX CHANNEL METADATA OBJECT AUDIO METADATA ANALYSIS GENERATION DEMODULATOR CHANNEL METADATA & OBJECT CHANNEL / ® GROUPING OBJECT AC-4 HDMI AND OBJECT AUDIO DECODER FORMATTER DEFINITION ANALYSIS PCM RENDERING AND PROCESSING TABLET/SMARTPHONE TV TO AVR / SOUNDBAR METADATA TO HEADPHONES TO SPEAKERS PCM ITU-R BWAV ADM (MXF, IMF) PACKAGING OBJECT APP AC-4 HEADPHONE RECEIVER / AC-4 HDMI® & CHANNEL DECODER RENDERER PROCESSOR DECODER FORMATTER INTERCHANGE TO AVR / SOUND BAR METADATA ED2 ENCODER PCM AC-4 IMMERSIVENESS Dolby AC-4 natively supports immersive audio to move sound around the audience in three-dimensional space. Both channel-based and object-based immersive audio can be delivered to the home and played back on speakers or headphones. -

Audio Coding for Digital Broadcasting

Recommendation ITU-R BS.1196-7 (01/2019) Audio coding for digital broadcasting BS Series Broadcasting service (sound) ii Rec. ITU-R BS.1196-7 Foreword The role of the Radiocommunication Sector is to ensure the rational, equitable, efficient and economical use of the radio- frequency spectrum by all radiocommunication services, including satellite services, and carry out studies without limit of frequency range on the basis of which Recommendations are adopted. The regulatory and policy functions of the Radiocommunication Sector are performed by World and Regional Radiocommunication Conferences and Radiocommunication Assemblies supported by Study Groups. Policy on Intellectual Property Right (IPR) ITU-R policy on IPR is described in the Common Patent Policy for ITU-T/ITU-R/ISO/IEC referenced in Resolution ITU-R 1. Forms to be used for the submission of patent statements and licensing declarations by patent holders are available from http://www.itu.int/ITU-R/go/patents/en where the Guidelines for Implementation of the Common Patent Policy for ITU-T/ITU-R/ISO/IEC and the ITU-R patent information database can also be found. Series of ITU-R Recommendations (Also available online at http://www.itu.int/publ/R-REC/en) Series Title BO Satellite delivery BR Recording for production, archival and play-out; film for television BS Broadcasting service (sound) BT Broadcasting service (television) F Fixed service M Mobile, radiodetermination, amateur and related satellite services P Radiowave propagation RA Radio astronomy RS Remote sensing systems S Fixed-satellite service SA Space applications and meteorology SF Frequency sharing and coordination between fixed-satellite and fixed service systems SM Spectrum management SNG Satellite news gathering TF Time signals and frequency standards emissions V Vocabulary and related subjects Note: This ITU-R Recommendation was approved in English under the procedure detailed in Resolution ITU-R 1. -

Surround Sound Processed by Opus Codec: a Perceptual Quality Assessment

28. Konferenz Elektronische Sprachsignalverarbeitung 2017, Saarbrücken SURROUND SOUND PROCESSED BY OPUS CODEC: APERCEPTUAL QUALITY ASSESSMENT Franziska Trojahn, Martin Meszaros, Michael Maruschke and Oliver Jokisch Hochschule für Telekommunikation Leipzig, Germany [email protected] Abstract: The article describes the first perceptual quality study of 5.1 surround sound that has been processed by the Opus codec standardised by the Internet Engineering Task Force (IETF). All listening sessions with up to five subjects took place in a slightly sound absorbing laboratory – simulating living room conditions. For the assessment we conducted a Degradation Category Rating (DCR) listening- opinion test according to ITU-T P.800 recommendation with stimuli for six channels at total bitrates between 96 kbit/s and 192 kbit/s as well as hidden references. A group of 27 naive listeners compared a total of 20 sound samples. The differences between uncompressed and degraded sound samples were rated on a five-point degradation category scale resulting in Degradation Mean Opinion Score (DMOS). The overall results show that the average quality correlates with the bitrates. The quality diverges for the individual test stimuli depending on the music characteristics. Under most circumstances, a bitrate of 128 kbit/s is sufficient to achieve acceptable quality. 1 Introduction Nowadays, a high number of different speech and audio codecs are implemented in several kinds of multimedia applications; including audio / video entertainment, broadcasting and gaming. In recent years the demand for low delay and high quality audio applications, such as remote real-time jamming and cloud gaming, has been increasing. Therefore, current research objectives do not only include close to natural speech or audio quality, but also the requirements of low bitrates and a minimum latency. -

Operating Instructions Blu-Ray Disc Home Theater Sound System SC

BT300.book 1 ページ 2009年6月12日 金曜日 午後12時13分 Operating Instructions Blu-ray Disc Home Theater Sound System Model No. SC-BT303 SC-BT300 SC-BT203 SC-BT200 The illustration shows the image of the unit SC-BT300 with “P” indicated on the packaging. Dear customer Thank you for purchasing this product. For optimum performance and safety, please read these instructions carefully. Before connecting, operating or adjusting this product, please read the instructions completely. Please keep this manual for future reference. To update the firmware of this unit, refer to page 32. Region management information BD-Video Example: This unit plays BD-Video marked with labels containing the region code A. DVD-Video Example: This unit plays DVD-Video marked with labels containing the region number “1” or “ALL”. 1 2 1 ALL 4 [For[the[U.S.A.[and[Canada[ ® If you have any questions contact As an ENERGY STAR Partner, [U.S.A.]and]Puerto]Rico]:1-800-211-PANA(7262) Panasonic has determined that [Canada]: 1-800-561-5505 this product meets the ENERGY STAR® guidelines for energy efficiency. [Only]for[U.S.A.]and]Puerto]Rico]: The warranty can be found on page 58. For Canada only: The word “Participant” is used in place of the word [Canada]: The warranty can be found on page 59. “Partner”. P PC PX RQT9508-1P 2009/7/08 BT300.book 2 ページ 2009年6月12日 金曜日 午後12時13分 ≥These operating instructions are applicable System SC-BT300 SC-BT303 SC-BT200 SC-BT203 to models SC-BT300, SC-BT303, SC-BT200 Main unit SA-BT300 SA-BT300 SA-BT200 SA-BT203 Getting started and SC-BT203 for a variety of regions. -

Configure Surround Sound on an Intel NUC Or Comptue Stick

Surround Sound Setup Guide for NUC This guide will show the recommend method to setup surround sound through bitstreaming. Bitstreaming is the process whereby the NUC sends an un-encoded digital signal to an A/V receiver, to which the receiver will decode the signal, not the NUC, and often produces better quality sound, depending on the receiver. What is Needed: AV Receiver with HDMI or TOSLINK (SPDIF), if using optical audio Surround speakers (5.1 or 7.1) 2 HDMI cables or a TOSLINK cable (a mini DisplayPort to HDMI cable can also be used from the NUC to the Receiver) HDMI display, keyboard, mouse NUC running Windows* Media Player Classic* (https://mpc-hc.org/) 1. Download and install the latest Intel® graphics drivers (https://downloadcenter.intel.com/) 2. Connect the HDMI or mini DisplayPort cable from the NUC to an HDMI input of the AV receiver. If using TOSLINK on the NUC, connect the NUC’s TOSLINK output to a TOSLINK input on the receiver. 3. Start Windows* and download and install Media Player Classic* (MPC-HC) (http://mpc-hc.org/downloads/) 4. Open MPC-HC. On the Menu bar, click View, then Options. 5. On the left side menu tree, click on Internal Filters, then click on Video Decoder (on the bottom of the screen). 6. It’s suggested that Hardware Acceleration be used, especially if 4K content is played, choose a Hardware Acceleration option, then click OK. 7. If 4K or HEVC (h.265) content is going to be played, also select, HEVC, and UHD (4K). -

Model DV6500 User Guide Super Audio CD / DVD Player

E59M5UD.qx3 04.7.16 7:50 PM Page 1 Model DV6500 User Guide Super Audio CD / DVD Player CLASS 1 LASER PRODUCT E59M5UD.qx3 04.7.16 7:50 PM Page 2 TO REDUCE THE RISK OF FIRE OR ELECTRIC SHOCK, WARNING DO NOT EXPOSE THIS PRODUCT TO RAIN OR MOISTURE. The lightning flash with arrowhead symbol within an equilateral triangle is intended to alert the user to the CAUTION presence of uninsulated “dangerous voltage” within the RISK OF ELECTRIC SHOCK product’s enclosure that may be of sufficient magnitude DO NOT OPEN to constitute a risk of electric shock to persons. CAUTION: The exclamation point within an equilateral triangle is TO REDUCE THE RISK OF ELECTRIC SHOCK, DO NOT REMOVE intended to alert the user to the presence of important COVER (OR BACK). NO USER-SERVICEABLE PARTS INSIDE. operating and maintenance (servicing) instructions in the REFER SERVICING TO QUALIFIED SERVICE PERSONNEL. literature accompanying the product. CAUTION: TO PREVENT ELECTRIC SHOCK, MATCH WIDE BLADE OF PLUG TO WIDE SLOT, FULLY INSERT. ATTENTION: POUR ÉVITER LES CHOC ÉLECTRIQUES, INTRODUIRE LA LAME LA PLUS LARGE DE LA FICHE DANS LA BORNE CORRESPONDANTE DE LA PRISE ET POUSSER JUSQU’AU FOND. NOTE: Operating Environment This equipment has been tested and found to comply with the limits Operating environment temperature and humidity: for a Class B digital device, pursuant to Part 15 of the FCC Rules. +5 C to +35 C (+41 F to +95 F); less than 85%RH (cooling vents not These limits are designed to provide reasonable protection against blocked) Do not install in the following locations harmful interference in a residential installation. -

Introduction to DVD Carol Cini, U.S

Proceedings of the 8th Annual Federal Depository Library Conference April 12 - 15, 1999 Introduction to DVD Carol Cini, U.S. Government Printing Office Washington, DC DVD started out standing for Digital Video Disc, then Digital Versatile Disc, and now it’s just plain old DVD. It is essentially a bigger and faster CD that is being promoted for entertainment purposes (movies) and some computer applications. It will eventually replace audio CDs, VHS and Beta tapes, laserdiscs, CD-ROMs, and video game cartridges as more hardware and software manufacturers support this new technology. DVDs and CDs look alike. A CD is a single solid injected molded piece of carbonate plastic that has a layer of metal to reflect data to a laser reader and coat of clear laminate for protection. DVD is the same size as a CD but consists of two solid injected molded pieces of plastic bonded together. Like CDs, DVDs have a metalized layer (requires special metalization process) and are coated with clear laminate. Unlike CD's, DVD's can have two layers per side and have 4 times as many "pits" and "lands" as a CD. There are various types of DVD, including DVD-ROM, DVD-Video, DVD-Audio, DVD-R, and DVD-RAM. The specifications for these DVD's are as follows: for prerecorded DVD's; Book A - DVD-ROM, Book B - DVD-Video, and Book C- DVD-Audio. For recordable DVD's, there is Book D - DVD-R, Book E - DVD-RAM. The official DVD specification books are available from Toshiba after signing a nondisclosure agreement and paying a $5,000 fee. -

Ultra High Definition 4K Television User's Guide

Ultra High Definition 4K Television User’s Guide: 65L9400U 58L8400U If you need assistance: Toshiba's Support Web site support.toshiba.com For more information, see “Troubleshooting” on page 173 in this guide. Owner's Record The model number and serial number are on the back and side of your television. Print out this page and write these numbers in the spaces below. Refer to these numbers whenever you communicate with your Toshiba dealer about this Television. Model name: Serial number: Register your Toshiba Television at register.toshiba.com Note: To display a High Definition picture, the TV must be receiving a High Definition signal (such as an over- the-air High Definition TV broadcast, a High Definition digital cable program, or a High Definition digital satellite program). For details, contact your TV antenna installer, cable provider, or GMA300039012 satellite provider. 12/14 2 CHILD SAFETY: PROPER TELEVISION PLACEMENT MATTERS TOSHIBA CARES • Manufacturers, retailers and the rest of the consumer electronics industry are committed to making home entertainment safe and enjoyable. • As you enjoy your television, please note that all televisions – new and old – must be supported on proper stands or installed according to the manufacturer’s recommendations. Televisions that are inappropriately situated on dressers, bookcases, shelves, desks, speakers, chests, carts, etc., may fall over, resulting in injury. TUNE IN TO SAFETY • ALWAYS follow the manufacturer’s recommendations for the safe installation of your television. • ALWAYS read and follow all instructions for proper use of your television. • NEVER allow children to climb on or play on the television or the furniture on which the television is placed. -

Technology of ISDB-TSB2 ISDB-T Seminar(18Th March

ISDB-T seminar(18th March. 2009) STRL PresentationPresentation 55--22 TechnologyTechnology ofof ISDBISDB--TTSBSB -- DigitalDigital RadioRadio SystemSystem -- 18th March. 2009 KBP ISDB-T seminar Manila, Philippines DiBEG JAPAN Kazunori Yokohata (NHK Science & Technical Research Lab) Digital broadcasting experts group ISDB-T seminar(18th March. 2009) STRL ISDB-TSB system ISDB-TSB Integrated Services Digital Broadcasting for Terrestrial Sound Broadcasting z System for terrestrial digital sound broadcasting (in VHF / UHF). z Intended for vehicular, portable and fixed reception. z Recommended as System F of Recommendation ITU-R BS.1114-6. z Commonality with ISDB-T of the DTTB system (also recommended as System C of Recommendation ITU-R BT.1306-3 System C). Digital broadcasting experts group Technology of ISDB-TSB2 ISDB-T seminar(18th March. 2009) STRL Requirements for ISDB-TSB Mobile and handheld reception z Car audio z Cell phone, PDA, PC High quality audio z Equivalent to CD z Multi-channel audio (5.1 surround, multilingual, etc.) Multimedia services z Data services z Information related to current program z Independent information (latest news, weather forecast, traffic information, etc.) z Electronic program guide Saving frequency resources z Limited channels for digital radio z Reduction of guard bands between adjacent ISDB-TSB channel z Simple assignment of channels for ISDB-TSB Digital broadcasting experts group Technology of ISDB-TSB3 ISDB-T seminar(18th March. 2009) STRL Technologies to realize requirements for ISDB-TSB Mobile and portable reception z OFDM modulation scheme High quality audio z MPEG-2 AAC (advanced audio coding) MPEG-2 AAC+SBR (spectral band replication) Multimedia services z MPEG-2 Systems (MPEG-2 TS) Video services z MPEG-4 H.264 AVC Saving frequency resources z BST (band-segmented transmission) -OFDM z Connected transmission and SFN (single frequency network) Digital broadcasting experts group Technology of ISDB-TSB4 ISDB-T seminar(18th March. -

Dolby Broadcast Technologies Overview

Dolby® Broadcast Technologies: Essential for Evolving Entertainment Broadcast delivery requirements are in transition, and television transmission is no longer limited to signals sent to TV sets and home theater systems. Consumers now watch their favorite programs and movies on multiple devices: on PCs via the Internet, or by using cell phones, portable media players, and more. Dolby’s portfolio of technologies is evolving right alongside today’s new broadcast landscape. Dolby® broadcast technologies work together as a seamless, integrated solution—they are involved at every stage, from content creation all the way to consumers. Dolby helps content providers deliver a great entertainment experience, regardless of how viewers access programming: in their home theaters; via new Internet-capable media devices such as Vudu and Apple TV®; or on the many video-enhanced mobile devices on the market. All Dolby broadcast technologies support a path for metadata, ensuring that consumers hear programming the way it was intended. Plus, each technology is designed to address unique requirements for different parts of the broadcast chain, while still efficiently taking advantage of similarities when possible. The Technologies Dolby E is our digital audio technology optimized for the distribution of multichannel audio through digital two- channel postproduction and broadcasting infrastructures. Dolby E is the ideal format for professional contribution and distribution through networks regardless of the technology used for final delivery to consumers. Dolby Digital is a worldwide standard in film, broadcast, and packaged media. It is used virtually worldwide for broadcast services with 5.1-channel audio and can be found in DVD, terrestrial DTV, digital cable, and direct broadcast satellite. -

T 765 AV Surround Sound Receiver

T 765 AV Surround Sound Receiver > POSITIONING The NAD T 765 now comes with full High Definition decoding thanks to NAD’s innovative approach to upgrading your AV tuner preamplifier – Modular Design Construction (MDC). The NAD T 765 is heir to many generations of award-winning NAD designs. This exceptional pedigree is evident in both the look and the feel of the T 765, and it is unmistakable the moment you listen. It is NAD’s insistence on creating products with remarkable sound quality at sensible prices that has made NAD the first choice among the most knowledgeable listeners from around the world. > NAD’sF E A‘Music T U First’ R E philosophy S dictates that we endow our Audio Video products with the same warm, involving sound quality that makes music listening so rewarding with our stereo components. This stands in stark contrast to our competitors who view Audio Video components primarily from a ‘content’ point-of-view, with sound quality far down the list of priorities. Yet the T 765 is second to none in terms of flexibility and up-to- the-minute digital technology. > F E A T U R E S • 140W x 7 (FTC) Power • 5 A/V Custom Presets store unique • Analogue video to HDMI Conversion • 7 x 80W Minimum Continuous Power speaker level and tone control settings • 3 Analogue Audio outputs including Zone 2 into 4/8 ohms, all channels driven • Direct access speaker level adjustment Audio Out and with the 2 other Audio simultaneously, 20Hz – 20kHz at for surround, centre and subwoofer outputs assignable also as Zone 3 and 0.05%THD (NAD Full Disclosure