ON Semiconductor Is Depicted in Figure 29

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Thyristors.Pdf

THYRISTORS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Thyristors Thyristors are a class of semiconductor devices characterized by 4-layers of alternating p and n material. Four-layer devices act as either open or closed switches; for this reason, they are most frequently used in control applications. Some thyristors and their symbols are (a) 4-layer diode (b) SCR (c) Diac (d) Triac (e) SCS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The 4-layer diode (or Shockley diode) is a type of thyristor that acts something like an ordinary diode but conducts in the forward direction only after a certain anode to cathode voltage called the forward-breakover voltage is reached. The basic construction of a 4-layer diode and its schematic symbol are shown The 4-layer diode has two leads, labeled the anode (A) and the Anode (A) A cathode (K). p 1 n The symbol reminds you that it acts 2 p like a diode. It does not conduct 3 when it is reverse-biased. n Cathode (K) K Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The concept of 4-layer devices is usually shown as an equivalent circuit of a pnp and an npn transistor. Ideally, these devices would not conduct, but when forward biased, if there is sufficient leakage current in the upper pnp device, it can act as base current to the lower npn device causing it to conduct and bringing both transistors into saturation. -

Electronic Devices & Circuits

COURSE MATERIAL ELECTRONIC DEVICES & CIRCUITS (15A04301) LECTURE NOTES B.TECH (II - YEAR & I - SEM) Prepared by: Ms. J.V. Pesha, Assistant Professor Department of Electronics and Communication Engineering VEMU INSTITUTE OF TECHNOLOGY (Approved By AICTE, New Delhi and Affiliated to JNTUA, Ananthapuramu) Accredited By NAAC & ISO: 9001-2015 Certified Institution Near Pakala, P. Kothakota, Chittoor- Tirupathi Highway Chittoor, Andhra Pradesh - 517 112 Web Site: www.vemu.org COURSE MATERIAL JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY ANANTAPUR II B.Tech I-Sem (E.C.E) T Tu C 3 1 3 (15A04301) ELECTRONIC DEVICES AND CIRCUITS Course Outcome: C212_1: Explain the characteristics and applications of the diode and special purpose electronic Devices. C212_2: Analyze various rectifiers and filters for the construction of a regulated power supply. C212_3: Demonstrate the construction, Working and Characteristics of BJT, JFET, and MOSFET in various modes and Compensation of a BJT. C212_4: Design and Analyze DC bias Circuitry of BJT and FET. C212_5: Analysis of Small Signal Model for BJT and FET amplifier. UNIT- I: Junction Diode Characteristics : Open circuited P-N junction, Biased P-N Junction, P-N Junction diode, Current Components in PN junction Diode, Diode Equation, V-I Characteristics, Temperature dependence on V-I characteristics, Diode resistance, Diode Capacitance, Energy band diagram of P-N junction Diode. Special Semiconductor Diodes: Zener Diode, Breakdown Mechanisms, Zener Diode applications, LED, LCD, Photo Diode, Varactor Diode, Tunnel Diode, -

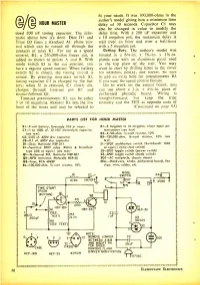

Sized 200 Uf Timing Capacitor. the Sche- Delay Time

fit your needs. It was 100,000 -ohms in the author's model giving him a minimum time HOUR MASTER delay of 30 seconds. Capacitor Cl may also be changed in value to modify the sized 200 uF timing capacitor. The sche- delay time. With a 200 uF capacitor and matic shows how it's done. Diac D1 and a 10 megohm pot, the maximum delay is Triac Q3 form a standard AC phase con- well over an hour and over a half -hour trol which can be turned off through the with a 5 megohm pot. contacts of relay K1. For use as a speed Getting Busy. The author's model was control, R4, a 250,000 -ohm linear pot, is housed in a 61/4 -in. x 33ús -in. x 17A3 -in. added as shown to points A and B. With plastic case with an aluminum panel used mode switch S3 in the out position. you as the top plate of the unit. You may have a regular speed control. When battery want to start by drilling holes in the cover switch S2 is closed, the timing circuit is for switches, pot(s), and socket. Be sure t armed. By pressing time -start switch S1, to add an extra hole for potentiometer R4 timing capacitor Cl is charged by the bat- if you want the speed control feature. tery; when Si is released, Cl slowly dis- Go to work on the circuit board; you charges through time -set pot R1 and can use about a 2 -in. x 41/2 -in. -

Power-Devices.Pdf

Power Devices Outline 1.1 Need for semiconductor power devices, 1.2 Power MOSFET (Qualitative) 1.3 Introduction to family of thyristors. 1.4 Silicon Controlled Rectifier (SCR)- structure, I-Vcharacteristics, Turn-On and Turn-Off characteristics, ratings 1.5 Gate-triggering circuits. 1.6 Diac and Triac- Basic structure, working and V-I characteristics. 1.7 Application of Diac as a triggering device for Triac. 1.1 Need for semiconductor power devices 1) The concept and features Power electronic devices: are the electronic devices that can be directly used in the power processing circuits to convert or control electric power. Vacuum devices: Mercury arc rectifier thyratron, etc. seldom In broad sense in use today Power electronic devices Semiconductor devices: major power electronic devices Very often: Power electronic devices= Power semiconductor devices Major material used in power semiconductor devices——Silicon Features of power electronic devices a) The electric power that power electronic device deals with is usually much larger than that the information electronic device does. b) Usually working in switching states to reduce power losses On-state Voltage across the device is 0 p=vi=0 V=0 Off-state Current through the device is 0 p=vi=0 i=0 c)Need to be controlled by information electronic circuits. d)Very often, drive circuits are necessary to interface between information circuits and power circuits. e)Dissipated power loss usually larger than information electronic devices —special packaging and heat sink are necessary. 2) Configuration of systems using power electronic devices Power electronic system: Electric isolation: optical, magnetic Control circuit (in a broad sense) detection circuit Power circuit (power Control stage, main circuit) circuit drive circuit Protection circuit is alsocircuit very often used in power electronic system especially for the expensive power semiconductors. -

Soft Start Circuit for Tetrode Filament Using TRIAC

Published by : International Journal of Engineering Research & Technology (IJERT) http://www.ijert.org ISSN: 2278-0181 Vol. 7 Issue 03, March-2018 Soft Start Circuit for Tetrode Filament using TRIAC Shyam Mohan V Senior Research Fellow- DRDO, Bangalore Abstract - This paper presents the creation of a soft start circuit filament. Tetrode is a vacuum tube it has a Heater for that operates based on the current regulating property of Electron emission, its supply voltage has to be TRIAC. TRIAC act as barrier in AC circuit preventing the current flow before being triggered. Supply voltage to the increased step by step from low value to its rated value heater filament need to be increased step by step to rated value. for safety and long life of vacuum tube. In this By changing the firing angle (180-0) of triac, the voltage topology power flow is regulated to the Heater applied to the Heater filament can be varied. Using a zero Filament by applying a AC supply voltage crossing detector and mono-stable multi-vibrator circuit the intermittently across the load during each half cycle. firing angle is changed. Trigger pulse is given to the Triac using a photo-diac. The TRIAC is set into a conducting state At starting only 20% of the input sine wave is applied and current flows through the Heater Filament soon after the across the LOAD. Step by step as the Resistance of RC trigger voltage is applied to the photodiac. The amount of circuit decreases, the RC time constant of Mono-stable voltage seen over the Heater Filament is determined by the multi-vibrator decreases, thus pulse width of output firing angle of the triac which is fixed by RC time constant of the monostable circuit. -

Comprehensive Careerprogram

Comprehensive CareerProgram Educational Training Equipment for the 21st Century Bulletin 285D Purpose The Hampden Comprehensive Career Program is designed to provide students planning careers in electronics with a solid foundation in the prac- tical applications of electrical and electronic cir- cuits and devices. Topics include everything from Ohm’s law, motors, and vacuum tubes through latest state-of-the-art devices such as MOSFETs, digital logic gates and operational amplifiers. A total of 189 topics are contained in five exper- H-CCP-B: Basic Program Topics H-CCP-C: Fundamental Consumer iment manuals, providing maximum flexibility in 1. Introduction to Laboratory Experimentation Program Topics establishing the electronic curriculum to meet a 2. Techniques of Preparing Laboratory Reports 1. Triggered Oscilloscope / AF Generator variety of career objectives. The hardware con- 3. Switching Devices and Circuits 2. Oscilloscope Voltage Measurements 4. Measuring Electrical Phenomena 3. Lissajous Patterns sists of discrete components integrated circuits, 5. Solid State Volt-Ohm-Milliammeter 4. Inductance and Inductance Reactance and printed circuit boards, utilizing Velcro work 6. Creation of Electrical Energy 5. Measuring Phase Angle by Lissajous surfaces and snap connectors. 7. Practical Uses of Electricity 6. Transformers 8. Voltage, Current, Resistance - Ohm's Law 7. Capacitors and Capacitance Description 9. Series Circuits 8. RC time Constants 10. Parallel Circuits 9. Capacitive Reactance The Hampden Comprehensive Career Program 11. Series- Parallel Circuits 10. Phase Shift Caused by Capacitance consists of five segments which may be 12. Kirchhoff’s Voltage Law 11. Capacitances in Series and Parallel sequenced in a dozen different ways to produce 13 Kirchhoff’s Voltage Law - Two Sources 12. -

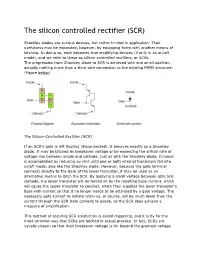

The Silicon Controlled Rectifier (SCR)

The silicon controlled rectifier (SCR) Shockley diodes are curious devices, but rather limited in application. Their usefulness may be expanded, however, by equipping them with another means of latching. In doing so, each becomes true amplifying devices (if only in an on/off mode), and we refer to these as silicon-controlled rectifiers, or SCRs. The progression from Shockley diode to SCR is achieved with one small addition, actually nothing more than a third wire connection to the existing PNPN structure: (Figure below) The Silicon-Controlled Rectifier (SCR) If an SCR's gate is left floating (disconnected), it behaves exactly as a Shockley diode. It may be latched by breakover voltage or by exceeding the critical rate of voltage rise between anode and cathode, just as with the Shockley diode. Dropout is accomplished by reducing current until one or both internal transistors fall into cutoff mode, also like the Shockley diode. However, because the gate terminal connects directly to the base of the lower transistor, it may be used as an alternative means to latch the SCR. By applying a small voltage between gate and cathode, the lower transistor will be forced on by the resulting base current, which will cause the upper transistor to conduct, which then supplies the lower transistor's base with current so that it no longer needs to be activated by a gate voltage. The necessary gate current to initiate latch-up, of course, will be much lower than the current through the SCR from cathode to anode, so the SCR does achieve a measure of amplification. -

Silicon-Controlled Rectifiers

Component Theory SCRs 1 Silicon-Controlled Rectifiers Our exploration of thyristors begins with a device called the four-layer diode, also known as a PNPN diode, or a Shockley diode after its inventor, William Shockley. This is not to be confused with a Schottky diode, that two-layer metal-semiconductor device known for its high switching speed. A crude illustration of the Shockley diode, often seen in textbooks, is a four-layer sandwich of P-N-P-N semiconductor material. 2 Silicon-Controlled Rectifiers Shockley or 4-layer diode Transistor equivalent of Shockley diode 3 Silicon-Controlled Rectifiers A silicon-controlled rectifier (or semiconductor- controlled rectifier) is a four-layer solid state device that controls current. The name "silicon controlled rectifier" or SCR is General Electric's trade name for a type of thyristor. The SCR was developed by a team of power engineers led by Gordon Hall and commercialized by Frank W. "Bill" Gutzwiller in 1957. 4 Silicon-Controlled Rectifiers Construction of SCR An SCR consists of four layers of alternating P and N type semiconductor materials. Silicon is used as the intrinsic semiconductor, to which the proper dopants are added. The junctions are either diffused or alloyed. The planar construction is used for low power SCRs (and all the junctions are diffused). The mesa type construction is used for high power SCRs. In this case, junction J2 is obtained by the diffusion method and then the outer two layers are alloyed to it, since the PNPN pellet is required to handle large currents. 5 Silicon-Controlled Rectifiers It is properly braced with tungsten plates to provide greater mechanical strength. -

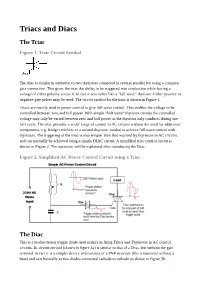

Triacs and Diacs the Triac

Triacs and Diacs The Triac Figure 1. Triac Circuit Symbol The triac is similar in operation to two thyristors connected in reverse parallel but using a common gate connection. This gives the triac the ability to be triggered into conduction while having a voltage of either polarity across it. In fact it acts rather like a "full wave" thyristor. Either positive or negative gate pulses may be used. The circuit symbol for the triac is shown in Figure 1. Triacs are mainly used in power control to give full wave control. This enables the voltage to be controlled between zero and full power. With simple "half wave" thyristor circuits the controlled voltage may only be varied between zero and half power as the thyristor only conducts during one half cycle. The triac provides a wider range of control in AC circuits without the need for additional components, e.g. bridge rectifiers or a second thyristor, needed to achieve full wave control with thyristors. The triggering of the triac is also simpler than that required by thyristors in AC circuits, and can normally be achieved using a simple DIAC circuit. A simplified triac control circuit is shown in Figure 2. The operation will be explained after introducing the Diac. Figure 2. Simplified AC Power Control Circuit using a Triac The Diac This is a bi-directional trigger diode used mainly in firing Triacs and Thyristors in AC control circuits. Its circuit symbol (shown in figure 3a) is similar to that of a Triac, but without the gate terminal, in fact it is a simpler device and consists of a PNP structure (like a transistor without a base) and acts basically as two diodes connected cathode to cathode as shown in figure 3b. -

Power Electronics

UNIVERSITY OF BABYLON FACULTY OF ENGINEERING DEPT. OF ELECTRICAL ENGINEERING FOURTH YEAR ACADEMIC YEAR 2012-2013 POWER ELECTRONICS Dr. Mahmoud Shaker Al-Shemmary Associate Prof. PowerU electronics is the technology to convert and control electric power from one form to another using electronic power Devices. CHAPTERU ONE : INTRODUCTION 1.U What is the power electronics. Applications of solid-state electronics in the electrical power field are steadily increasing; the term power electronics has been used since 1960s, after the introduction of the silicon controlled rectifier (SCR) by general electric. Power electronics has shows rapid growth in recent years with the development of power semiconductor devices that can switch large current efficiently at high voltages. Since these devices offer high reliability and small size. The scope of applications of power electronic systems as regulating power supply, variable speed of AC and DC machines, high voltage DC transmission lines, frequency changer and load matching in solar system. The broad field of electrical engineering can be divided into three major areas, namely, electric power, electronic, and control. Power electronics deal the application of power semiconductor devices, such as thyristors and transistors, for the conversion and control of electrical energy at high power levels. This conversion is usually from AC to DC or vice versa, while the parameters controlled are voltage, current, or frequency. For example, a DC/DC converter has constant input and performs an output of variable voltage and current. The process of power conversion or control is realized by controlling the adequate operation of power switches devices. The control signals necessary are generated by electronic or digital means, so the power flow is controlled by electronic means. -

Introductory POWER Electronics

Introductory Electronics ¢¡ £¥¤ ¦ POWER §©¨ ¨ Features of Power Electronic System 1.Function and Form Energy Processing : altering the character of electrical energy Interfacing : imposing relationship of voltages and currents at one port to the other : Interacting with the external systems: bidirectional energy flow external determines the internal function Form : generically referred as converters, power processors (ac/dc, ac/dc, dc/dc) 2.Components Switches : power diode (PN; Shottkey), power transistor (BJT; MOSFET) , thyristor (SCR; TRIAC; MCT; GTO) Energy Storage Elements : capacitor, inductor 3.Dynamics and Control ¢¡ £¥¤ ¦ §©¨ ¨ http://www.nobel.se/physics/educational/transistor/function/index.html Power Diode 1 • Bipolar PN Junction ¢¡ £¥¤ ¦ §©¨ ¨ Power Diode 2 • Shottky Diode Advantages: 1. Short Reverse Recovery Time --- High speed rectifier 2. Low Voltage Drop in Forward Bias --- High speed TTL IC 74S00 (ECL) --- Low power TTL IC 74LS00 (TTL) Reason for fast speed: CHARGE STORAGE in PN diode due To slow holes to get homes No P-materials reduces charge storage ¢¡ £¥¤ ¦ §©¨ ¨ Power Diode 3 • Diode Bridge • Tunnel Diode Heavily doped, negative resistance over forward bias range, so nice for high frequency oscillator • Varicap Diode PN junction cap decreases when reverse biasing voltage increases For variable cap to eliminate the need of moving part 60pF/0v 6pF/20v • Zener Diode narrow junction, Zener breakdown, large change of current causes no change of voltage, voltage regulator • LED -

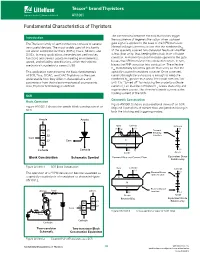

Fundamental Characteristics of Thyristors Application Note

Teccor® brand Thyristors AN1001 Fundamental Characteristics of Thyristors The connections between the two transistors trigger Introduction the occurrence of regenerative action when a proper The Thyristor family of semiconductors consists of several gate signal is applied to the base of the NPN transistor. very useful devices. The most widely used of this family Normal leakage current is so low that the combined hFE are silicon controlled rectifiers (SCRs), Triacs, SIDACs, and of the specially coupled two-transistor feedback amplifier DIACs. In many applications these devices perform key is less than unity, thus keeping the circuit in an off-state functions and are real assets in meeting environmental, condition. A momentary positive pulse applied to the gate speed, and reliability specifications which their electro- biases the NPN transistor into conduction which, in turn, mechanical counterparts cannot fulfill. biases the PNP transistor into conduction. The effective hFE momentarily becomes greater than unity so that the This application note presents the basic fundamentals specially coupled transistors saturate. Once saturated, of SCR, Triac, SIDAC, and DIAC Thyristors so the user current through the transistors is enough to keep the understands how they differ in characteristics and combined hFE greater than unity. The circuit remains “on” parameters from their electro-mechanical counterparts. until it is “turned off” by reducing the anode-to-cathode Also, Thyristor terminology is defined. current (IT) so that the combined hFE is less than unity and regeneration ceases. This threshold anode current is the holding current of the SCR. SCR Geometric Construction Basic Operation Figure AN1001.3 shows cross-sectional views of an SCR Figure AN1001.1 shows the simple block construction of an chip and illustrations of current flow and junction biasing in SCR.