Software Break- Size of the Quantization Noise (I.E., L/2 an LSB of the Point, Single Step Trace, Disassembler, and RS-232 Quantizer)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Extracting and Mapping Industry 4.0 Technologies Using Wikipedia

Computers in Industry 100 (2018) 244–257 Contents lists available at ScienceDirect Computers in Industry journal homepage: www.elsevier.com/locate/compind Extracting and mapping industry 4.0 technologies using wikipedia T ⁎ Filippo Chiarelloa, , Leonello Trivellib, Andrea Bonaccorsia, Gualtiero Fantonic a Department of Energy, Systems, Territory and Construction Engineering, University of Pisa, Largo Lucio Lazzarino, 2, 56126 Pisa, Italy b Department of Economics and Management, University of Pisa, Via Cosimo Ridolfi, 10, 56124 Pisa, Italy c Department of Mechanical, Nuclear and Production Engineering, University of Pisa, Largo Lucio Lazzarino, 2, 56126 Pisa, Italy ARTICLE INFO ABSTRACT Keywords: The explosion of the interest in the industry 4.0 generated a hype on both academia and business: the former is Industry 4.0 attracted for the opportunities given by the emergence of such a new field, the latter is pulled by incentives and Digital industry national investment plans. The Industry 4.0 technological field is not new but it is highly heterogeneous (actually Industrial IoT it is the aggregation point of more than 30 different fields of the technology). For this reason, many stakeholders Big data feel uncomfortable since they do not master the whole set of technologies, they manifested a lack of knowledge Digital currency and problems of communication with other domains. Programming languages Computing Actually such problem is twofold, on one side a common vocabulary that helps domain experts to have a Embedded systems mutual understanding is missing Riel et al. [1], on the other side, an overall standardization effort would be IoT beneficial to integrate existing terminologies in a reference architecture for the Industry 4.0 paradigm Smit et al. -

Japanese Semiconductor Industry Service

Japanese Semiconductor Industry Service Volume II Technology & Government Dataquest nn a company of The Dun & Bradstreet Corporation 1290 Ridder Park Drive San Jose, California 95131-2398 (408) 437-8000 Telex: 171973 Fax: (408) 437-0292 Sales/Service offices: UNITED KINGDOM GERMANY Dataquest UK Limited Dataquest GmbH 13th Floor, Centrepoint Rosenkavalierplatz 17 103 New Oxford Street D-8000 Munich 81 London WCIA IDD West Germany England (089)91 10 64 01-379-6257 Telex: 5218070 Telex: 266195 Fax: (089)91 21 89 Fax: 01-240-3653 FRANCE JAPAN Dataquest SARL Dataquest Japan, Ltd. 100, avenue Charles de Gaulle Taiyo Ginza Building/2nd Floor 92200 Neuilly-sur-Seine 7-14-16 Ginza, Chuo-ku France Tokyo 104 Japan (01)4738.13.12 (03)546-3191 Telex: 611982 Telex: 32768 Fax: (01)4738.11.23 Fax: (03)546-3198 The content of this report represents our interpretation and analysis of information generally available to the public or released by responsible individuals in the subject com panies, but is not guaranteed as to accuracy or completeness. It does not contain material provided to us in confidence by our clients. This information is not furnished in connection with a sale or offer to sell securities, or in connection with the solicitation of an offer to buy securities. This firm and its par ent and/or their officers, stockholders, or members of their families may, from time to time, have a long or short position in the securities mentioned and may sell or buy such securities. Printed in the United States of America. All rights reserved. -

Circuit-Cellar-018.Pdf

1 EDITOR’S I’ve Seen the Future INK Curtis Franklin, Jr. 1 I recently led a panel discussion at the Embedded Systems 32-BIT PROCESSORS Programming Conference. I met interesting people, arranged for a few articles, and ran into lots of folks who were carrying crystal There weren’t many people talking about 8-bit processors at balls in their fanny packs. I thought you might like to know what the show. Intel mentioned the 8051, saying that they have now they say you’re going to be doing in the next few years... shipped over 100,000,000 of them, but that came as a passing statement at their press conference announcing the latest mem- OPERATING SYSTEMS bers of the 80960 family. Motorola was ready and willing to talk about 68030 and 88000 applications, National was discussing the You’re going to be using an operating system. I’m not talking 32000, and everyone was announcing the arrival of the 32-bit about the operating system on your desktop computer, but the future. Once in a while I heard talk about 16-bit chips like the complete multitasking operating system that you’ll be building 80186 and 8096, but there was a noticeable absence of discussion into each and every control project. Depending on who you talk on anything having to do with 8-bit applications. to, you’ll be using an MS-DOS variant, a UNIX variant, or a All of the predictions I’ve talked about are fine and probably specialized embedded 0s for your development. -

21 198511 Computer Journal

188N'07a.Wl THE COMPUTER JOURNAL~ For Those Who Interface, Build, and Apply Micros Issue Number 21 November-December, 1985 $2.50U5 Extending Turbo Pascal Customize With Procedures and Functions pilge2 Unsoldering: The Arcane Art Second in a Series pilge8 Analog Data Acquisition and Control Connecting Your Computer to the Real World page19 Build the Circuit Designer 1 MPB Part 2: Programming the SHC pagelS • The Computer Corner page 52 The Computer Journal! Issue #21 1 THE COMPUTER JOURNAL 190 Sullivan Crossroad Editor's Page Columbia Falls, Montana 59912 406-257-9119 Mid-Level Languages Being Developed about languages have been voiced by When the first hobbyists built their others several times during the past Editor/Publisher microcomputers they had to code their two months. Art Car/son programs directly in machine language. Assembly is a great programming but they soon wrote assemblers which language and the small ROMabie Production Assistant enabled them to use easier to remem programs run fast - but coding can be Judie Overbeek ber mnemonics for their source code. tedious for large programs, and I/O. Circulation Language development continued and screen-handling, menus and floating point math routines can be a real bitch Donna Carlson BASIC became the familiar language for the new micro owner. Today there to code. Developing a non-trivial Technical Editor is an almost overwhelming assortment assembly language program is awk Lance Rose of languages to choose from with ward because you haveto write the something for every purpose, and it souce code with an editor (I use Wor Contributing Editor seems that there should be no reason to dStar), assemble to a HEX file, and load Ernie Brooner work on language development- but that to a .COM file for a trial run. -

View of J1 Should Be Used to Properly Connect the Computer to Your Power Supply

TEC~N~CA~MANUAL REV 1.0 Micrhmint;lnc I15 Timberlachen Cirde, Sub 2001, Lake Mary, FL 32746 Phone 407-262- Fax 407-2620069 www.micromint.com .. ............................. COPYRIGHT f********x************n********* * * * RTC180, RTC52, BCC180, BASIC-180, and BCC bus rt * are trademarks of Micromint, Inc. .& * * * This manual is copyright (c) 1990 * * by Micromint, Inc. * * * * All Rights Reserved * * * * * f*Q**t*****f******X****k****** DISCUIMER ***********+**********ff******** * * * While we have attempted to provide accurate and up-to- * * date information in this manual, Micromint Inc. makes no * * representations or warranties respecting its contents. We reserve * * the right to make periodic changes to the text and to issue new * * editions of this manual without notification. t * * A occasionally in this manual we refer to other manufacturers' * * products. Such references do not constitute an endorsement of * * these products, but are included for the purpose of illustration * * or clarification. We do not intend such technical information and * * interface data to supersede information provided by individual * * manufacturers. * * * * * ...................................................................... Conditions of sale and Product Warranty Micromint Inc. and the Buyer agree to the following terms and conditions of Sale and Purchase: 1. Micromint Inc. extends the following warranty: a factory- manufactured circuit board or assembly carries with it a one-year warranty covering both parts and labor. Any unit which is found to have a defect in materials or workmanship will, at the discre- tion of ~icromintInc., be repaired or replaced. 2. A minimum inspection fee must be prepaid for the repair of units that are no longer under warranty. Call Micromint Inc. for a current list of fees. -

Software a Lications Swimming in the Relational Lake

r $3.95 April-May 1987 Software A lications Swimming In The Relational Lake . .................... 14 Designing relational databases. Expert System. ................... ............ ... .... 22 Gary designs an expert system with Prolog. Nasty Software ................................. .. .. .. 82 A plague of new programs in the public domain. Hardware Applications - Controlling The Real World ............................. 6 Build an 8-channel temperature scanner. The Bleeping PC ......................... .... ... ... 30 Stra nge noises fro m clonal counters. Who's Making Great Hard Drives ...................... 44 Read before you purchase your next hard drive. Changing the Picture ............................~ ...... 86 Super graphics from a new graphics processo r. o $3.95 April-May 1987 No. 35 p~~ :~::.J ~::.:~ UJ III <..: ):1 >:~. :::1 ill t:) i:'/ r:J :::: Software A~lications I:J ..... j'TJ ::1:) :".~~ ~ t 0.1 • : L> t~:J ~.;~: t "':1 :!:~: t:'l Swimming In The Relational Lake ...................... 14 :1.'., Designing relational databases. I . Expert System ......................................... 22 :.~ I it. l.n Gary designs an expert system with Prolog. :u Nasty Software ........................................ 82 A plague of new programs in the public domain. Hardware Applications Controlling The Real World ............................. 6 Build an 8-channel temperature scanner. The Bleeping PC ...................................... 30 Strange noises from clonal counters. -.j" Who's Making Great Hard Orives ..................... -

Circuit Cellar: Then & Now

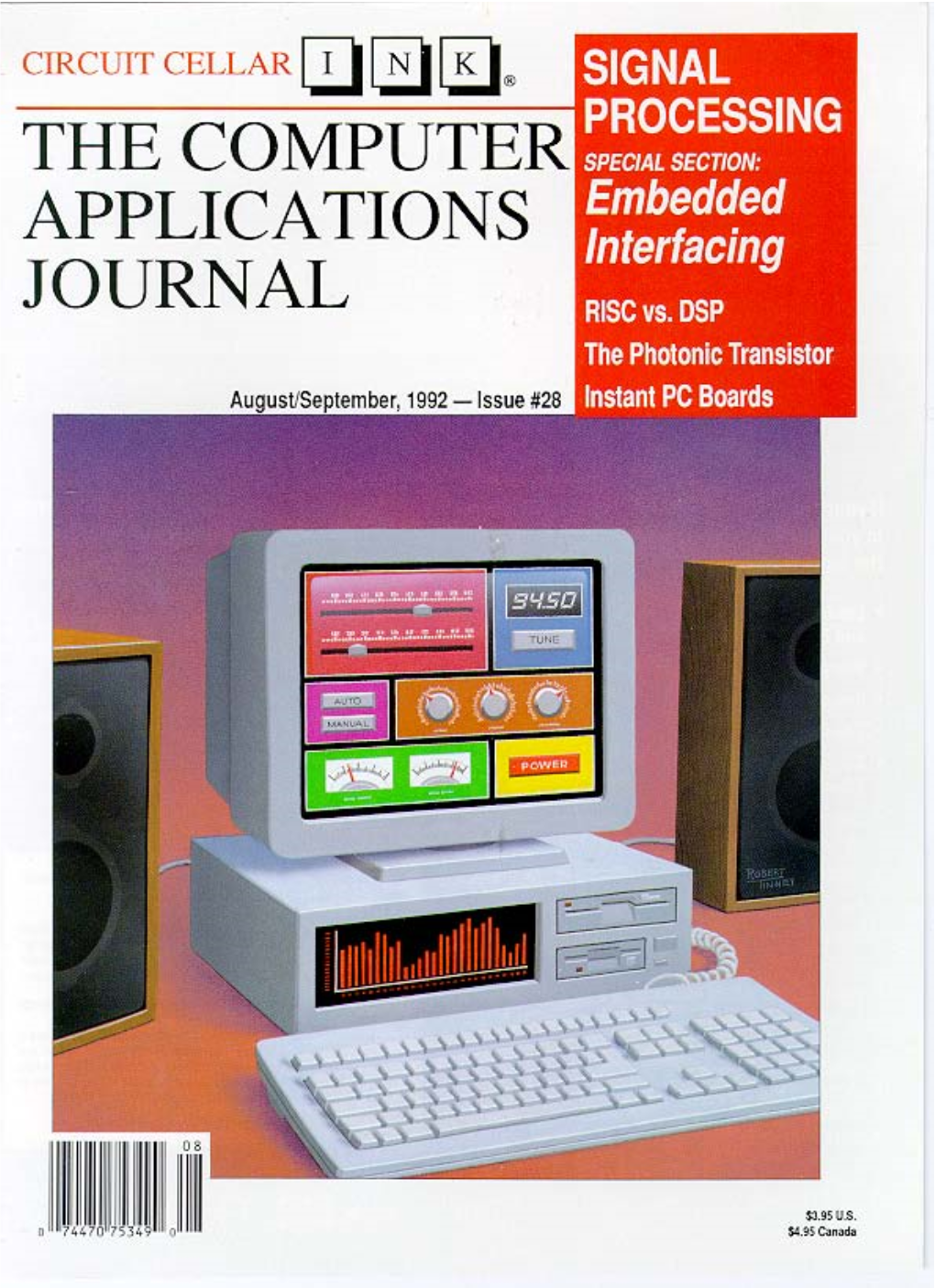

cover1.qxp 2/2/2007 3:43 PM Page 2 #200 March 2007 w w w . c i r c u i t c e CIRCUIT® l l a r . c o m CELLARTHE MAGAZINE FOR COMPUTER APPLICATIONS ROBOTICS Robotic Arm Servo Control Rolling Robot Circuit Cellar: ThenWWW.GiURUMELE.Hi2.RO & Now 03> 7925274 75349 $4.95 U.S. ($5.95 Canada) cover1.qxp 2/2/2007 3:44 PM Page 3 007 CIRCUIT CELLAR (1988 to Present) —Steve Ciarcia describes how he used his HCS to save a life (“A Home Control Event Worth Remembering,” Circuit Cellar 199) “Inside the Box Still Counts” — This was the title of my very first Circuit Cellar INK —George Martin is back with a C language tutorial editorial 19 years ago. Two hundred issues later I still believe it. Like solder being my favorite programming language, I still believe that however appliance-like 2007 (“Hello World … Want Cookie,” Circuit Cellar 198) embedded control and personal computing implementations become, we can’t for- get that the process of achieving that goal isn’t instant. In order to create the —Ed Nisley provides tips for choosing voltage references sophisticated devices and technologies regarded as off-the-shelf, many people (“Voltage References,” Circuit Cellar 193) still have to maintain real expertise in rudimentary design skills. Basically, some- —Tom Cantrell covers using the ’Net as a long RS-232 cable body always has to know what’s inside the box. —Steve Ciarcia, “Inside the Box Still Counts,” Circuit Cellar 200, 2007 (“Device Surfer,” Circuit Cellar 192) —Atmel AVR Design Contest 2006, Sponsored by Atmel, 2006 2006 —DesignStellaris2006 -

COMPUTER JOURNAL 190 Sullivan Crossroad JOURNAL Columbia Falls, Montana 59912 406-257-9119 Features Issue Number 29

~ II " " III I Programming User Support Appl ications Issue Number 29 ".00 Better Software Filter Design Writing Pipeable User Friendly Programs MDISK Add a One Megabyte RAM Disk to Ampro L.B. Using the Hitachi HD64180 Embedded Processor Designs The ZCPR3 Corner Announcing ACPR33 plus Z-COM Customization 68000 Why Use a New OS & the 680001 Detecting the 8087 Math Chip Temperature Sensitive Software Floppy Disk Track Structure A Look at Disk Control Information & Data Capacity ISSN • 07~9331 The COMPUTER THE COMPUTER JOURNAL 190 Sullivan Crossroad JOURNAL Columbia Falls, Montana 59912 406-257-9119 Features Issue Number 29 Better Software Filter Design Editor/Publisher A compromise that allows programs written under Art Carlson DOS to be pipeable. yet still user friendly by Kevin Lacobie 5 Art Director Donna Carlson MDISK Production Assistant Add a one megabyte RAM Disk to your Ampro Judie Overbeek Little Board by Terry Hazen & Jim Cole Circulation 13 Donna Carlson Using The Hitachi HD64180 Contributing Editors Coping with object code incompatibility, Joe Bartel wandering I/O addresses, and using the ASCII ports. C. Thomas Hilton by Kenneth A. Taschner & Frederick B. Maxwell 18 Donald Howes Bill Kibler 68000 Rick Lehrbaum An alternative to the PC for high performance systems Frederick B. Maxwell by Joe Bartel 31 Jay Sage Kenneth A. Taschner Detecting the 8087 Math Chip Routines which work on the XT don't always work on the AT. Entire contents copyright© by E. Clay Buchanan III 36 1987 by The Computer Journal. Floppy Disk Track Structure SUbscription rates-$16 one year (6 Issues), or $28 two years (12 How track structure and sector size affect the formatted capacity . -

Circuit Cellar

EDITOR’S English: INK The Forgotten Language? Ken Davidson I s the English language really so obscure that people have should have been caught early on. However, since he didn’t seem given up trying to use it correctly altogether? Granted, English is to be able to find anything else wrong, I think two bad words out one of the more difficult languages to learn due to its endless of the thousands in the issue isn’t half bad. He could have a field exceptions to rules. It’s usually more important to get your idea day with some other publications I see on the newsstand each across than to get all the parts of the language correct. My month. frustration stems from my recent observations of some so-called I don’t expect our authors to be able to write prize-winning “editors” that can’t even catch a spelling mistake let alone bad articles; I certainly can’t. I also don’t want to discourage anyone punctuation or grammar. from submitting an article because they don’t think it’s good Werecently started the search for additional staff editors. All enough; it can be massaged into something we can all be proud that we’re asking of these people is that they be able to read a raw of. What I would like to encourage, though, is that when writing manuscript; fix spelling, punctuation, and grammar; and convert a piece, have someone else look at it to see if it even makes sense. any “engineerese” into readable English. -

Excerpts from the Circuit Cellar BBS CONNEC

WWW.GiURUMELE.Hi2.RO Words are wonderful in their ability to form vi- module puts an 80286,512K memory, and all of the “glue” sions and emotions in our minds. Such a simple word as chips for a working AT-type computer into a package only “home” can, with itsassociations, bring a tear to a weary slightly larger than an 80486. The engineers at Mi tsumi see traveler’s eye. Other words, take COMDEXasanexample, the 80286 playing an increasing role in embedded applica- can produce fevered visions of technology oozing from the tions, and they are pushing the idea of the entire computer very pores of casinos while armies of disembodied feet as a plug-in module. According to the engineers, fax plod through aisles stretching to infinity.. machines have already been designed around their 80286, Can you tell that I just finished “doing” COMDEX? A and more products are on the way. I think they may be on week of strolling past the latest in microcomputers has left to something with this approach, and we’re working on an me tired and footsore, but encouraged about the future of article showing how to use the module in applications. the small computer industry. A side-effect of the 80286’s move into embedded applications may be the demise of the 80186. The ‘186 has MS-DOS MARCHES ON... been a favorite of designers who wanted to develop soft- ware under MS-DOS but needed more oomph than an . ..or more accurately, the Intel 80x86 family keeps 8088 could muster. Products like the Mitsumi module rolling.