Design of Full Adder and Full Subtractor Using DNA Computing

Total Page:16

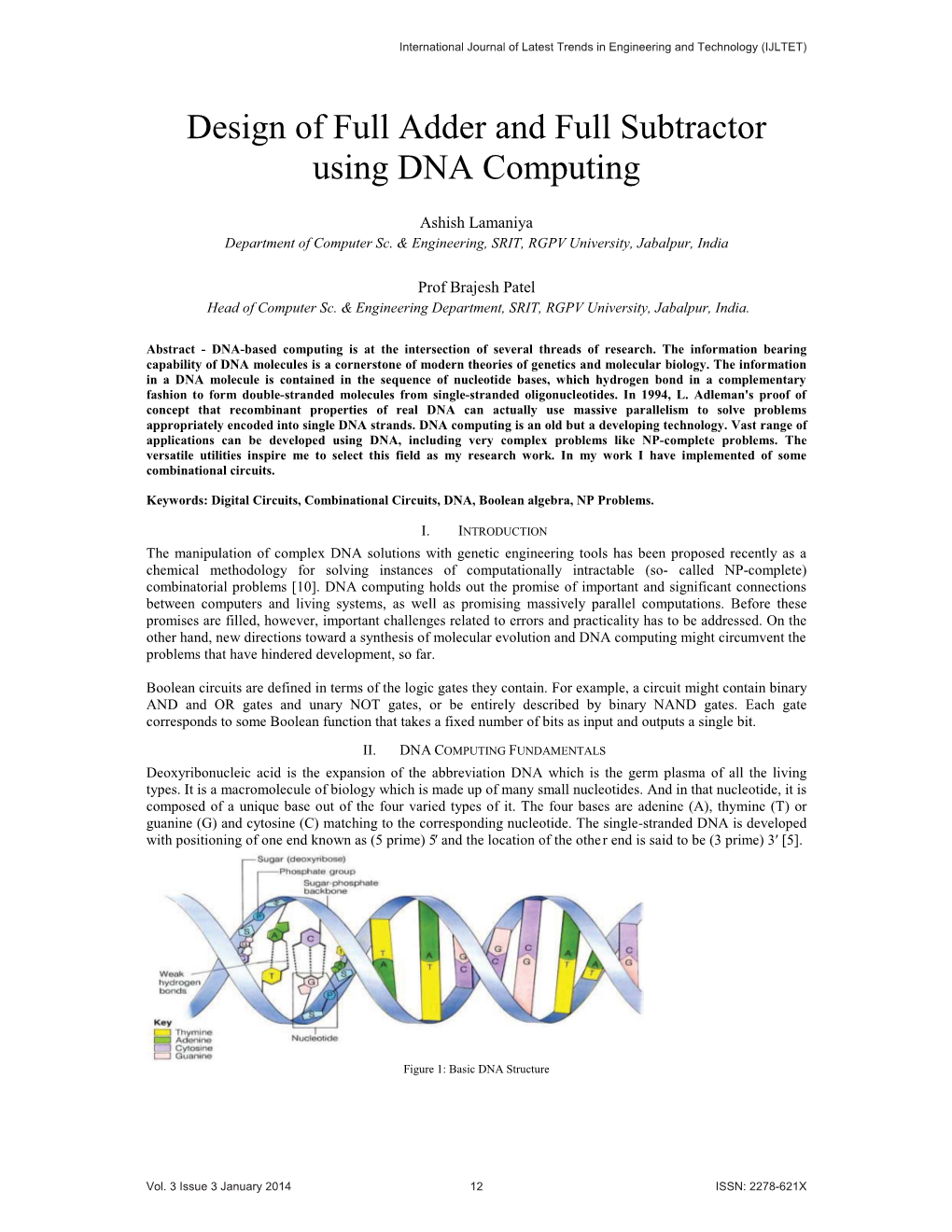

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Fast and Verified Software Stackfor Secure Function Evaluation

Session I4: Verifying Crypto CCS’17, October 30-November 3, 2017, Dallas, TX, USA A Fast and Verified Software Stack for Secure Function Evaluation José Bacelar Almeida Manuel Barbosa Gilles Barthe INESC TEC and INESC TEC and FCUP IMDEA Software Institute, Spain Universidade do Minho, Portugal Universidade do Porto, Portugal François Dupressoir Benjamin Grégoire Vincent Laporte University of Surrey, UK Inria Sophia-Antipolis, France IMDEA Software Institute, Spain Vitor Pereira INESC TEC and FCUP Universidade do Porto, Portugal ABSTRACT as OpenSSL,1 s2n2 and Bouncy Castle,3 as well as prototyping We present a high-assurance software stack for secure function frameworks such as CHARM [1] and SCAPI [31]. More recently, a evaluation (SFE). Our stack consists of three components: i. a veri- series of groundbreaking cryptographic engineering projects have fied compiler (CircGen) that translates C programs into Boolean emerged, that aim to bring a new generation of cryptographic proto- circuits; ii. a verified implementation of Yao’s SFE protocol based on cols to real-world applications. In this new generation of protocols, garbled circuits and oblivious transfer; and iii. transparent applica- which has matured in the last two decades, secure computation tion integration and communications via FRESCO, an open-source over encrypted data stands out as one of the technologies with the framework for secure multiparty computation (MPC). CircGen is a highest potential to change the landscape of secure ITC, namely general purpose tool that builds on CompCert, a verified optimizing by improving cloud reliability and thus opening the way for new compiler for C. It can be used in arbitrary Boolean circuit-based secure cloud-based applications. -

Week 1: an Overview of Circuit Complexity 1 Welcome 2

Topics in Circuit Complexity (CS354, Fall’11) Week 1: An Overview of Circuit Complexity Lecture Notes for 9/27 and 9/29 Ryan Williams 1 Welcome The area of circuit complexity has a long history, starting in the 1940’s. It is full of open problems and frontiers that seem insurmountable, yet the literature on circuit complexity is fairly large. There is much that we do know, although it is scattered across several textbooks and academic papers. I think now is a good time to look again at circuit complexity with fresh eyes, and try to see what can be done. 2 Preliminaries An n-bit Boolean function has domain f0; 1gn and co-domain f0; 1g. At a high level, the basic question asked in circuit complexity is: given a collection of “simple functions” and a target Boolean function f, how efficiently can f be computed (on all inputs) using the simple functions? Of course, efficiency can be measured in many ways. The most natural measure is that of the “size” of computation: how many copies of these simple functions are necessary to compute f? Let B be a set of Boolean functions, which we call a basis set. The fan-in of a function g 2 B is the number of inputs that g takes. (Typical choices are fan-in 2, or unbounded fan-in, meaning that g can take any number of inputs.) We define a circuit C with n inputs and size s over a basis B, as follows. C consists of a directed acyclic graph (DAG) of s + n + 2 nodes, with n sources and one sink (the sth node in some fixed topological order on the nodes). -

Rigorous Cache Side Channel Mitigation Via Selective Circuit Compilation

RiCaSi: Rigorous Cache Side Channel Mitigation via Selective Circuit Compilation B Heiko Mantel, Lukas Scheidel, Thomas Schneider, Alexandra Weber( ), Christian Weinert, and Tim Weißmantel Technical University of Darmstadt, Darmstadt, Germany {mantel,weber,weissmantel}@mais.informatik.tu-darmstadt.de, {scheidel,schneider,weinert}@encrypto.cs.tu-darmstadt.de Abstract. Cache side channels constitute a persistent threat to crypto implementations. In particular, block ciphers are prone to attacks when implemented with a simple lookup-table approach. Implementing crypto as software evaluations of circuits avoids this threat but is very costly. We propose an approach that combines program analysis and circuit compilation to support the selective hardening of regular C implemen- tations against cache side channels. We implement this approach in our toolchain RiCaSi. RiCaSi avoids unnecessary complexity and overhead if it can derive sufficiently strong security guarantees for the original implementation. If necessary, RiCaSi produces a circuit-based, hardened implementation. For this, it leverages established circuit-compilation technology from the area of secure computation. A final program analysis step ensures that the hardening is, indeed, effective. 1 Introduction Cache side channels are unintended communication channels of programs. Cache- side-channel leakage might occur if a program accesses memory addresses that depend on secret information like cryptographic keys. When these secret-depen- dent memory addresses are loaded into a shared cache, an attacker might deduce the secret information based on observing the cache. Such cache side channels are particularly dangerous for implementations of block ciphers, as shown, e.g., by attacks on implementations of DES [58,67], AES [2,11,57], and Camellia [59,67,73]. -

Probabilistic Boolean Logic, Arithmetic and Architectures

PROBABILISTIC BOOLEAN LOGIC, ARITHMETIC AND ARCHITECTURES A Thesis Presented to The Academic Faculty by Lakshmi Narasimhan Barath Chakrapani In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science, College of Computing Georgia Institute of Technology December 2008 PROBABILISTIC BOOLEAN LOGIC, ARITHMETIC AND ARCHITECTURES Approved by: Professor Krishna V. Palem, Advisor Professor Trevor Mudge School of Computer Science, College Department of Electrical Engineering of Computing and Computer Science Georgia Institute of Technology University of Michigan, Ann Arbor Professor Sung Kyu Lim Professor Sudhakar Yalamanchili School of Electrical and Computer School of Electrical and Computer Engineering Engineering Georgia Institute of Technology Georgia Institute of Technology Professor Gabriel H. Loh Date Approved: 24 March 2008 College of Computing Georgia Institute of Technology To my parents The source of my existence, inspiration and strength. iii ACKNOWLEDGEMENTS आचायातर् ्पादमादे पादं िशंयः ःवमेधया। पादं सॄचारयः पादं कालबमेणच॥ “One fourth (of knowledge) from the teacher, one fourth from self study, one fourth from fellow students and one fourth in due time” 1 Many people have played a profound role in the successful completion of this disser- tation and I first apologize to those whose help I might have failed to acknowledge. I express my sincere gratitude for everything you have done for me. I express my gratitude to Professor Krisha V. Palem, for his energy, support and guidance throughout the course of my graduate studies. Several key results per- taining to the semantic model and the properties of probabilistic Boolean logic were due to his brilliant insights. -

Privacy Preserving Computations Accelerated Using FPGA Overlays

Privacy Preserving Computations Accelerated using FPGA Overlays A Dissertation Presented by Xin Fang to The Department of Electrical and Computer Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering Northeastern University Boston, Massachusetts August 2017 To my family. i Contents List of Figures v List of Tables vi Acknowledgments vii Abstract of the Dissertation ix 1 Introduction 1 1.1 Garbled Circuits . 1 1.1.1 An Example: Computing Average Blood Pressure . 2 1.2 Heterogeneous Reconfigurable Computing . 3 1.3 Contributions . 3 1.4 Remainder of the Dissertation . 5 2 Background 6 2.1 Garbled Circuits . 6 2.1.1 Garbled Circuits Overview . 7 2.1.2 Garbling Phase . 8 2.1.3 Evaluation Phase . 10 2.1.4 Optimization . 11 2.2 SHA-1 Algorithm . 12 2.3 Field-Programmable Gate Array . 13 2.3.1 FPGA Architecture . 13 2.3.2 FPGA Overlays . 14 2.3.3 Heterogeneous Computing Platform using FPGAs . 16 2.3.4 ProceV Board . 17 2.4 Related Work . 17 2.4.1 Garbled Circuit Algorithm Research . 17 2.4.2 Garbled Circuit Implementation . 19 2.4.3 Garbled Circuit Acceleration . 20 ii 3 System Design Methodology 23 3.1 Garbled Circuit Generation System . 24 3.2 Software Structure . 26 3.2.1 Problem Generation . 26 3.2.2 Layer Extractor . 30 3.2.3 Problem Parser . 31 3.2.4 Host Code Generation . 32 3.3 Simulation of Garbled Circuit Generation . 33 3.3.1 FPGA Overlay Architecture . 33 3.3.2 Garbled Circuit AND Overlay Cell . -

Reaction Systems and Synchronous Digital Circuits

molecules Article Reaction Systems and Synchronous Digital Circuits Zeyi Shang 1,2,† , Sergey Verlan 2,† , Ion Petre 3,4 and Gexiang Zhang 1,∗ 1 School of Electrical Engineering, Southwest Jiaotong University, Chengdu 611756, Sichuan, China; [email protected] 2 Laboratoire d’Algorithmique, Complexité et Logique, Université Paris Est Créteil, 94010 Créteil, France; [email protected] 3 Department of Mathematics and Statistics, University of Turku, FI-20014, Turku, Finland; ion.petre@utu.fi 4 National Institute for Research and Development in Biological Sciences, 060031 Bucharest, Romania * Correspondence: [email protected] † These authors contributed equally to this work. Received: 25 March 2019; Accepted: 28 April 2019 ; Published: 21 May 2019 Abstract: A reaction system is a modeling framework for investigating the functioning of the living cell, focused on capturing cause–effect relationships in biochemical environments. Biochemical processes in this framework are seen to interact with each other by producing the ingredients enabling and/or inhibiting other reactions. They can also be influenced by the environment seen as a systematic driver of the processes through the ingredients brought into the cellular environment. In this paper, the first attempt is made to implement reaction systems in the hardware. We first show a tight relation between reaction systems and synchronous digital circuits, generally used for digital electronics design. We describe the algorithms allowing us to translate one model to the other one, while keeping the same behavior and similar size. We also develop a compiler translating a reaction systems description into hardware circuit description using field-programming gate arrays (FPGA) technology, leading to high performance, hardware-based simulations of reaction systems. -

SOTERIA: in Search of Efficient Neural Networks for Private Inference

SOTERIA: In Search of Efficient Neural Networks for Private Inference Anshul Aggarwal, Trevor E. Carlson, Reza Shokri, Shruti Tople National University of Singapore (NUS), Microsoft Research {anshul, trevor, reza}@comp.nus.edu.sg, [email protected] Abstract paper, we focus on private computation of inference over deep neural networks, which is the setting of machine learning-as- ML-as-a-service is gaining popularity where a cloud server a-service. Consider a server that provides a machine learning hosts a trained model and offers prediction (inference) ser- service (e.g., classification), and a client who needs to use vice to users. In this setting, our objective is to protect the the service for an inference on her data record. The server is confidentiality of both the users’ input queries as well as the not willing to share the proprietary machine learning model, model parameters at the server, with modest computation and underpinning her service, with any client. The clients are also communication overhead. Prior solutions primarily propose unwilling to share their sensitive private data with the server. fine-tuning cryptographic methods to make them efficient We consider an honest-but-curious threat model. In addition, for known fixed model architectures. The drawback with this we assume the two parties do not trust, nor include, any third line of approach is that the model itself is never designed to entity in the protocol. In this setting, our first objective is to operate with existing efficient cryptographic computations. design a secure protocol that protects the confidentiality of We observe that the network architecture, internal functions, client data as well as the prediction results against the server and parameters of a model, which are all chosen during train- who runs the computation. -

The Size and Depth of Layered Boolean Circuits

The Size and Depth of Layered Boolean Circuits Anna G´al? and Jing-Tang Jang?? Dept. of Computer Science, University of Texas at Austin, Austin, TX 78712-1188, USA fpanni, [email protected] Abstract. We consider the relationship between size and depth for layered Boolean circuits, synchronous circuits and planar circuits as well as classes of circuits with small separators. In particular, we show that every layered Boolean circuitp of size s can be simulated by a lay- ered Boolean circuit of depth O( s log s). For planar circuits and syn- p chronous circuits of size s, we obtain simulations of depth O( s). The best known result so far was by Paterson and Valiant [16], and Dymond and Tompa [6], which holds for general Boolean circuits and states that D(f) = O(C(f)= log C(f)), where C(f) and D(f) are the minimum size and depth, respectively, of Boolean circuits computing f. The proof of our main result uses an adaptive strategy based on the two-person peb- ble game introduced by Dymond and Tompa [6]. Improving any of our results by polylog factors would immediately improve the bounds for general circuits. Key words: Boolean circuits, circuit size, circuit depth, pebble games 1 Introduction In this paper, we study the relationship between the size and depth of fan-in 2 Boolean circuits over the basis f_; ^; :g. Given a Boolean circuit C, the size of C is the number of gates in C, and the depth of C is the length of the longest path from any input to the output. -

Accelerating Large Garbled Circuits on an FPGA-Enabled Cloud

Accelerating Large Garbled Circuits on an FPGA-enabled Cloud Miriam Leeser Mehmet Gungor Kai Huang Stratis Ioannidis Dept of ECE Dept of ECE Dept of ECE Dept of ECE Northeastern University Northeastern University Northeastern University Northeastern University Boston, MA Boston, MA Boston, MA Boston, MA [email protected] [email protected] [email protected] [email protected] Abstract—Garbled Circuits (GC) is a technique for ensuring management technique presented is also applicable to other the privacy of inputs from users and is particularly well suited big data problems that make use of FPGAs. for FPGA implementations in the cloud where data analytics is In this paper we describe approaches and experiments to im- frequently run. Secure Function Evaluation, such as that enabled by GC, is orders of magnitude slower than processing in the prove on previous implementations in order to obtain improved clear. We present our best implementation of GC on Amazon speedup as well as support larger examples. Specifically, the Web Services (AWS) that implements garbling on Amazon’s main contribution of this paper is to use the memory available FPGA enabled F1 instances. In this paper we present the largest on an FPGA more efficiently in order to support large data problems garbled to date on FPGA instances, which includes sets on FPGA instances and improve the speed up obtained problems that are represented by over four million gates. Our implementation speeds up garbling 20 times over software over from running applications on FPGAs in the cloud. a range of different circuit sizes. -

Boolean Circuit Problems

Boolean Circuit Problems Problem 1. Adding It Up How could we use boolean circuits to build a calculator? Let's investigate... a) Suppose that you have a one-bit number A, and a one-bit number B. What truth table represents the product of multiplying A times B? What circuit could you build to compute that truth table? A B Product 0 0 0 1 1 0 1 1 Circuit: b) Suppose now that you want to add A and B instead of multiplying them. However, 1+1 is 2, which is bigger than either 0 or 1 – so now we need two circuits: one to compute the sum bit, and one to compute a carry bit. Fill in the rest of the truth table, and write the two circuits. A B Sum Carry 0 0 0 1 1 0 1 0 1 1 0 1 Circuit for Sum: Circuit for Carry: c) An “adder” circuit component, as used to add up numbers longer than just one bit, actually needs to add up three bits – A, B, and C. However, we still only have the sum bit and the carry bit as the two outputs. Write the two circuits for this truth table. A B C Sum Carry 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 0 0 1 0 0 1 1 0 0 1 1 0 1 1 0 1 0 1 1 1 1 1 1 Circuit for Sum: Circuit for Carry: Problem 2. Functional Completeness A set of logic gates is called functionally complete if you can use those logic gates to construct any other logic gate. -

Boolean Logic and Some Elements of Computational Complexity

General Information and Communication Technology 1 Course Number 320211 Jacobs University Bremen Herbert Jaeger Second module of this course: Boolean logic and Some elements of computational complexity 1 1 Boolean logic 1.1 What it is and what it is good for in CS There are two views on Boolean logic (BL) which are relevant for CS. In informal terms they can be described as follows: 1. In digital computers, information is coded and processed just by "zeros" and "ones" – concretely, by certain voltages in the electronic circuitry which are switching (veeeery fast!) between values of 0 Volt (corresponding to "zero") and some system-specific positive voltage V+, for instance V+ = 5 Volts (corresponding to "one"). V+ = 5 Volts was a standard in old digital circuits of the first personal computers, today the voltages are mostly lower. You know that much of the computation in a computer is done in a particular microchip called the central processing unit (CPU). The CPU contains thousands (or millions) of transistor-based electronic mini-circuits called logic gates. At the output end of such a gate one can measure a voltage which is approximately either 0 or V+. The specs of a computer contain a statement like "CPU speed is 2.5 GHz". GHz stands for Giga-Hertz, a measure of frequency. 1 Hertz means a frequency of "1 event per second", 2.5 GHz means "2.5 × 109 events per second". This means that 2.5 × 109 times in a second, all the gates may switch their output voltage from 0 to V+ or vice versa (or stay on the same level). -

GMW Vs. Yao? Efficient Secure Two-Party Computation with Low

GMW vs. Yao? Efficient Secure Two-Party Computation with Low Depth Circuits Thomas Schneider and Michael Zohner Engineering Cryptographic Protocols Group (ENCRYPTO), European Center for Security and Privacy by Design (EC SPRIDE), Technische Universit¨atDarmstadt, Germany fthomas.schneider,[email protected] Abstract. Secure two-party computation is a rapidly emerging field of research and enables a large variety of privacy-preserving applications such as mobile social networks or biometric identification. In the late eighties, two different approaches were proposed: Yao's garbled circuits and the protocol of Goldreich-Micali-Wigderson (GMW). Since then, re- search has mostly focused on Yao's garbled circuits as they were believed to yield better efficiency due to their constant round complexity. In this work we give several optimizations for an efficient implementa- tion of the GMW protocol. We show that for semi-honest adversaries the optimized GMW protocol can outperform today's most efficient im- plementations of Yao's garbled circuits, but highly depends on a low network latency. As a first step to overcome these latency issues, we summarize depth-optimized circuit constructions for various standard tasks. As application scenario we consider privacy-preserving face recog- nition and show that our optimized framework is up to 100 times faster than previous works even in settings with high network latency. Keywords: GMW protocol, optimizations, privacy-preserving face recognition 1 Introduction Generic secure two-party computation allows two parties to jointly compute any function on their private inputs without revealing anything but the result. Interestingly, two different approaches have been introduced at about the same time in the late eighties: Yao's garbled circuits [33] and the protocol of Goldreich- Micali-Wigderson (GMW) [11, 12].