Williams Pinball CPU Tester Edward Cheung [email protected] Rev. Date: 8/15/2015 (Change History on Last Page)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Pin Golf Score Sheet Name: # Pinball Novice Average Pro Score 1

Pin Golf Score Sheet Pin Golf Score Sheet Name: Name: # Pinball Novice Average Pro Score # Pinball Novice Average Pro Score Lite ABCD A-D + Bonus A-D + Bonus + Lite ABCD A-D + Bonus A-D + Bonus + Paddock 1: 1: Finish Race Paddock 1: 1: Finish Race 1 2: 2:: 1: 1 2: 2:: 1: (W ’69) 3: 2: (W ’69) 3: 2: 3: 3: 3: 3: Lite ABCD A-D + Bonus A-D + Bonus + Lite ABCD A-D + Bonus A-D + Bonus + Centigrade 37 1: 1: Adv Therm Centigrade 37 1: 1: Adv Therm 2 2: 2:: 1: 2 2: 2:: 1: (G ’77) 3: 3: 2: (G ’77) 3: 3: 2: 3: 3: Lite ABC A-C + Bonus A-C + Bonus + Lite ABC A-C + Bonus A-C + Bonus + Joker Poker 1: 1: Cards Joker Poker 1: 1: Cards 3 2: 2:: 1: 3 2: 2:: 1: (G ’78) 3: 3: 2: (G ’78) 3: 3: 2: 3: 3: 50,000 1 million 2 million 50,000 1 million 2 million Cyclone 1: 1: 1: Cyclone 1: 1: 1: 4 4 (W ’88) 2: 2: 2: (W ’88) 2: 2: 2: 3: 3: 3: 3: 3: 3: 1.25 million 2.5 million 5 million 1.25 million 2.5 million 5 million Bad Cats 1: 1: 1: Bad Cats 1: 1: 1: 5 5 (W ’89) 2: 2: 2: (W ’89) 2: 2: 2: 3: 3: 3: 3: 3: 3: 625,000 1.25 million 2.5 million 625,000 1.25 million 2.5 million Black Knight 2K 1: 1: 1: Black Knight 2K 1: 1: 1: 6 6 (W ’89) 2: 2: 2: (W ’89) 2: 2: 2: 3: 3: 3: 3: 3: 3: 750,000 1.5 million 3 million 750,000 1.5 million 3 million Elvira ATPM 1: 1: 1: Elvira ATPM 1: 1: 1: 7 7 (B ’89) 2: 2: 2: (B ’89) 2: 2: 2: 3: 3: 3: 3: 3: 3: 1.5 million 3 million 6 million 1.5 million 3 million 6 million 1: 1: 1: 1: 1: 1: 8 Diner (W ’90) 2: 2: 2: 8 Diner (W ’90) 2: 2: 2: 3: 3: 3: 3: 3: 3: 1.25 million 2.5 million 5 million 1.25 million 2.5 million 5 million Addams Family -

Pinball Game List

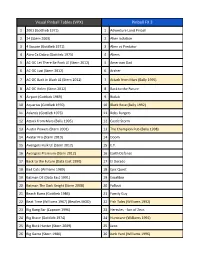

Visual Pinball Tables (VPX) Pinball FX 3 1 2001 (Gottlieb 1971) 1 Adventure Land Pinball 2 24 (Stern 2009) 2 Alien Isolation 3 4 Square (Gottlieb 1971) 3 Alien vs Predator 4 Abra Ca Dabra (Gottlieb 1975) 4 Aliens 5 AC-DC Let There Be Rock LE (Stern 2012) 5 American Dad 6 AC-DC Luci (Stern 2012) 6 Archer 7 AC-DC Back in Black LE (Stern 2012) 7 Attack from Mars (Bally 1995) 8 AC-DC Helen (Stern 2012) 8 Back to the Future 9 Airport (Gottlieb 1969) 9 Biolab 10 Aquarius (Gottlieb 1970) 10 Black Rose (Bally 1992) 11 Atlantis (Gottlieb 1975) 11 Bobs Burgers 12 Attack from Mars (Bally 1995) 12 Castle Storm 13 Austin Powers (Stern 2001) 13 The Champion Pub (Bally 1998) 14 Avatar Pro (Stern 2010) 14 Doom 15 Avengers Hulk LE (Stern 2012) 15 E.T. 16 Avengers Premium (Stern 2012) 16 Earth Defense 17 Back to the Future (Data East 1990) 17 El Dorado 18 Bad Cats (Williams 1989) 18 Epic Quest 19 Batman DE (Data East 1991) 19 Excalibur 20 Batman The Dark Knight (Stern 2008) 20 Fallout 21 Beach Bums (Gottlieb 1986) 21 Family Guy 22 Beat Time (Williams 1967) (Beatles MOD) 22 Fish Tales (Williams 1992) 23 Big Bang Bar (Capcom 1996) 23 Hercules - Son of Zeus 24 Big Brave (Gottlieb 1974) 24 Hurricane (Williams 1991) 25 Big Buck Hunter (Stern 2009) 25 Jaws 26 Big Game (Stern 1980) 26 Junk Yard (Williams 1996) Visual Pinball Tables (VPX) Pinball FX 3 27 Big Guns (Williams 1987) 27 Jurassic Park 28 Black Knight (Williams 1980) 28 Jurassic Park Pinball Mayhem 29 Black Knight 2000 (Williams 1989) 29 Jurassic World 30 Black Rose (Bally 1992) 30 Mars 31 Blue Note (Gottlieb 1979) 31 Marvel - Age of Ultron 32 Bram Stoker's Dracula (Williams 1993) 32 Marvel - Ant-Man 33 Bronco (Gottlieb 1977) 33 Marvel - Blade 34 Bubba the Redneck Werewolf (2018) 34 Marvel - Captain America 35 Buccaneer (Gottlieb 1976) 35 Marvel - Civil War 36 Buckaroo (Gottlieb 1965) 36 Marvel - Deadpool 37 Bugs Bunny B. -

1080-Pinballgamelist.Pdf

No. Table Name Table Type 1 12 Days Christmas VPX Table 2 2001 (Gottlieb 1971) VP 9 Table 3 24 (Stern 2009) VP 9 Table 4 250cc (Inder 1992) VP 9 Table 5 4 Roses (Williams 1962) VP 9 Table 6 4 Square (Gottlieb 1971) VP 9 Table 7 Aaron Spelling (Data East 1992) VP 9 Table 8 Abra Ca Dabra (Gottlieb 1975) VP 9 Table 9 ACDC (Stern 2012) VP 9 Table 10 ACDC Pro - PM5 (Stern 2012) PM5 Table 11 ACDC Pro (Stern 2012) VP 9 Table 12 Addams Family Golden (Williams 1994) VP 9 Table 13 Adventures of Rocky and Bullwinkle and Friends (Data East 1993) VP 9 Table 14 Aerosmith Future Table 15 Agents 777 (GamePlan 1984) VP 9 Table 16 Air Aces (Bally 1975) VP 9 Table 17 Airborne (Capcom 1996) VP 9 Table 18 Airborne Avenger (Atari 1977) VP 9 Table 19 Airport (Gottlieb 1969) VP 9 Table 20 Aladdin's Castle (Bally 1976) VP 9 Table 21 Alaska (Interflip 1978) VP 9 Table 22 Algar (Williams 1980) VP 9 Table 23 Ali (Stern 1980) VP 9 Table 24 Ali Baba (Gottlieb 1948) VP 9 Table 25 Alice Cooper Future Table 26 Alien Poker (Williams 1980) VP 9 Table 27 Alien Star (Gottlieb 1984) VP 9 Table 28 Alive! (Brunswick 1978) VPX Table 29 Alle Neune (NSM 1976) VP 9 Table 30 Alley Cats (Williams 1985) VP 9 Table 31 Alpine Club (Williams 1965) VP 9 Table 32 Al's Garage Band Goes On World Tour (Alivin G. 1992) VP 9 Table 33 Amazing Spiderman (Gottlieb 1980) VP 9 Table 34 Amazon Hunt (Gottlieb 1983) VP 9 Table 35 America 1492 (Juegos Populares 1986) VP 9 Table 36 Amigo (Bally 1973) VP 9 Table 37 Andromeda (GamePlan 1985) VP 9 Table 38 Animaniacs SE Future Table 39 Antar (Playmatic 1979) -

24 1/1/2009 6/4/2020 3.38 4 AC/DC 1/1/2012 4/9/2020 5 1 Ace Of

24 1/1/2009 6/4/2020 3.38 4 AC/DC 1/1/2012 4/9/2020 5 1 Ace Of Speed 6/11/2020 0 0 The Addams Family 1/1/1992 4/19/2020 4.36 11 Aerosmith 2/1/2017 6/11/2020 0 0 Algar 1/1/1980 7/13/2020 0 0 Aliens 5/11/2020 0 0 America's Most Haunted 5/10/2020 0 0 Apollo 13 1/1/1995 6/16/2020 0 0 Asteroid Annie 5/10/2020 0 0 Atlantis 6/4/2020 0 0 Attack and Revenge from Mars 7/23/2020 0 0 Attack from Mars 12/1/1995 6/23/2020 4.06 8 Austin Powers 1/1/2001 6/7/2020 0 0 Avatar 8/27/2010 5/17/2020 0 0 The Avengers 1/1/2012 8/9/2020 0 0 Aztec 7/13/2020 0 0 Back to the Future 1/1/1990 6/4/2020 5 5 Bad Cats 11/6/1989 6/22/2020 0 0 The Bally Game Show 1/26/1990 6/11/2020 0 0 Barb Wire 1/1/1996 5/27/2020 0 0 Barbarella 6/16/2020 0 0 Barracora 6/20/2020 0 0 Batman 1/1/1991 5/15/2020 0 0 Batman (Stern) 7/21/2008 8/8/2020 0 0 Batman 66 6/18/2020 0 0 Batman Forever 1/1/1995 6/23/2020 0 0 Baywatch 1/1/1995 6/18/2020 0 0 Beach Bums 6/10/2020 0 0 Big Bang Bar 1/1/1996 4/16/2020 5 2 Big Buck Hunter Pro 1/1/2010 6/10/2020 0 0 Big Shot 7/13/2020 0 0 Black Belt 7/12/2020 0 0 Black Hole 1/1/1981 6/11/2020 0 0 Black Knight 4/4/1989 5/10/2020 4.5 4 Black Knight 2000 4/4/1989 5/11/2020 4.5 4 Black Rose 7/1/1992 6/4/2020 3 3 Bram Stoker's Dracula 1/1/1993 4/10/2020 0 0 Breakshot 5/1/1996 5/29/2020 1.5 1 Bubba the Redneck Werewolf 5/27/2020 0 0 Buck Rogers 6/16/2020 0 0 Bugs Bunny's Birthday Ball 12/3/1990 6/3/2020 0 0 Cactus Canyon 1/1/1998 7/26/2020 0 0 Capt. -

Roadshow Shrine Road Show

RoadShow Shrine Road Show (for LA-4 and LA-5 ROMs), Version 2.0 (April 9, 1995) Contents: ❍ Changes from Version 1.1 ❍ History and Thanks ❍ Overview ❍ Playfield Description ❍ General Rules and Scoring ❍ Blast ❍ Flying Rocks ❍ The Wheel ❍ Souvenirs ❍ Multiball ❍ City Scenes (Modes) ❍ Super Payday (Wizard Bonus) ❍ The Magic Standup ❍ Combos ❍ Easter Eggs and Cheats ❍ Bugs ❍ Miscellaneous Stuff ❍ Operator Adjustments ❍ Strategies Changes from Version 1.1: ❍ Scott now has access to an LA-5 machine, so some info on L-5 has been added. ❍ Scott's email address has changed. ❍ Corrected info on the Magic Standup. It turns out that it's more powerful than we thought before! ❍ Added the value of Fun With Bonus. file:///D|/Pinballs/RoadShow_htm/Roadshow2.htm (1 of 43) [4/22/2001 4:33:24 PM] RoadShow Shrine ❍ Added operator adjustments as section 17. Thanx to Cameron Silver for providing the list of adjustments. ❍ Added that a mode won't start if you collect Bad Weather at the Blast Hole. ❍ Added a few more joke souvenirs. ❍ Added a note about how the status report shows the number of locks. ❍ Added in what happens after you complete all the cities. ❍ Added a few more bugs. ❍ Added in a point-scoring strategy (go for all the souvenirs you can). ❍ Fixed up the quotes (Scott did all of the work here). ❍ Fixed up a *lot* of little details here and there. Top History and Thanks: Version 2.0: Major revision that incorporated lots of changes and fixes. The section of operator adjustments was added. Version 1.1: This was a quick update to fix the glaring goofs in 1.0. -

Mancave Games Virtual Pinball Game List

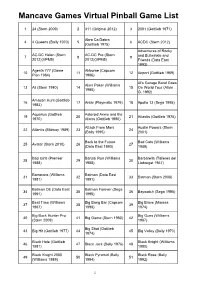

Mancave Games Virtual Pinball Game List 1 24 (Stern 2009) 2 311(Original 2012) 3 2001 (Gottlieb 1971) AbraCa Dabra 4 4Queens( Bally 1970) 5 6 ACDC (Stern 2012) (Gottlieb 1975) Adventures of Rocky AC-DC Helen( Stern AC-DC Pro (Stern 7 8 9 and Bullwinkle and 2012)(VPM5) 2012)(VPM5) Friends (DataEast 1993) Agents777 (Game Airborne (Capcom 10 11 12 Airport (Gottlieb 1969) Plan 1984) 1996) Al's Garage Band Goes Alien Poker (Williams 13 Ali (Stern 1980) 14 15 On World Tour (Alivin 1980) G. 1992) Amazon Hunt (Gottlieb 16 17 Antar (Playmatic 1979) 18 Apollo 13 (Sega 1995) 1983) Aquarius (Gottlieb Asteroid Annie andt he 19 20 21 Atlantis (Gottlieb 1975) 1970) Aliens (Gottlieb 1980) Attack From Mars Austin Powers (Stern 22 Atlantis (Midway 1989) 23 24 (Bally 1995) 2001) Back to the Future Bad Cats (Williams 25 Avatar (Stern 2010) 26 27 (DataEast 1990) 1989) Bad Girls (Premier Banzai Run (Williams Barbarella( Talleres del 28 29 30 1988) 1988) Llobregat 1967) Barracora (Williams Batman (DataEast 31 32 33 Batman (Stern 2008) 1981) 1991) Batman DE (DataEast Batman Forever (Sega 34 35 36 Baywatch (Sega 1995) 1991) 1995) Beat Time (Williams Big Bang Bar (Capcom Big Brave (Maresa 37 38 39 1967) 1996) 1974) Big Buck Hunter Pro Big Guns (Williams 40 41 Big Game (Stern 1980) 42 (Stern 2009) 1987) Big Shot (Gottlieb 43 Big Hit (Gottlieb 1977) 44 45 Big Valley (Bally 1970) 1974) Black Hole (Gottlieb Black Knight (Williams 46 47 Black Jack (Bally 1976) 48 1981) 1980) Black Knight 2000 Black Pyramid (Bally Black Rose (Bally 49 50 51 (Williams 1989) 1984) 1992) -

PINBALL NVRAM GAME LIST This List Was Created to Make It Easier for Customers to Figure out What Type of NVRAM They Need for Each Machine

PINBALL NVRAM GAME LIST This list was created to make it easier for customers to figure out what type of NVRAM they need for each machine. Please consult the product pages at www.pinitech.com for each type of NVRAM for further information on difficulty of installation, any jumper changes necessary on your board(s), a diagram showing location of the RAM being replaced & more. *NOTE: This list is meant as quick reference only. On Williams WPC and Sega/Stern Whitestar games you should check the RAM currently in your machine since either a 6264 or 62256 may have been used from the factory. On Williams System 11 games you should check that the chip at U25 is 24-pin (6116). See additional diagrams & notes at http://www.pinitech.com/products/cat_memory.php for assistance in locating the RAM on your board(s). PLUG-AND-PLAY (NO SOLDERING) Games below already have an IC socket installed on the boards from the factory and are as easy as removing the old RAM and installing the NVRAM (then resetting scores/settings per the manual). • BALLY 6803 → 6116 NVRAM • SEGA/STERN WHITESTAR → 6264 OR 62256 NVRAM (check IC at U212, see website) • DATA EAST → 6264 NVRAM (except Laser War) • CLASSIC BALLY → 5101 NVRAM • CLASSIC STERN → 5101 NVRAM (later Stern MPU-200 games use MPU-200 NVRAM) • ZACCARIA GENERATION 1 → 5101 NVRAM **NOT** PLUG-AND-PLAY (SOLDERING REQUIRED) The games below did not have an IC socket installed on the boards. This means the existing RAM needs to be removed from the board & an IC socket installed. -

Cutbank 84 Article 1

CutBank Volume 1 Issue 84 CutBank 84 Article 1 Spring 2016 CutBank 84 Follow this and additional works at: https://scholarworks.umt.edu/cutbank Part of the Creative Writing Commons Let us know how access to this document benefits ou.y Recommended Citation (2016) "CutBank 84," CutBank: Vol. 1 : Iss. 84 , Article 1. Available at: https://scholarworks.umt.edu/cutbank/vol1/iss84/1 This Full Volume is brought to you for free and open access by ScholarWorks at University of Montana. It has been accepted for inclusion in CutBank by an authorized editor of ScholarWorks at University of Montana. For more information, please contact [email protected]. CutBank | 84 ISBN 9781939717092 CutBank 84 9 781939 717092 CutBank 84 CutBank is published biannually at the University of Montana by graduate students in the Creative Writing Program. Publication is funded and supported by the As- sociated Students of Montana, the Pleiades Foundation, the Second Wind Reading Series, Humanities Montana, Tim O’Leary, Michelle Cardinal, William Kittredge, Annick Smith, Truman Capote Literary Trust, Sponsors of the Fall Writer’s Opus, the Department of English, the Creative Writing Program, Kevin Canty, Judy Blunt, Karin Schalm, Michael Fitzgerald & Submittable, and our readers & donors. Subscriptions are $15 per year + $3 for subscriptions outside of North America. Make checks payable to CutBank or shop online at www.cutbankonline.org/subscribe. Our reading period is September 15 - February 1. Complete submission guidelines are available online. No portion of CutBank may be reproduced without permission. All rights reserved. All correspondence to: CutBank English Department, LA 133 University of Montana Missoula, MT 59812 Printed by Sheridan Press. -

Nome 24 (Stern) (2009) (Collectors Edition) (1.01) 2001 (Gottlieb

Nome 24 (Stern) (2009) (Collectors Edition) (1.01) 2001 (Gottlieb) (1971) (2.00) Abra Ca Dabra (Gottlieb) (1975) (Ultimate) (1.01) ACDC - Devil Girl (Stern) (2012) (Ultimate) (1.0) Addams Family, The (Bally) (1992) (Ultimate) (1.02) Air Aces (Bally) (1975) (1.0) Aliens Legacy (Original) (2011) (Ultimate Edition) (1.02) Apollo 13 (Sega) (1995) (1a) Atlantis (Bally) (1989) (WIP) Attack From Mars ULTIMATE 1.02 Austin Powers (Stern) (2001) (1.0) Avatar (Stern) (2010) (Ultimate Edition) (1.01) Back to the Future (Data East)(1990)(GLXB, SZA, francisco666, ramp model by rom)(1.0) Bally_Spectrum_1_0 Banzai Run (Williams) (1988) (WIP) Batman The Dark Knight (Stern) (2008) (UE) (1.04) Big Bang Bar (Capcom) (1996) (Physics 2,5) Big Ben (Williams) (1954) (1.1) Big Guns (Williams) (1987) (Ultimate) (1.01) Big Indian (Gottlieb) (1974) (1.50) BigBangBar 2015 Black Pyramid (Bally) (1984) (1.0) Blue Vs Pink (Original) (1.0) Bond 50 (Anniversary Edition) (1.0) Bram Stoker's Dracula (Williams) (1993) (1.0) Bubble Bobble (Original) (1.0) Centaur (Bally) (1981) (Ultimate Edition) (1.01) Centigrade 37 (Gottlieb) (1977) (UE) (1.02) Chamber Of Chills (Original) (2014) (1.0) Checkpoint (Data East) (1991) (1.1) Classic Panic (Original) (1.0) Close Encounters Of The Third Kind Cosmic Gunfight (Williams) (1982) (1.1) Cow Poke (Gottlieb) (1965) (3.0) Creature From The Black Lagoon (Bally) (1992) (1.2) Cross Country (Bally) (1963) (1.01) Cyclone (Williams) (1988) (Ultimate) (1.02) Dakar (Game Plan) (1988) (1.0) Dark Quest (Original) (1.0 Holo Fix) Dawn Of The Dead -

Adventuring with Books: a Booklist for Pre-K-Grade 6. the NCTE Booklist

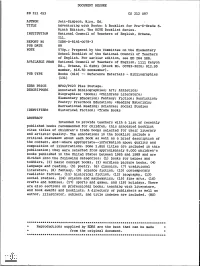

DOCUMENT RESUME ED 311 453 CS 212 097 AUTHOR Jett-Simpson, Mary, Ed. TITLE Adventuring with Books: A Booklist for Pre-K-Grade 6. Ninth Edition. The NCTE Booklist Series. INSTITUTION National Council of Teachers of English, Urbana, Ill. REPORT NO ISBN-0-8141-0078-3 PUB DATE 89 NOTE 570p.; Prepared by the Committee on the Elementary School Booklist of the National Council of Teachers of English. For earlier edition, see ED 264 588. AVAILABLE FROMNational Council of Teachers of English, 1111 Kenyon Rd., Urbana, IL 61801 (Stock No. 00783-3020; $12.95 member, $16.50 nonmember). PUB TYPE Books (010) -- Reference Materials - Bibliographies (131) EDRS PRICE MF02/PC23 Plus Postage. DESCRIPTORS Annotated Bibliographies; Art; Athletics; Biographies; *Books; *Childress Literature; Elementary Education; Fantasy; Fiction; Nonfiction; Poetry; Preschool Education; *Reading Materials; Recreational Reading; Sciences; Social Studies IDENTIFIERS Historical Fiction; *Trade Books ABSTRACT Intended to provide teachers with a list of recently published books recommended for children, this annotated booklist cites titles of children's trade books selected for their literary and artistic quality. The annotations in the booklist include a critical statement about each book as well as a brief description of the content, and--where appropriate--information about quality and composition of illustrations. Some 1,800 titles are included in this publication; they were selected from approximately 8,000 children's books published in the United States between 1985 and 1989 and are divided into the following categories: (1) books for babies and toddlers, (2) basic concept books, (3) wordless picture books, (4) language and reading, (5) poetry. (6) classics, (7) traditional literature, (8) fantasy,(9) science fiction, (10) contemporary realistic fiction, (11) historical fiction, (12) biography, (13) social studies, (14) science and mathematics, (15) fine arts, (16) crafts and hobbies, (17) sports and games, and (18) holidays. -

Gottlieb 1971) VP 9 Table 3 24 (Stern 2009

No. Table Name Table Type 1 12 Days Christmas VPX Table 2 2001 (Gottlieb 1971) VP 9 Table 3 24 (Stern 2009) VP 9 Table 4 250cc (Inder 1992) VP 9 Table 5 4 Roses (Williams 1962) VP 9 Table 6 4 Square (Gottlieb 1971) VP 9 Table 7 Aaron Spelling (Data East 1992) VP 9 Table 8 Abra Ca Dabra (Gottlieb 1975) VP 9 Table 9 ACDC (Stern 2012) VP 9 Table 10 ACDC Pro - PM5 (Stern 2012) PM5 Table 11 ACDC Pro (Stern 2012) VP 9 Table 12 Addams Family Golden (Williams 1994) VP 9 Table 13 Adventures of Rocky and Bullwinkle and Friends (Data East VP1993) 9 Table 14 Aerosmith Future Table 15 Agents 777 (GamePlan 1984) VP 9 Table 16 Air Aces (Bally 1975) VP 9 Table 17 Airborne (Capcom 1996) VP 9 Table 18 Airborne Avenger (Atari 1977) VP 9 Table 19 Airport (Gottlieb 1969) VP 9 Table 20 Aladdin's Castle (Bally 1976) VP 9 Table 21 Alaska (Interflip 1978) VP 9 Table 22 Algar (Williams 1980) VP 9 Table 23 Ali (Stern 1980) VP 9 Table 24 Ali Baba (Gottlieb 1948) VP 9 Table 25 Alice Cooper Future Table 26 Alien Poker (Williams 1980) VP 9 Table 27 Alien Star (Gottlieb 1984) VP 9 Table 28 Alive! (Brunswick 1978) VPX Table 29 Alle Neune (NSM 1976) VP 9 Table 30 Alley Cats (Williams 1985) VP 9 Table 31 Alpine Club (Williams 1965) VP 9 Table 32 Al's Garage Band Goes On World Tour (Alivin G. 1992) VP 9 Table 33 Amazing Spiderman (Gottlieb 1980) VP 9 Table 34 Amazon Hunt (Gottlieb 1983) VP 9 Table 35 America 1492 (Juegos Populares 1986) VP 9 Table 36 Amigo (Bally 1973) VP 9 Table 37 Andromeda (GamePlan 1985) VP 9 Table 38 Animaniacs SE Future Table 39 Antar (Playmatic 1979) -

Gottlieb Run Outrages Lancman

LocaL cLassifieds inside April 15, 2012 Your Neighborhood — Your News® Renaissance Gottlieb run outrages Lancman turns LIC into Accusations fly among Democrats as fourth enters congressional race prime location seeking a spot in the Democratic And then the finger pointing Gottlieb, who he called a “long- By Joe ANutA primary for a Queens congres- began. time party hack,” as a sham can- By ReBecca HeNely sional seat, state Assemblyman Lancman accused the didate. After word spread that Jeff Rory Lancman (D-Fresh Mead- Queens County Democrats and “Today, the Meng campaign The opening of JetBlue’s new Gottlieb, a 70-year-old employee of ows) said it was a ploy to siphon state Assemblywoman Grace has been caught red-handed in office and a new park in Long Is- the state Board of Elections, was votes away from him. Meng’s campaign of propping up one of the most malicious schemes land City last week was hailed as any of us have ever seen: an outra- a milestone for the community by geous ploy to deceive Jewish vot- leaders around the city, but the Pl a y Ba l l ! ers with a fraudulent candidate neighborhood has been growing designed to manipulate the elec- and changing for some time. toral process in her favor,” said After years of being known Lancman’s campaign manager, as a manufacturing mecca, Long Mark Benoit. Island City has become one of Lancman contends that Jew- Queens’ most up-and-coming ish voters will pull the lever for communities. Gottlieb just be- Its million-dollar views of cause of his Jew- Manhattan ish last name, have attract- Full coverage taking away ed residential votes the assem- development, PAGES 18,19 blyman believes would otherwise the hotel in- go to him.