MICRONAS VPC 3205C, VPC 3215C Video Processor Family

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

HDMI to Composite/S-Video Scaler

HDMI to Composite/S-Video Scaler Features* • Supported input resolutions: • 480i@60Hz • 576i@50Hz • 480p@60Hz • 576p@50Hz • 720p@50/60Hz • 1080i@50/60Hz • 1080p@50/60Hz • 640x480@60Hz • 800x600@60Hz • 1024x768@60Hz • 1280x1024@60Hz • 1600x1200@60Hz • Converts and scales HDMI to Composite/S-Video at 480i/60 or 576i/50 GTV-HDMI-2-COMPSVIDSN • De-embeds audio from HDMI and outputs it as digital and analog audio • Accepts HDMI video at resolutions up to 1080p Full HD Converts HDMI source to Composite and S-Video with • Supports both NTSC and PAL formats scaling • Underscan/Overscan Switch helps optimize image size on old analog TV screens without over-cropping or visible black borders Convert any Hi-Def source to standard definition NTSC/PAL format • Field upgradable firmware via USB port with scaling. The HDMI to analog video scaler supports resolutions up to 1080p Full HD video and scaled outputs in Composite and Specifications* S-Video, while maintaining the original aspect ratio for optimal viewing. The coax S/PDIF digital audio and left/right analog audio • Maximum Pixel Clock: 225 MHz outputs allow the audio extracted from the HDMI signal to be sent • Video Input Connector: (1) HDMI Type A, 19-pin, female, locking to any AV Receiver or audio amplifier. Underscan/Overscan and • Video Output Connectors: (1) Composite, RCA-type, female NTSC/PAL switches help assure compatibility with a variety of (1) S-Video, female analog televisions. This scaler also features a USB port for firmware • Audio Output Connectors: (1) L/R analog audio (2 x RCA-type, female) upgrades. -

LC-32/37RA1E Operation-Manual GB

LC-32RA1E LC-37RA1E ENGLISH C790WJZZ LC-32RA1E OPERATION MANUAL / BEDIENUNGSANLEITUNG / MODE D’EMPLOI / MANUALE DI ISTRUZIONI / GEBRUIKSAANWIJZING / MANUAL DE MANEJO LC-37RA1E DEUTSCH LCD COLOUR TELEVISION LCD-FARBFERNSEHGERÄT TÉLÉVISION COULEUR À ÉCRAN À CRISTAUX LIQUIDES (LCD) FRANÇAIS TELEVISORE A COLORI LCD LCD-KLEURENTELEVISIE TELEVISIÓN EN COLOR LCD ITALIANO OPERATION MANUAL BEDIENUNGSANLEITUNG MODE D’EMPLOI MANUALE DI ISTRUZIONI GEBRUIKSAANWIJZING MANUAL DE MANEJO NEDERLANDS ESPAÑOL Printed in Spain Gedruckt in Spanien Imprimé en Espagne Printed on environmentally friendly paper Stampato in Spagna Auf ökologischem Papier gedruckt Gedrukt in Spanje Imprimé sur papier écologique Impreso en España Stampato su carta ecologica Afgedrukt op ecologisch papier PIN TINS-C790WJZZ Impreso en papel ecológico 06P11-SP-NG 1 LC-32RA1E / LC-37RA1E ( ) : LC-32RA1E [ ] : LC-37RA1E : LC-32RA1E LC-37RA1E (506.0) / [542.0] (506,0) / [542,0] (796.4) / [920.0] (83.9) / [100.0] (115.1) / [115.9] (796,4) / [920,0] (83,9) / [100,0] (115,1) / [115,9] (700.4) / [823.0] (700,4) / [823,0] (532.1) / [600.0] (532,1) / [600,0] (589.6) / [657.0] (589,6) / [657,0] (395.1) / [464.0] (395,1) / [464,0] (343.0) / [377.0] (343,0) / [377,0] SPECIAL NOTE FOR USERS IN THE U.K. (250.0) / [291.4] (250,0) / [291,4] The mains lead of this product is fitted with a non-rewireable (moulded) plug incorporating a 13A fuse. Should the fuse need to be replaced, a BSI or ASTA approved BS 1362 fuse marked or ASA and of the same rating 200.0 as above, which is also indicated on the pin face of the plug, must be used. -

LED TV in Some Locations) Turns the TV on and Off

Getting Started Plug & Play Connections Remote Control When you turn the TV on for the first time, a sequence of on-screen prompts will assist in configuring basic settings. Press thePOWER ✎ This remote control has Braille points on the Power, Channel, and Volume buttons and can be used by visually impaired persons. y For better picture and audio quality, connect to a digital device using an HDMI cable. y PC(D-Sub) and PC/DVI AUDIO IN input are not supported. Accessories button. Plug & Play is available only when the Input source is set to y The picture may not display normally (if at all) or the audio may not work if an external y For HDMI/DVI cable connection, you must use the HDMI IN 1(DVI) port. TV. device that uses an older version of HDMI mode is connected to the TV. If such a problem • Remote Control & Batteries (AAA x 2) • Holder-Wire stand occurs, ask the manufacturer of the external device about the HDMI version and, if out of y Connecting through the HDMI cable may not be supported depending on the PC. • Owner’s Instructions • Power Cord ✎ Connecting the power cord and antenna. (refer to date, request an upgrade. y If an HDMI to DVI cable is connected to the HDMI IN 1(DVI) port, the audio does not work. • Warranty Card / Safety Guide (Not available ‘Connections’) y Be sure to purchase a certified HDMI cable. Otherwise, the picture may not display or a y Service: Connector for service only. Displays and selects the available video connection error may occur. -

FDS1703-ABK Your Advantages

17" Video surveillance systems FDS1703-ABK Your advantages The 17-inch FDS1703-ABK with a traditional 5:4 aspect ratio stands out thanks to its signal inputs designed for video secur- High image quality for a better view ity systems. Its HDMI input supports resolutions right through to Display with a high brightness level Full HD. A composite (BNC) input allows analogue video surveil- lance devices like cameras and recorders to be connected. The PC (HDMI) and analogue video input FDS1703-ABK provides support for PAL, SECAM and NTSC sig- NTSC/PAL/SECAM support nal formats. Overscan and normal display Two-year guarantee for 24/7 operation 17" Video surveillance systems Features Variety of interfaces for PC and video Reduced Noise and Flicker An HDMI input is available for connecting to computers to re- Thanks to its Y/C separation, the monitor offers images free from ceive signals from a digital source, such as an HDD recorder. noise and flickering. During Y/C separation, the luminance sig- There is a composite (BNC) input for connecting analogue video nal (Y) and chrominance signal (C), i.e. the brightness and col- surveillance equipment and surveillance cameras. The monitor our information from the image signal, are separated, preventing supports NTSC, PAL and SECAM signals. overlap artifacts. In addition, the monitor displays 16,77 million colours clearly and vividly. Built-in loudspeaker for PC and video Two build-in 0.5 W stereo speakers ensure good tone rendering. The loudspeakers support both PC and video sources. 24/7 use guaranteed The monitor is built for 24-hour use and is impressively reliable. -

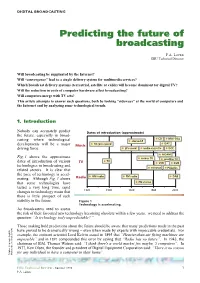

Predicting the Future of Broadcasting

DIGITAL BROADCASTING Predicting the future of broadcasting P.A. Laven EBU Technical Director Will broadcasting be supplanted by the Internet? Will “convergence” lead to a single delivery system for multimedia services? Which broadcast delivery systems (terrestrial, satellite or cable) will become dominant for digital TV? Will the reduction in costs of computer hardware affect broadcasting? Will computers merge with TV sets? This article attempts to answer such questions, both by looking “sideways” at the world of computers and the Internet and by analyzing some technological trends. 1. Introduction Nobody can accurately predict Dates of introduction (approximate) the future, especially in broad- CD Mini-Disc casting where technological stereo LP DAT developments will be a major Music 78 rpm record driving force. LP record audio cassette DCC NICAM Fig. 1 shows the approximate colour TV satellite TV TV dates of introduction of various TV VCR DVB technologies in broadcasting and teletext PALplus related sectors. It is clear that the pace of technology is accel- AM radio FM radio DAB erating. Although Fig. 1 shows Radio that some technologies have FM stereo lasted a very long time, rapid changes in technology mean that 1920 1940 1960 1980 2000 there is little prospect of such stability in the future. Figure 1 Technology is accelerating. As broadcasters need to assess the risk of their favoured new technology becoming obsolete within a few years, we need to address the question: “Is technology truly unpredictable? ” Those making bold predictions about the future should be aware that many predictions made in the past have proved to be dramatically wrong – even when made by experts with impeccable credentials. -

Imagine the Most Advanced Evolution of Color Projection on the Planet

Specifications SP-A800B Display Device Texas Instruments DMD, single chip, 1920 x1080 Screen Format 16:9 System NTSC n AV-NTSC (VIT) n PAL/SECAM n Power Supply 100V~240V, 50 Hz – 60 Hz AC Picture Brightness (Marketing value) 1000 ANSI Lumens Contrast Ratio (Marketing value) 10,000:1 (Full on/off) imagine the most advanced evolution Lamp Type 300W Philips UHP Lamp Life 2000 Hours of color projection on the planet. Dynamic Black n Reference Color Temp. 6500K Samsung SP-A800B Color Temp. Variation 5500K/6500K/8000K/9300K Resolution 1920 x 1080 1080p Full HD Home Theater Projector Scan System Progressive (1080p) 3D Y/C Comb n Digital N/R n 3 to 2 Pull Down n Functions PC Input Multi Mode Blue Screen n Multi Language English/German/Spanish/Dutch/French/Italian/Portuguese/Chinese/Swedish/Korean DTV Ready Input: 1080p/1080i/720p/576p/576i/480p/480i Multi Format Full/Zoom1/Zoom2/Wide Fit/4:3 Picture Mode 7 (Dynamic/Standard/Movie1~2/User1~3) LED Lamp Off n Lens Focus Manual Lens Shift Manual (vertical only) Zoom Lens Manual Throw Ratio 1.72~2.24 Image Size (inches) 40" to 300" H-Sync Range 15.0 - 80.0kHz V-Sync Range 48 - 100Hz Fan Noise 24 dBA Theater mode, 30 dBA Bright mode Remote Type TM-90 Terminal Rear Input HDMI 2 Composite In 1 S-Video 1 Component 2 (1080p/1080i/720p/576p/576i/480p/480i) PC (D-sub 15-Pin) 1 RS-232C (S/W Upgrade+Function control) 1 Dimensions 18" x 8.5" x 19" Video Processing Weight 21.6 lbs. -

TP19DB Data Sheet

MMooddeelll TTPP1199DDBB DDaayyBBrriiittee 19" DayBrite Professional Video Monitor with Scan Reverse • High & Standard Definition Video LCD Monitor 1080/720/576/480 • 3G SDI with loop out, HDMI • Analog inputs are Composite, PC-VGA • Modes: EGA to WUXGA, NTSC/PAL/SECAM/NTSC4.43/PAL-M • 10-bit Digital Processing (up to 1920 X 1200), 16.7 million true colors, 24 bit • Aspect Ratios: 16:9, 4:3, 1.85 to 1, etc. Presets and Adjustable • Fully Adjustable Scans: H & V sizes, Overscan / Underscan, Reverse Scan • Digital Adaptive Comb Filters SPECIFICATIONS Active Area (Diagonal): 19.0" MODES High & Standard Definition Video Modes: 1080/720/576/480 @23/24/25/29/30/60 i/p/sF Digital and Analog (autoselected), VESA VGA & DVI PC Video Modes: EGA, VGA, SVGA, XGA, WXGA, SXGA, WSXGA, UXGA, WUXGA Standard Definition Video Modes: NTSC/PAL/SECAM/NTSC4.43/PAL-M (autoselected) INPUTS Digital Video Inputs: 3G / HD / SD SDI (SMPTE 259M/292/296), HD HDMI Analog Video Inputs: Composite, PC VGA (EIA, CCIR, VESA, SMPTE 274) PICTURE Aspect Ratios: 16:9, 4:3, Letterbox, and (de-) Anamorphic, FiXed and Variable Aspect Ratio Images PiXel (RGB Trio) Arrangement: 1280 H X 1024 V RGB Vertical Stripe (983.040 PiXels, 15:9/1.667:1) PiXel (RGB Trio) Pitch, Depth: 0.294 H X 0.294 V mm, 16.7 million colors (10 bit digital processing) Brightness, typical, 0°: 1500 nts (cd/m2) Contrast Ratio, 0°: 1500:1 (high contrast) Color Bit Depth: 16.7 million colors (10-bit Digital Processing) Viewing Angle, contrast>10:1 : 170° H, 160° V (extreme wide view) Response Time: 5 ms (high -

Integrated High Definition LED Television User's Guide

Leading Innovation Integrated High Definition LED Television User’s Guide: 23L1350U 23L2300U 29L1350U 32L2300U 32L1350U 39L2300U 39L1350U 50L2300U 50L1350U 58L1350U If you need assistance: Toshiba’s Support Web site support.toshiba.com For more information, see “Troubleshooting” on page 108 in this guide. Owner’s Record The model number and serial number are on the back and side of your TV. Record these numbers in the spaces below. Refer to these numbers whenever you communicate with your Toshiba dealer about this TV Model number: ___________________________________ Serial number: ___________________________________ Note: To display a High Definition picture, the TV must be receiving a High Definition signal (such as an over-the-air High Definition TV broadcast, a High Definition digital GMA300018011 cable program, or a High Definition digital satellite program). For details, contact your TV antenna installer, 06/13 cable provider, or satellite provider 2 Dear Customer, WARNING Thank you for purchasing this Toshiba LED TV. This To prevent injury, this apparatus must be securely document will help you use the many exciting features attached to the floor/wall in accordance with the of your new LED TV. Before operating your LED TV, installation instructions. See item 26) on page 5 . carefully read this manual completely. WARNING: If you decide to wall mount this Safety Precautions television, always use a mounting bracket that has WARNING: TO REDUCE THE RISK OF FIRE been Listed by an independent laboratory (such as OR ELECTRIC SHOCK, DO NOT EXPOSE THIS UL, CSA, ETL) and is appropriate for the size and APPLIANCE TO RAIN OR MOISTURE. weight of this television. -

EBU Guidelines for Consumer Flat Panel Displays (Fpds)

EBU – TECH 3321 EBU guidelines for Consumer Flat Panel Displays (FPDs) Source: P/Display Status: Technical Specification Geneva September 2007 1 Page intentionally left blank. This document is paginated for recto-verso printing Tech 3321 EBU guidelines for Consumer Flat Panel Displays (FPDs) Contents 1. Scope............................................................................................................ 5 2. Background..................................................................................................... 5 3. Main technical parameters .................................................................................. 5 3a Luminance ................................................................................................... 5 3b Black level ................................................................................................... 6 3c Contrast...................................................................................................... 6 3d Frame rate presentation .................................................................................. 6 3e Digital interface (DVI or HDMI) coding range .......................................................... 6 3f HDMI AVI InfoFrame ........................................................................................ 6 4. Recommended “EBU default” settings .................................................................... 7 4a Display gamma .............................................................................................. 7 4b Colour -

NTSC Specifications

NTSC Modulation Standard ━━━━━━━━━━━━━━━━━━━━━━━━ The Impressionistic Era of TV. It©s Never The Same Color! The first analog Color TV system realized which is backward compatible with the existing B & W signal. To combine a Chroma signal with the existing Luma(Y)signal a quadrature sub-carrier Chroma signal is used. On the Cartesian grid the x & y axes are defined with B−Y & R−Y respectively. When transmitted along with the Luma(Y) G−Y signal can be recovered from the B−Y & R−Y signals. Matrixing ━━━━━━━━━ Let: R = Red \ G = Green Each range from 0 to 1. B = Blue / Y = Matrixed B & W Luma sub-channel. U = Matrixed Blue Chroma sub-channel. U #2900FC 249.76° −U #D3FC00 69.76° V = Matrixed Red Chroma sub-channel. V #FF0056 339.76° −V #00FFA9 159.76° W = Matrixed Green Chroma sub-channel. W #1BFA00 113.52° −W #DF00FA 293.52° HSV HSV Enhanced channels: Hue Hue I = Matrixed Skin Chroma sub-channel. I #FC6600 24.29° −I #0096FC 204.29° Q = Matrixed Purple Chroma sub-channel. Q #8900FE 272.36° −Q #75FE00 92.36° We have: Y = 0.299 × R + 0.587 × G + 0.114 × B B − Y = −0.299 × R − 0.587 × G + 0.886 × B R − Y = 0.701 × R − 0.587 × G − 0.114 × B G − Y = −0.299 × R + 0.413 × G − 0.114 × B = −0.194208 × (B − Y) −0.509370 × (R − Y) (−0.1942078377, −0.5093696834) Encode: If: U[x] = 0.492111 × ( B − Y ) × 0° ┐ Quadrature (0.4921110411) V[y] = 0.877283 × ( R − Y ) × 90° ┘ Sub-Carrier (0.8772832199) Then: W = 1.424415 × ( G − Y ) @ 235.796° Chroma Vector = √ U² + V² Chroma Hue θ = aTan2(V,U) [Radians] If θ < 0 then add 2π.[360°] Decode: SyncDet U: B − Y = -┼- @ 0.000° ÷ 0.492111 V: R − Y = -┼- @ 90.000° ÷ 0.877283 W: G − Y = -┼- @ 235.796° ÷ 1.424415 (1.4244145537, 235.79647610°) or G − Y = −0.394642 × (B − Y) − 0.580622 × (R − Y) (−0.3946423068, −0.5806217020) These scaling factors are for the quadrature Chroma signal before the 0.492111 & 0.877283 unscaling factors are applied to the B−Y & R−Y axes respectively. -

LCD Television Users Guide

LCD Television Users Guide LT-42X579 42" class (42" Diagonal) LT-47X579 47" class (46.9" Diagonal) LT-52X579 52" class (52” Diagonal) LT-42EM59 42" class (42" Diagonal) LT-47EM59 47" class (46.9" Diagonal) LT-52EM59 52" class (52” Diagonal) 1080p HDTV Important Note: In the spaces below, enter the model and serial number of your television (located at the rear of the television cabinet). Staple your sales receipt or invoice to the inside cover of this guide. Keep this user’s guide in a convenient place for future reference. Keep the carton and original packaging for future use. Serial Number: LCT2387-002A-A Model Number: 0708TSH-II-IM Table of Contents Warnings . 3 Add Channel . 31 Precautions . 6 Edit Channel . 31 V-Chip . 31 Remote Control . 10 Guide . 31 TV Basic Controls . 12 TV (V-Chip) . 32 Password . 33 Setup . 16 MPAA . 33 Initial Setup . 16 Can. Eng. 34 Key Features . 18 Can. Fre. 35 TVPG . 36 Remote Control Functions . 19 Sleep . 19 Sound . 37 Return+ TV . 19 MTS . 37 Favorite . 19 Digital Audio (ML) . 37 Aspect . 20 Surround . 37 Sound . 20 Sound Status . 38 Video . 20 Audio Reset . 38 Guide . 21 Power . 39 SUB CH . 21 Sleep Timer . 39 ML/MTS . 21 Power Indicator . 39 Customizing your TV . 22 Setting . 40 Picture . 23 Plug-In Menu . 40 Video Status . 23 Time Zone . 40 Color Temp . 24 D.S.T. 40 Color Management . 24 Language . 40 Dynamic Gamma . 24 Noise Mute . 40 Smart Picture . 25 Front Panel Lock . 41 Digital VNR . 25 Transparency . 41 MPEG NR . 25 Auto Shut Off . -

SAA7114 PAL/NTSC/SECAM Video Decoder with Adaptive PAL/NTSC Comb filter, VBI Data Slicer and High Performance Scaler Rev

SAA7114 PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC comb filter, VBI data slicer and high performance scaler Rev. 03 — 17 January 2006 Product data sheet 1. General description The SAA7114 is a video capture device for applications at the image port of Video Graphics Array (VGA) controllers. The SAA7114 is a combination of a two-channel analog preprocessing circuit including source selection, anti-aliasing filter and Analog-to-Digital Converter (ADC), an automatic clamp and gain control, a Clock Generation Circuit (CGC), a digital multistandard decoder containing two-dimensional chrominance/luminance separation by an adaptive comb filter and a high performance scaler, including variable horizontal and vertical up and downscaling and a brightness, contrast and saturation control circuit. It is a highly integrated circuit for desktop video and similar applications. The decoder is based on the principle of line-locked clock decoding and is able to decode the color of PAL, SECAM and NTSC signals into ITU 601 compatible color component values. The SAA7114 accepts CVBS or S-video (Y/C) as analog inputs from TV or VCR sources, including weak and distorted signals. An expansion port (X port) for digital video (bidirectional half duplex, D1 compatible) is also supported to connect to MPEG or a video phone codec. At the so called image port (I port) the SAA7114 supports 8-bit or 16-bit wide output data with auxiliary reference data for interfacing to VGA controllers. The target application for the SAA7114 is to capture and scale video images, to be provided as a digital video stream through the image port of a VGA controller, for display via the frame buffer of the VGA, or for capture to system memory.