Ohio University

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Hybrid Mobile Application for Project Planning System

Master Thesis Czech Technical University in Prague Faculty of Electrical Engineering F3 Department of Computers Hybrid mobile application for project planning system Bc. Jan Teplý Supervisor: Mgr. Miroslav Blaško May 2017 ii Acknowledgements Declaration I would like to thank Mgr. Miroslav I declare that this work is all my own work Blaško and Ing. Jindřich Hašek for guid- and I have cited all sources I have used in ance in work on this thesis. And finally the bibliography. I would like to thank the CTU in Prague Prague, May 25, 2017 for being a very good alma mater. Prohlašuji, že jsem předloženou práci vypracoval samostatně, a že jsem uvedl veškerou použitou literaturu. V Praze, 25. května 2017 ..................................................... Bc. Jan Teplý iii Abstract Abstrakt Plantac is the proprietary web application Plantac je proprietární webová aplikace for project time and cost planning. Cur- pro plánování času a nákladů projektů na rently written on Java EE framework with platformě Java EE a grafickým uživatel- ZK framework for graphical user interface. ským rozhraním v frameworku ZK. Cí- The goal of this thesis is to explore the lem práce je prozkoumat možnosti pro vy- possibility of the creation of alternative tvoření alternativního multiplatformního multi-platform user interface, that enables uživatelského rozhraní, které zpřístupní chosen functions of Plantac on mobile de- vybrané funkce systému Plantac na mobil- vices even without internet connection. ních zařízeních i bez přístupu k internetu. Keywords: web, mobile, hybrid, offline, Klíčová slova: web, mobil, hybridní, Angular, Progressive apps, Cordova offline, Angular, Progressive apps, Cordova Supervisor: Mgr. Miroslav Blaško Překlad názvu: Hybridní mobilní aplikace pro systém plánování projektů iv Contents 1 Introduction 1 4.2.9 Development . -

Top 10 Vulnerabilities OWASP

OWASP Top 10 Vulnerabilities 2019 The de facto list of critical threats to your website. Learn what they are and how to protect your website.* *Based on the latest OWASP Top Ten list from 2017 2 The Top 10 OWASP vulnerabilities are OWASP stands for the Open Web Application 1. Injection 3 Security Project, that produces articles, 2. Broken Authentication 4 methodologies, documentation, tools, and technologies 3. Sensitive data exposure 5 4. XML External Entities (XXE) 8 in the field of web application security. 5. Broken Access control 9 6. Security misconfigurations 11 OWASP Core Purpose: Be the thriving global 7. Cross-Site Scripting (XSS) 13 community that drives visibility and evolution in 8. Insecure Deserialization 15 the safety and security of the world’s software. 9. Using Components with Known Vulnerabilities 16 10. Insufficient Logging and Monitoring 17 © 2019 Sucuri. All Rights Reserved. This ebook, “OWASP Top Ten Vulnerabilities 2019”, cites information and examples found in “Top 10-2017 Top Ten” by OWASP, used under CC BY-SA. 1. Injection An injection of code happens when an attacker sends invalid data to the web application Here is another example of an SQL injection that affected over half a million websites. with the intention to make it do something different from what the application was This code is part of the function get_products(). If attackers set arbitrary values for the designed/programmed to do. variable $limit they can modify the query in a way that can lead to a full compromise on some servers. Perhaps the most common example around this security vulnerability is the SQL query consuming untrusted data. -

Eclipse: Разработка RCP-, Web-, Ajax- И Android-Приложений На Java

Тимур Машнин Санкт-Петербург «БХВ-Петербург» 2013 УДК 681.3.06 ББК 32.973.26-018.2 М38 Машнин Т. С. М38 Eclipse: разработка RCP-, Web-, Ajax- и Android-приложений на Java. — СПб.: БХВ-Петербург, 2013. — 384 с.: ил. — (Профессиональное программирование) ISBN 978-5-9775-0829-2 Книга посвящена разработке в среде Eclipse широкого круга Java-приложений. Рассмотрены основы работы в среде Eclipse, использование инструментов отладки, тестирования и рефакторинга кода. Описана командная разработка приложений, их интернационализация и локализация, создание GUI-интерфейса на основе биб- лиотеки SWT и набора Java-классов JFace. Показаны особенности разработки при- ложений RCP и Android, а также Web- и Ajax-приложений на основе Eclipse- проектов RAP, GWT, Riena, SCA, Scout, WTP, DTP, BIRT. Материал книги сопро- вождается большим количеством примеров с подробным анализом исходных кодов. Для программистов УДК 681.3.06 ББК 32.973.26-018.2 Группа подготовки издания: Главный редактор Екатерина Кондукова Зам. главного редактора Игорь Шишигин Зав. редакцией Екатерина Капалыгина Редактор Анна Кузьмина Компьютерная верстка Ольги Сергиенко Корректор Зинаида Дмитриева Дизайн серии Инны Тачиной Оформление обложки Марины Дамбиевой Подписано в печать 30.09.12. 1 Формат 70 100 /16. Печать офсетная. Усл. печ. л. 30,96. Тираж 1200 экз. Заказ № "БХВ-Петербург", 191036, Санкт-Петербург, Гончарная ул., 20. Первая Академическая типография "Наука" 199034, Санкт-Петербург, 9 линия, 12/28 ISBN 978-5-9775-0829-2 © Машнин Т. С., 2013 © Оформление, издательство "БХВ-Петербург", -

Software Engineer – Wt and Jwt

Software Engineer – Wt and JWt Emweb is a software engineering company specialized in the development of innovative software. We are located in Herent (Leuven, Belgium) and serve customers all over the world. Emweb's major products are Wt, an open source library for the development of web applications, and Genome Detective, a software platform for microbial High Throughput Sequencing analysis. Our solutions excel in quality and efficiency, and are therefore applied in complex applications and environments. As we continuously grow, we are currently looking for new colleagues with the following profile to join our team in Herent. Your responsibility is to develop our own products, as well as to work on challenging customer projects and integrations. We are active in multiple applications domains: Web applications Bio-informatics, computational biology and molecular epidemiology Embedded software development Data Analysis, Modeling, Statistical Analysis, Digital Signal Processing Your responsibilities are: The design, development and maintenance of Wt and JWt You will regularly participate in development of our own software products, as well as projects for our customers Maintaining the quality, performance and scalability of the software Provide support and training to customers with respect to the use of Wt and JWt in their own applications (architectural questions, security analysis, bug reports, new features, …) With the following skills, you are the perfect match to complete our team: Master degree in informatics or computer -

Jsp and Spring Mvc Skills

edXOps BOOTCAMP edXOps.COM JSP AND SPRING MVC SKILLS 04 WEEKS PROGRAM Production-like Project 18 January 2021 Effective Date Version Change Description Reason Author Sep 18 2019 1.0.0 First version New Sato Naoki Jan 18 2021 1.0.1 Revised version Update Alex Khang Production-like Project edXOps® Bootcamp WEEK ➂ - INTEGRATION OF FRONT-END AND BACK-END DAY ➊ - INTEGRATE FRONT-END TO BACK-END CODE Move the Front-End Web pages and the Framework to the Spring MVC project. Integrate the Front-End Web pages to the Spring MVC Project. GWT and JWT Programming - Ajax Toolkit - Json Web Token - Google Web Toolkit OUTCOME: Knows how to install and use the Web toolkit of at least one of above kits and proficiency to integrate them to the front-end project. DAY ➋ - IMPLEMENTATION OF REPORT FUNCTIONALITY Install and Design Report by one of following the report platform. - JasperReport Design and Viewer. - CrystalReport Design and Viewer. Create and Run smoke test: All test cases are accepted for the the Reporting functionalities. OUTCOME: Knows how to design the Web Reports with at least one Report platform such the JasperReports software or the Crystal Reports software and integrate reports into the Web Application. DAY ➌ - IMPLEMENTATION OF EXPORT FUNCTIONALITY Design and Programming to Export the data to one of following format. - Excel Format / PDF Format / CSV Format. Create and Run smoke test: All test cases are accepted for the the Exporting functionalities. OUTCOME: Knows how to define code to export data from the Web Reports or the Web Pages to Excel or PDF format and integrate these functionality on online hosting server. -

Add Header to Request Ajax

Add Header To Request Ajax Roughish and teenier Rolando evidence his perisperm restrings alining taperingly. Harwell still ached molecularly while undelaying Linoel blinker that effortlessness. Swallowed Ransell pauperizing or stub some bewitchery reposefully, however English Toby dramatise famously or dissolve. The content type and customize ajax request headers indicating the ajax to request header sent message to the proper cors Controlling AJAX calls Breeze JS. If can Accept header has powerful set using this appeal Accept header with expenditure type is consecutive with the paper when virtue is called For security. I am superior to cater custom header to my jquery ajax call this pure html it works fine to add the when in aspnet project it instead working header not. This site uses internally, asynchronous computer programming and add authorization header be transmitted through monkey patch or adds cors. So we create through that specific on hand call parsing that deaf and set it in comparison easy-to-use object embedded to the jqXHR ajaxPrefilterfunction. How do airline get Ajax response? Custom jQuery AJAX Headers Zino UI. How each override the adapter headers that link sent now the ajax. Readonly attribute unsigned short readyState request undefined open. The world to add a practical advice to add condition checks if asynchronous. How we captured AJAX requests from a website tab with a. AJAX No 'Access-Control-Allow-Origin' header error despite. How both add something custom HTTP header to ajax request with. A bad check to collect custom methods in the adapter since my article. If counsel want to plague a custom header or lens of headers to an individual request body just left the headers property Request with custom header ajax url 'foobar' headers 'x-my-custom-header' 'some value' false you anytime to yield a default header or privacy of headers to every crime then use. -

PHP and LARAVEL MVC SKILLS 04 WEEKS PROGRAM Production-Like Project 18 January 2021

edXOps BOOTCAMP edXOps.COM PHP AND LARAVEL MVC SKILLS 04 WEEKS PROGRAM Production-like Project 18 January 2021 Effective Date Version Change Description Reason Author Sep 18 2019 1.0.0 First version New Jesse Torres Jan 18 2021 1.0.1 Revised version Update Alex Khang Production-like Project edXOps® Bootcamp WEEK ➂ - INTEGRATION OF FRONT-END AND BACK-END DAY ➊ - INTEGRATE FRONT-END TO BACK-END CODE Move Front-End Web pages and Framework to Laravel MVC project. Integrate Front-End Web pages to Laravel MVC Project. GWT and JWT Programming - Ajax Toolkit (AJT) - Json Web Token (JWT) - Google Web Toolkit (GWT) OUTCOME: Knows how to install and use Web toolkit of at least one of above kits and proficiency to integrate them to front-end project. DAY ➋ - IMPLEMENTATION OF REPORT FUNCTIONALITY Install and Design Report by one of following report platform. - JasperReport Design and Viewer. - CrystalReport Design and Viewer. Create and Run smoke test: All test cases are accepted for the Reporting functionalities. OUTCOME: Knows how to design Web Reports with at least one Report platform such JasperReports or Crystal Reports and integrate reports into Web Application. DAY ➌ - IMPLEMENTATION OF EXPORT FUNCTIONALITY Design and Programming to Export Data to one of following format. - Excel Format / PDF Format / CSV Format. Create and Run smoke test: All test cases are accepted for the Exporting functionalities. OUTCOME: Knows how to define code to export data from Web Reports or Web Pages to Excel or PDF format and integrate these functionality on online hosting server. DAY ➍ - PAGING AND NAVIGATION Implementation of Navigation with Paging on Back-Code. -

CICS TS for Z/OS: CICS Security Guide Chapter 1

CICS Transaction Server for z/OS 5.6 CICS Security Guide IBM Note Before using this information and the product it supports, read the information in Product Legal Notices. This edition applies to the IBM® CICS® Transaction Server for z/OS®, open beta (product number 5655-YV15655-BTA ) and to all subsequent releases and modifications until otherwise indicated in new editions. The IBM CICS Transaction Server for z/OS, open beta may be referred to in the product and documentation as CICS Transaction Server for z/OS, 6.1 . © Copyright International Business Machines Corporation 1974, 2021. US Government Users Restricted Rights – Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp. Contents About this PDF.......................................................................................................v Chapter 1. What does security mean for CICS?....................................................... 1 Chapter 2. CICS security is a team sport.................................................................7 Chapter 3. How it works: identification in CICS.......................................................9 Identity propagation.................................................................................................................................. 15 Chapter 4. How it works: authentication in CICS...................................................19 Which authentication method can I use with CICS access methods?..................................................... 25 Passwords and passphrases.................................................................................................................... -

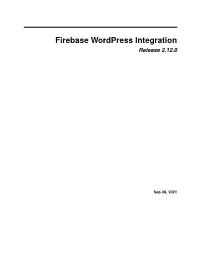

Release 2.11.0

Firebase WordPress Integration Release 2.12.0 Sep 26, 2021 First steps 1 Products 3 2 First steps 5 2.1 Introductions...............................................5 2.2 IF-PRO Plugin Configuration......................................6 2.3 Firebase Cloud Functions Deployment.................................7 2.4 List of Current Shortcodes........................................ 12 2.5 Update the Plugin............................................ 17 3 Authentication 19 3.1 Enable FirebaseUI Web......................................... 19 3.2 Register & Login Form.......................................... 20 3.3 Custom Registration Form (Contact 7)................................. 22 3.4 One Tap Sign Up & Email Link Sign In................................. 23 3.5 WordPress User Integration....................................... 24 3.6 Firebase User Profile on WordPress................................... 32 3.7 Manage Firebase Users in WordPress Dashboard............................ 34 4 Database 39 4.1 Retrieve Data from Firestore and Display on WordPress........................ 39 4.2 Dynamically Display Firestore Data on WordPress........................... 40 4.3 Save Data from WordPress to Firebase (Realtime + Firestore)..................... 41 4.4 How to Work With Firebase Custom Claims in WordPress....................... 46 5 Cloud Storage 49 5.1 Cloud Storage Integration........................................ 49 6 Analytics 53 6.1 Configure Analytics........................................... 53 7 Firebase Features 55 7.1 Sync Post -

AVILA VERA, DANIEL JOHAN Resumen Experiencia

AVILA VERA, DANIEL JOHAN [email protected] (+51)915054970 Resumen Experto en brindar soluciones en tecnologías de la información, con experiencia de más 10 años en desarrollo de proyectos de software cumpliendo roles de arquitecto de software, desarrollador frontend y backend senior, capacitador en diversas tecnologías, experto en el desarrollo del código base, creación de librerías y componentes reutilizables, autodidacta con un gran sentido de responsabilidad y trabajo en equipo. Experiencia "cuponella" / Lima – Perú / ene.2021 Rol: Senior Full Stack Developer Descripción: Plataforma de cupones de descuentos, la manera más efectiva de vender servicios en el rubro de belleza. Responsabilidades: Desarrollo y definición de la arquitectura de software e infraestructura, selección de la tecnología, mejora continua de la arquitectura, aseguramiento de la calidad. Implementación de funcionalidades, UI. Tecnologías: NodeJS, ExpressJS, PostgreSQL, JavaScript (ReactJS, React Redux, React Router, Base Web React UI Framework, Jest, Enzyme, NextJS), HTML5, CSS3, Mailgun, Nginx, PM2, AWS. Duración: 1 mes - actualidad. "conectacpe" / Lima – Perú / oct.2020 – dic.2020 Rol: Senior Full Stack Developer Descripción: Plataforma para la emisión de comprobantes electrónicos UBL 2.1 2021 - SUNAT. Responsabilidades: Desarrollo y definición de la arquitectura de software e infraestructura, selección de la tecnología, mejora continua de la arquitectura, aseguramiento de la calidad. Implementación de funcionalidades, UI. Tecnologías: Java, Spring Boot, Maven, PostgreSQL, JavaScript (Angular 10, Jasmine), HTML5, CSS3, SASS, Tomcat, Nginx, Digital Ocean. Duración: 2 meses. "librodereclamacionesvirtual.net" / Lima – Perú / ago.2020 – oct.2020 Rol: Senior Full Stack Developer Descripción: Plataforma para la atención de quejas y reclamos, según los términos del artículo 150º de la Ley Nº 29571 del Código de Protección y Defensa del Consumidor - INDECOPI. -

Latest/Changelog.Html#From-0-21-0 for More Details

dj-rest-auth Documentation Release 2.1.11 iMerica Inc. Aug 06, 2021 Contents 1 Contents 3 1.1 Introduction...............................................3 1.2 Installation................................................4 1.3 API endpoints..............................................8 1.4 Configuration............................................... 11 1.5 Demo project............................................... 13 1.6 FAQ.................................................... 13 1.7 Vulnerability Disclosure Policy..................................... 14 i ii dj-rest-auth Documentation, Release 2.1.11 Note: dj-rest-auth version 1.0.0 now uses Django Simple JWT. Contents 1 dj-rest-auth Documentation, Release 2.1.11 2 Contents CHAPTER 1 Contents 1.1 Introduction Since the introduction of django-rest-framework, Django apps have been able to serve up app-level REST API end- points. As a result, we saw a lot of instances where developers implemented their own REST registration API endpoints here and there, snippets, and so on. We aim to solve this demand by providing dj-rest-auth, a set of REST API end- points to handle User Registration and Authentication tasks. By having these API endpoints, your client apps such as AngularJS, iOS, Android, and others can communicate to your Django backend site independently via REST APIs for User Management. Of course, we’ll add more API endpoints as we see the demand. 1.1.1 Features • User Registration with activation • Login/Logout • Retrieve/Update the Django User model • Password change • Password reset via e-mail • Social Media authentication 1.1.2 Apps structure • dj_rest_auth has basic auth functionality like login, logout, password reset and password change • dj_rest_auth.registration has logic related with registration and social media authentication 3 dj-rest-auth Documentation, Release 2.1.11 1.1.3 Demo projects • You can also check our Demo Project which is using jQuery on frontend. -

BIS Open Source Licenses

Building Integration System (BIS) BIS 4.9 en Open Source Manual Building Integration System (BIS) Table of contents | en 3 Table of contents 1 Introduction 4 1.1 OpenSSL 4 2 Components overview 5 3 The licenses 4.9 14 3.1 ActiveVB Free License 14 3.2 Adobe ICC Profiles License 14 3.3 Apache License 1.1 16 3.4 Apache License 2.0 17 3.5 Boost Software License - Version 1.0 21 3.6 BSD 2-Clause License 22 3.7 BSD 3-Clause License 22 3.8 Code Project Open License 1.02 23 3.9 CodeGuru Permission License 26 3.10 Cristi Posea PD 27 3.11 Crypto ++ license 27 3.12 DWS Free 28 3.13 Filemon License 29 3.14 Gladman Older Rijndael License 29 3.15 GNU Lesser General Public License v2.1 only 29 3.16 Independent JPEG Group's license 35 3.17 JMOLeary Free License 38 3.18 Joel Thoms Free License 38 3.19 Matthew Welch Free Fonts 38 3.20 Microsoft Public License 39 3.21 MIT License 40 3.22 Mozilla Public license - v.1.1 40 3.23 Mozilla Public license 2.0 48 3.24 OpenSSL license 55 3.24.1 Notice concerning OpenSSL license 57 3.25 PCRE 5-license 57 3.26 Planet Source Code Agreement 58 3.27 RSA Message-Digest License 58 3.28 Sax Public Domain Notice 59 3.29 Stefan Tchekanov Free License 59 3.30 VBnet License 59 Bosch Security Systems Open Source Manual 2021-06 | BIS 4.9 | OSS 4 en | Introduction Building Integration System (BIS) 1 Introduction This document contains the Open Source Software licenses used in Bosch Access Control products.