Chisel – Accelerating Hardware Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Paul Sellers' Workbench Measurements and Cutting

PAUL SELLERS’ WORKBENCH MEASUREMENTS AND CUTTING LIST PAUL SELLERS’ WORKBENCH MEASUREMENTS AND CUTTING LIST NOTE When putting together the cutting list for my workbench, I worked in imperial, the system with which I am most comfortable. I was not happy, however, to then provide direct conversions to metric because to be accurate and ensure an exact fit this would involve providing measurements in fractions of millimetres. When I do work in metric I find it more comfortable to work with rounded numbers, therefore I have created two slightly different sets of measurements. This means that in places the imperial measurement given is not a direct conversion of the metric measurement given. Therefore, I suggest you choose one or other of the systems and follow it throughout. © 2017 – Paul Sellers v2 PAUL SELLERS’ WORKBENCH MEASUREMENTS AND CUTTING LIST WOOD QTY DESCRIPTION SIZE (IMPERIAL) SIZE (METRIC) (THICK X WIDE X LONG) (THICK X WIDE X LONG) 4 Leg 2 ¾” x 3 ¾” x 34 ⅜” 70 x 95 x 875mm 1 Benchtop 2 ⅜” x 12” x 66” 65 x 300 x 1680mm 2 Apron 1 ⅝” x 11 ½” x 66” 40 x 290 x 1680mm 1 Wellboard 1” x 12 ½” x 66” 25 x 320 x 1680mm 4 Rail 1 ½” x 6” x 26” 40 x 150 x 654mm 2 Bearer 1 ¼” x 3 ¾” x 25” 30 x 95 x 630mm 4 Wedge ⅝” x 1 ½” x 9” 16 x 40 x 228mm 4 Wedge retainer ⅝” x 1 ½” x 4” 16 x 40 x 100mm HARDWARE QTY DESCRIPTION SIZE (IMPERIAL) SIZE (METRIC) 1 Vise 9” 225mm Dome head bolts (including nuts and washers) for 4 ⅜” x 5” 10 x 130mm bolting legs to aprons 2 Lag screws (with washers) for underside of vise ½” x 2 ½” 12 x 65mm 2 Lag screws for face -

Stanley CE Certified Products Catalog

Selection, Innovation, CE CERTIFIED Performance PRODUCT Your One-Stop Shop for Hydraulic Tools CATALOG and Attachments CE TOOLS CATALOG INDEX About Hydraulic Tools . 1-2 Breakers . 2-4 Chipping Hammer . 5 Augers . 5 Tamper Drills . 6 Grinders . 7 Hammer Drills . 8 Impact Drills . 9 Impact Wrenches . 10 Diamond Chainsaws . 11 Chainsaw & Cutoff Saw Water Pump . 11 Utility Chain saw . 12 Cutoff Saw . 12 Sump Pumps . 13 Trash Pumps . 14 GREAT BRAND, GREAT TOOLS Power Units . 15 STANLEY has a proud tradition of being a global leader in the development of a wide range of innovative hydraulic products used in a variety of industries and Suggested Carrier Ranges . 16 applications throughout the world. As a proud member of STANLEY Black & Decker, a 175 year old company committed to the manufacture and distribution of quality tools for the professional, industrial, and consumer, we at Stanley Infrastructure are dedicated to providing our customers with innovative customer-driven product Profile Grinders . 16 designs, world class quality, unmatched product support, and superior value. Track Jacks . 17 GLOBAL REPRESENTATION Weld Shear . 17 STANLEY Infrastructure produces an extensive line of products for use in construction, demolition, scrap processing, recycling, utilities, municipalities, railroads, Rail Saw . 18 industry, landscaping, underwater, construction, and specialty trades. STANLEY Infrastructure Tools has sales offices and distributors throughout North America, Central America, South America, Europe, Asia, Australia, and the Middle East. Rail Drill . 18 Hydraulic System Requirements . 19-20 OUR MISSION STANLEY is committed to providing innovative solutions for infrastructure based applications. We are for those who make the world move. B www.stanleyinfrastructure.com 833.723.1843 833.723.1843 www.stanleyinfrastructure.com C CE TOOLS CE TOOLS SERIES BR BREAKERS Nothing equals the impact force of hydraulic-powered breakers. -

Instruction Manual Read Instructions Before Operating This Tool

SDS4 HAMMER DRILL Instruction Manual Read instructions before operating this tool. G10100 www.evolutionfury.com SDS4 HAMMER DRILL EC - DECLARATION OF CONFORMITY SDS HAMMER DRILL FIG 1 FIG 2 EC - DECLARATION OF CONFORMITY GB Congratulations on your purchase of an Evolution Power We, the importer Tools SDS4 4 Function Hammer Drill. Please complete Evolution Power Tools Ltd. your product registration on line to validate your machine’s Venture One warranty period and ensure prompt service if needed. We Longacre Close sincerely thank you for selecting a product from Evolution Sheffield Power Tools. S20 3FR WARRANTY GB Declare that the product Part numbers: ZIC-SD6A-20 12 MONTH LIMITED WARRANTY. Evolution power tools Evolution: SDS4 reserves the right to make improvements and modifications SDS 4 Function Hammer Drill to design without prior notice. Complies with the essential requirements of the following Evolution Power Tools will, within twelve (12) months from European Directives: the original date of purchase, repair or replace any goods 2006/42/EC – Machine Directive found to be defective in materials or workmanship. This 2006/95/EC – Low Voltage Directive warranty is void if the tool being returned has been used 2004/108/EC – EMC Directive to drill / chisel materials beyond the recommendations 2002/95/EC – Restriction of the use of Certain Hazardous in the Instruction Manual or if the drill has been damaged Substances in Electrical and Electric Equipment by accident, neglect, or improper service. This warranty does not apply to machines and / or components which Standards and Technical specifications referred to:- have been altered, changed, or modified in any way, or EN 55014-1:2006 subjected to use beyond recommended capacities and EN 55014-2/A1:2001 specifications. -

Sds Hammers Sds Plus / Sds Max

THE COMPLETE RANGE SDS HAMMERS SDS PLUS / SDS MAX www.metabo.com/uk SDS PLUS HAMMERS SDS PLUS HAMMERS KHA 18 LTX Cordless Hammer n Vario (V)-electronics for working with customised speeds for the materials used Metabo’s powerful SDS Plus hammers are always the right choice when it comes to processing n Metabo S-automatic torque limiting clutch: mechanical decoupling of the hard materials such as concrete or stone. The pneumatic hammer mechanism delivers high- drive if the drill jams for safe working energy impacts that allow for low fatigue working with high productivity. n Ultra-M technology for highest performance, gentle charging, optimum energy utilisation and long service life All Metabo SDS Plus hammers come as standard with the renowned S-automatic mechanical safety clutch for maximum machine and operator safety, should the drill or chisel become stuck the S-automatic safety clutch disengages the motor from the drive which not only prevents kick-back but also ensures your machine does not stall and burn-out, therefore increasing the service life of your Metabo. Machines equipped with our die-cast aluminium housings provide the highest longevity and performance with a strong mounted hammer mechanism which is resistant to the harshest of mechanical loads, robust protection from the working environment and efficient heat dissipation therefore prolonging the service life of your Metabo. The enormous power combined with user-optimised ergonomics and safety make the Metabo hammers your perfect choice of tool when working in demanding applications. For added piece of mind, Metabo offers you a 3 year XXL warranty on your investment when Battery pack voltage 18 V registered with 4 weeks of purchase. -

Simple Machines

Name: _______________________________________ Simple Machines There are six basic types of simple machines: inclined plane, wedge, screw, wheel and axle, lever, and pulley. 1. What is the man doing with the crow bar? Which type of simple machine is he using? ____________________________________________________________ ____________________________________________________________ ____________________________________________________________ ____________________________________________________________ 2. Why might this woman be drilling a hole? Which type of simple machine will she probably insert in the hole when she's done drilling? ____________________________________________________________ ____________________________________________________________ ____________________________________________________________ ____________________________________________________________ 6. What is this man doing? What type of simple machine is the ladder that he is standing on? ____________________________________________________________ ____________________________________________________________ ____________________________________________________________ ____________________________________________________________ Super Teacher Worksheets - www.superteacherworksheets.com 4. What might the woman doing with the cord, wheel and hook? Which basic simple machine is she using? ____________________________________________________________ ____________________________________________________________ ____________________________________________________________ -

Hollow Chisel Mortiser

User Manual Read and understand this manual before using machine. HOLLOW CHISEL MORTISER Model Number 25200 ® CUS STEEL CITY TOOL WORKS Manual Part No. OR71593 VER. 2.07 THANK YOU for purchasing your new Steel City Hollow Chisel Mortiser. This mortiser has been designed, tested, and inspected with you, the customer, in mind. When properly assembled, used and maintained, your mortiser will provide you with years of trouble free service, which is why it is backed by one of the longest machinery warranties in the business. This mortiser is just one of many products in the Steel City’s family of woodworking machinery and is proof of our commitment to total customer satisfaction. At Steel City we continue to strive for excellence each and every day and value the opinion of you, our customer. For comments about your mortiser or Steel City Tool Works, please visit our web site at www.steelcitytoolworks.com . 2 TABLE OF CONTENTS INTRODUCTION SECTION 1 Warranty .................................................................................................................................................4 SECTION 2 Product Specifications ............................................................................................................................7 SECTION 3 Accessories and Attachments ................................................................................................................7 SECTION 4 Definition of Terms..................................................................................................................................7 -

1. Hand Tools 3. Related Tools 4. Chisels 5. Hammer 6. Saw Terminology 7. Pliers Introduction

1 1. Hand Tools 2. Types 2.1 Hand tools 2.2 Hammer Drill 2.3 Rotary hammer drill 2.4 Cordless drills 2.5 Drill press 2.6 Geared head drill 2.7 Radial arm drill 2.8 Mill drill 3. Related tools 4. Chisels 4.1. Types 4.1.1 Woodworking chisels 4.1.1.1 Lathe tools 4.2 Metalworking chisels 4.2.1 Cold chisel 4.2.2 Hardy chisel 4.3 Stone chisels 4.4 Masonry chisels 4.4.1 Joint chisel 5. Hammer 5.1 Basic design and variations 5.2 The physics of hammering 5.2.1 Hammer as a force amplifier 5.2.2 Effect of the head's mass 5.2.3 Effect of the handle 5.3 War hammers 5.4 Symbolic hammers 6. Saw terminology 6.1 Types of saws 6.1.1 Hand saws 6.1.2. Back saws 6.1.3 Mechanically powered saws 6.1.4. Circular blade saws 6.1.5. Reciprocating blade saws 6.1.6..Continuous band 6.2. Types of saw blades and the cuts they make 6.3. Materials used for saws 7. Pliers Introduction 7.1. Design 7.2.Common types 7.2.1 Gripping pliers (used to improve grip) 7.2 2.Cutting pliers (used to sever or pinch off) 2 7.2.3 Crimping pliers 7.2.4 Rotational pliers 8. Common wrenches / spanners 8.1 Other general wrenches / spanners 8.2. Spe cialized wrenches / spanners 8.3. Spanners in popular culture 9. Hacksaw, surface plate, surface gauge, , vee-block, files 10. -

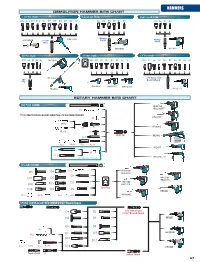

HAMMERS DEMOLITION HAMMER BITS CHART 1-1/8” Hex Shank Makita Large Shank Makita Small Shank D15 D14 D13 D12 D9 D7 D5 D4 D3 D2 D1 D7 D5 D4 D3 D2 D1 D10 D8 D3 D1

HAMMERS DEMOLITION HAMMER BITS CHART 1-1/8” Hex Shank Makita Large Shank Makita Small Shank D15 D14 D13 D12 D9 D7 D5 D4 D3 D2 D1 D7 D5 D4 D3 D2 D1 D10 D8 D3 D1 Makita HM1304B HM1810 Large Makita 1-1/8” Small Hex HM1500 HK1810 SDS Plus Shank SDS Max Shank 3/4” Hex Shank D10 D8 D3 D2 D1 HK1820 D9 D7 D6 D5 D4 D3 D2 D1 D16 D11 D9 D7 D6 D5 D4 D3 D2 D1 SDS max HK1820L 3/4” Hex 21/32” SDS Round Shank Plus HM0860C HM1100C HM1202C HK0500 HM1211B ROTARY HAMMER BITS CHART SDS PLUS SHANK HR3210C R1 HR3210FCT R8 IS ADAPTER WHICH ALLOWS OLDER TOOLS TO USE DEMOLITION BITS R6 HR2811F Metal R3 R2 HR3000C Wood R4 SDS Plus HR2432 D1 R23c R23b R23 R23a HR2455 R9 R8 R10 HR2470F / FT HR160DWA & HR2400 only SDS MAX SHANK D4 R1a HR5210C D5 HR5211C D1 D11 D6 HR4010C SDS HR4011C D2 HR4510C D16 D15 max HR4511C SDS Max D18 D9 D3 HR4002 R24c R24b R24 R24a HR4500C SPLINE SHANK & 3/4” HEX SHANK 21/32” Round Shank D4 D2 3/4” HEX Shank 21/32” Round Shank D5 D3 HR3851 D8 D6 R6 D7 HR4040C R1b D1 D18 D17 R24a R24c R24b R24 D16 HR5000 Taper Shank R5 Spline Shank 67 HAMMERS DEMOLITION HAMMER BITS CHART Demolition Hammer Bits Chart HM1202C, HM1100C, HR3210C/FCT, HM0860C, HR5210C, HR3000C, HR2811F, HR5211C, HR4510C, HM1810C, HM1304B HM1500 HK1810 HR2455, HR2432, Model HR4511C, HR4500C, HR2470F/FT, HK1820, HR4010C, HR4011C, HK0500 HR4002 Ref. No. Description 1-1/8" Hex 3/4" Hex Makita Large Makita Small SDS Plus 3/4" Hex, 21/32" Round SDS Max Hex Shank Size Part No. -

The Leading Manufacturer of Forged Hand and Power Tools Accessories Since 1946

122806_A_AJAX_ATW-lisa 7/17/12 8:20 PM Page 1 The Leading Manufacturer of Forged Hand and Power Tools Accessories Since 1946 TM Phone: 800.323.9129 • Fax: 800.424.2529 122806_A_AJAX_r3.qxp_AJAX 7/25/12 11:59 AM Page 3 Phone: 800.323.9129 • Fax: 800.424.2529 www.ajaxtools.com ZIP GUN CHISELS & ACCESSORIES WELD FLUX CHISELS & ACCESSORIES CHIPPING HAMMER TOOLS & ACCESSORIES BERYLLIUM COPPER SAFETY TOOLS RIVET BUSTER TOOLS & ACCESSORIES PAVING BREAKER TOOLS DRILL STEEL TOOLS ELECTRIC HAMMER TOOLS RIGGER TOOLS HAND TOOLS WEDGES, LINE UP PINS & SCRAPERS DEMOLITION TOOLS TM Wear Safety Goggles 4 122806_A_AJAX_ATW-lisa 7/17/12 8:20 PM Page 5 23⁄8" 3 .495" 111⁄16" .495" 2 ⁄8" 60mm 51⁄64" 15⁄16" 60mm 13⁄4" 17 ⁄32" .485" 44.4mm .580" 15⁄32" .469" 14.7mm .576" .680" .680" .576" 17.2mm 17.2mm .812" .812" 3 3 20.6mm 2 ⁄8" 3⁄8" 13 9 20.6mm 23⁄8" ⁄8" 60.3mm ⁄16" ⁄16" .495" 19⁄32" 29⁄32" 9.5mm 9.5mm 60.3mm 3 4 1⁄2" sq. 1⁄4" 1⁄4" 1 ⁄ " .360" Ø .415" 44.4mm .580" .425" 1 14.7mm Ø .373" .576" 1 ⁄8" .680" 13⁄16" 11⁄8" 13⁄16" 28.5mm 17.2mm 20.6mm 28.5mm 20.6mm 21⁄2" 1 4 21⁄2" 11⁄4" 1 5 1 ⁄ " 3⁄8" 63.5mm 3 1 ⁄4" REF 1 ⁄64" 32mm 63.5mm 32mm ⁄8" .620" 9.5mm 13⁄4" 9.5mm .354" .919" 1" 3⁄8" .375" .610" 44.4mm 13 13 .576" .680" -

Chisel Quilts

1501 Easy Chisel Quilts REQUIRED GO! Baby Friendly Twelve Star Quilt Quilt 49” x 61” Finished Block SizeSize 11½”11½” Teresa Varnes Amie Potter Long Braid Tablee RunneRunnerr 14” x 102” Finished Width ooff BrBraidaid 6” Eleanor Burns Judy Jackson Medium Length Braid Table Runner 14” x 54” 2 Select from a Star Lap Robe or Braid Table Runer in two sizes featuring AccuQuilt® Die #55039 for Chisels. The Star also uses Die #55009 for Half Square Triangles. This die is #3 from the 6” Mix and Match series. The Chisel die cuts two shapes at a time. Chisels #55039 The Half Square Half Square Triangle Triangle die cuts four #55009 shapes at a time. Carefully follow cutting instructions, because they are not the same for both projects. Chisels for Star Lap Robe are cut from strips placed right side up. Chisels for Braid Table Runner are cut from strips placed wrong sides together in pairs. 3 Fabric Selection Decide on the theme or era of your projects, such as Civil War, Depression, Traditional, Modern, Juvenile, or Holiday. It's easy to select from a line that a designer put together in a variety of prints and solids, or ones that appear solid. A total of eighteen fat quar- ters is enough for both projects, including two Table Runners in the medium length. Select twelve medium to dark print fat quarters in a variety of values, colors, and scales. Select six Background prints in similar values but different textures that appear solid and do not distract from prints. Twelve Fat Quarters Six Backgrounds In additional, purchase fabric listed on page 5 for finishing your project. -

How to Make 'Condor Tails'

How to Make ‘Condor Tails’ BY JAMEEL ABRAHAM An ingenious way to combine routers, a band saw and hand tools for big dovetails. know what you’re thinking: “Another opinion on how to cut I dovetails.” I hear you. But this one’s different. I promise. No back and forth over pins or tails first. No Rob Cosman vs. Frank Klausz. Well, actually a little Klausz. When I built my first serious workbench in the 1990s I practically memorized Scott Landis’ “The Work- bench Book” (Taunton) and like many woodworkers I was attracted to Frank Klausz’s beautiful bench, especially the large, crisp dovetails that joined the parts of the tail vise. Klausz told us what tools he used to cut the joints, but didn’t elaborate much on technique. I suppose with a lifetime of skill at your command, you just pick up the tools and the joint emerges. I wanted the crisp look of Klausz’s joints without waiting 20 years to develop the skill. After build- ing several large benches over the past few years, this technique emerged. Best of Both Worlds I’m a big believer in making dovetail Enormous perfection. Cutting large-scale dovetails, such as for this workbench, can be a challenge. joints that fit right off the saw. That’s a This technique makes it straightforward. skill that’s easy to learn with some prac- tice. But not so with the beefy members of a workbench, or large-scale furni- railing just to get the thing vertical so where they excel. This is truly blended ture. -

Carlton Maintenance and Safety Manual

Maintenance and Safety Manual CARLTON® | Blount, Inc. Corporate Headquarters P.O. Box 22127 Portland, Oregon 97269-2127 USA carltonproducts.com 800-223-5168 © Copyright 2013 | Blount, Inc. | F/N 556740 Rev AA 3/13 An in-depth manual on saw chain theory, safety, maintenance instructions and troubleshooting for Carlton® saw chain, guide bars and drive sprockets Chain Saw Safety If you do not have experience and specialized training for dealing with chain saw kickback, then Carlton® urges you to use only low-kickback saw chains which have this green label: ATTENTION – READ THIS: The saw chain in this package is low kickback saw chain. It met the reduced kickback requirements of ANSI B175.1 and CSA Z62.3 when tested on a representative sample of chain saws. Its safety features significantly reduce the hazard of kickback while maintaining high cutting performance. ALL CUTTING SAW CHAINS CAN KICK BACK, which may result in severe personal injury to the chain saw operator or bystanders. Operate your chain saw safety. Read all warnings in your chain saw operator's manual. Part numbers Chain pitch .043"/1.1 mm .050"/1.3 mm .058"/1.5 mm .063"/1.6 mm gauge gauge gauge gauge 3/8" LP N4C-BL N1C-BL — — K1NK-BL, .325" — K2C-BL K3C-BL K1C-BL 3/8" — A1EP-GL A2EP-GL A3EP-GL Saw chains marked with a yellow label like the one below, are not low-kickback and are intended for use only by professional chain saw operators. ATTENTION – READ THIS: Warning: this saw chain may be capable of kickback that could result in serious injury to the chain saw operator or bystanders.