Accelerating Performance for Server-Side Java* Applications 2

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Real-Time Java for Embedded Devices: the Javamen Project*

REAL-TIME JAVA FOR EMBEDDED DEVICES: THE JAVAMEN PROJECT* A. Borg, N. Audsley, A. Wellings The University of York, UK ABSTRACT: Hardware Java-specific processors have been shown to provide the performance benefits over their software counterparts that make Java a feasible environment for executing even the most computationally expensive systems. In most cases, the core of these processors is a simple stack machine on which stack operations and logic and arithmetic operations are carried out. More complex bytecodes are implemented either in microcode through a sequence of stack and memory operations or in Java and therefore through a set of bytecodes. This paper investigates the Figure 1: Three alternatives for executing Java code (take from (6)) state-of-the-art in Java processors and identifies two areas of improvement for specialising these processors timeliness as a key issue. The language therefore fails to for real-time applications. This is achieved through a allow more advanced temporal requirements of threads combination of the implementation of real-time Java to be expressed and virtual machine implementations components in hardware and by using application- may behave unpredictably in this context. For example, specific characteristics expressed at the Java level to whereas a basic thread priority can be specified, it is not drive a co-design strategy. An implementation of these required to be observed by a virtual machine and there propositions will provide a flexible Ravenscar- is no guarantee that the highest priority thread will compliant virtual machine that provides better preempt lower priority threads. In order to address this performance while still guaranteeing real-time shortcoming, two competing specifications have been requirements. -

Zing:® the Best JVM for the Enterprise

PRODUCT DATA SHEET Zing:® ZING The best JVM for the enterprise Zing Runtime for Java A JVM that is compatible and compliant The Performance Standard for Low Latency, with the Java SE specification. Zing is a Memory-Intensive or Interactive Applications better alternative to your existing JVM. INTRODUCING ZING Zing Vision (ZVision) Today Java is ubiquitous across the enterprise. Flexible and powerful, Java is the ideal choice A zero-overhead, always-on production- for development teams worldwide. time monitoring tool designed to support rapid troubleshooting of applications using Zing. Zing builds upon Java’s advantages by delivering a robust, highly scalable Java Virtual Machine ReadyNow! Technology (JVM) to match the needs of today’s real time enterprise. Zing is the best JVM choice for all Solves Java warm-up problems, gives Java workloads, including low-latency financial systems, SaaS or Cloud-based deployments, developers fine-grained control over Web-based eCommerce applications, insurance portals, multi-user gaming platforms, Big Data, compilation and allows DevOps to save and other use cases -- anywhere predictable Java performance is essential. and reuse accumulated optimizations. Zing enables developers to make effective use of memory -- without the stalls, glitches and jitter that have been part of Java’s heritage, and solves JVM “warm-up” problems that can degrade ZING ADVANTAGES performance at start up. With improved memory-handling and a more stable, consistent runtime Takes advantage of the large memory platform, Java developers can build and deploy richer applications incorporating real-time data and multiple CPU cores available in processing and analytics, driving new revenue and supporting new business innovations. -

Java Performance Mysteries

ITM Web of Conferences 7 09015 , (2016) DOI: 10.1051/itmconf/20160709015 ITA 2016 Java Performance Mysteries Pranita Maldikar, San-Hong Li and Kingsum Chow [email protected], {sanhong.lsh, kingsum.kc}@alibaba-inc.com Abstract. While assessing software performance quality in the cloud, we noticed some significant performance variation of several Java applications. At a first glance, they looked like mysteries. To isolate the variation due to cloud, system and software configurations, we designed a set of experiments and collected set of software performance data. We analyzed the data to identify the sources of Java performance variation. Our experience in measuring Java performance may help attendees in selecting the trade-offs in software configurations and load testing tool configurations to obtain the software quality measurements they need. The contributions of this paper are (1) Observing Java performance mysteries in the cloud, (2) Identifying the sources of performance mysteries, and (3) Obtaining optimal and reproducible performance data. 1 Introduction into multiple tiers like, client tier, middle-tier and data tier. For testing a Java EE workload theclient tier would Java is both a programming language and a platform. be a load generator machine using load generator Java as a programming language follows object-oriented software like Faban [2]. This client tier will consist of programming model and it requires Java Virtual users that will send the request to the application server Machine (Java Interpreter) to run Java programs. Java as or the middle tier.The middle tier contains the entire a platform is an environment on which we can deploy business logic for the enterprise application. -

Performance Comparison of Java and C++ When Sorting Integers and Writing/Reading Files

Bachelor of Science in Computer Science February 2019 Performance comparison of Java and C++ when sorting integers and writing/reading files. Suraj Sharma Faculty of Computing, Blekinge Institute of Technology, 371 79 Karlskrona, Sweden This thesis is submitted to the Faculty of Computing at Blekinge Institute of Technology in partial fulfilment of the requirements for the degree of Bachelor of Science in Computer Sciences. The thesis is equivalent to 20 weeks of full-time studies. The authors declare that they are the sole authors of this thesis and that they have not used any sources other than those listed in the bibliography and identified as references. They further declare that they have not submitted this thesis at any other institution to obtain a degree. Contact Information: Author(s): Suraj Sharma E-mail: [email protected] University advisor: Dr. Prashant Goswami Department of Creative Technologies Faculty of Computing Internet : www.bth.se Blekinge Institute of Technology Phone : +46 455 38 50 00 SE-371 79 Karlskrona, Sweden Fax : +46 455 38 50 57 ii ABSTRACT This study is conducted to show the strengths and weaknesses of C++ and Java in three areas that are used often in programming; loading, sorting and saving data. Performance and scalability are large factors in software development and choosing the right programming language is often a long process. It is important to conduct these types of direct comparison studies to properly identify strengths and weaknesses of programming languages. Two applications were created, one using C++ and one using Java. Apart from a few syntax and necessary differences, both are as close to being identical as possible. -

Design and Analysis of a Scala Benchmark Suite for the Java Virtual Machine

Design and Analysis of a Scala Benchmark Suite for the Java Virtual Machine Entwurf und Analyse einer Scala Benchmark Suite für die Java Virtual Machine Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) genehmigte Dissertation von Diplom-Mathematiker Andreas Sewe aus Twistringen, Deutschland April 2013 — Darmstadt — D 17 Fachbereich Informatik Fachgebiet Softwaretechnik Design and Analysis of a Scala Benchmark Suite for the Java Virtual Machine Entwurf und Analyse einer Scala Benchmark Suite für die Java Virtual Machine Genehmigte Dissertation von Diplom-Mathematiker Andreas Sewe aus Twistrin- gen, Deutschland 1. Gutachten: Prof. Dr.-Ing. Ermira Mezini 2. Gutachten: Prof. Richard E. Jones Tag der Einreichung: 17. August 2012 Tag der Prüfung: 29. Oktober 2012 Darmstadt — D 17 For Bettina Academic Résumé November 2007 – October 2012 Doctoral studies at the chair of Prof. Dr.-Ing. Er- mira Mezini, Fachgebiet Softwaretechnik, Fachbereich Informatik, Techni- sche Universität Darmstadt October 2001 – October 2007 Studies in mathematics with a special focus on com- puter science (Mathematik mit Schwerpunkt Informatik) at Technische Uni- versität Darmstadt, finishing with a degree of Diplom-Mathematiker (Dipl.- Math.) iii Acknowledgements First and foremost, I would like to thank Mira Mezini, my thesis supervisor, for pro- viding me with the opportunity and freedom to pursue my research, as condensed into the thesis you now hold in your hands. Her experience and her insights did much to improve my research as did her invaluable ability to ask the right questions at the right time. I would also like to thank Richard Jones for taking the time to act as secondary reviewer of this thesis. -

Java (Software Platform) from Wikipedia, the Free Encyclopedia Not to Be Confused with Javascript

Java (software platform) From Wikipedia, the free encyclopedia Not to be confused with JavaScript. This article may require copy editing for grammar, style, cohesion, tone , or spelling. You can assist by editing it. (February 2016) Java (software platform) Dukesource125.gif The Java technology logo Original author(s) James Gosling, Sun Microsystems Developer(s) Oracle Corporation Initial release 23 January 1996; 20 years ago[1][2] Stable release 8 Update 73 (1.8.0_73) (February 5, 2016; 34 days ago) [±][3] Preview release 9 Build b90 (November 2, 2015; 4 months ago) [±][4] Written in Java, C++[5] Operating system Windows, Solaris, Linux, OS X[6] Platform Cross-platform Available in 30+ languages List of languages [show] Type Software platform License Freeware, mostly open-source,[8] with a few proprietary[9] compo nents[10] Website www.java.com Java is a set of computer software and specifications developed by Sun Microsyst ems, later acquired by Oracle Corporation, that provides a system for developing application software and deploying it in a cross-platform computing environment . Java is used in a wide variety of computing platforms from embedded devices an d mobile phones to enterprise servers and supercomputers. While less common, Jav a applets run in secure, sandboxed environments to provide many features of nati ve applications and can be embedded in HTML pages. Writing in the Java programming language is the primary way to produce code that will be deployed as byte code in a Java Virtual Machine (JVM); byte code compil ers are also available for other languages, including Ada, JavaScript, Python, a nd Ruby. -

Implementing Data-Flow Fusion DSL on Clojure

CORE Metadata, citation and similar papers at core.ac.uk Provided by Hosei University Repository Implementing Data-Flow Fusion DSL on Clojure 著者 SAKURAI Yuuki 出版者 法政大学大学院情報科学研究科 journal or 法政大学大学院紀要. 情報科学研究科編 publication title volume 11 page range 1-6 year 2016-03-24 URL http://hdl.handle.net/10114/12212 Implementing Data-Flow Fusion DSL on Clojure Yuuki Sakuraiy Graduate School of Computer and Information Sciences, Hosei University, Tokyo, Japan [email protected] Abstract—This paper presents a new optimization tech- Hand fusion is powerful and sometime the fastest way, nique for programming language Clojure based on the stan- but this causes the problems of lowering the readability of dard fusion technique that merges list operations into a code. The modified code is often ugly and error prone. simplified loop. Automated fusion prevents such kind of code degrada- Short-cut fusions, foldr/build fusion, and stream fusions are tion. However, automated fusion can be applied only to standard fusion techniques used in a functional programming. limited cases. Moreover, a recent fusion technique proposed by Lippmeier. Our approach is the middle way between automatic Data flow fusion [7] can fuse loops containing several data and manual. The user of our system first insert data-flow consumers over stream operators on Haskell. However, this is fusion macro manually into the code, and then the Clojure only for Haskell. Clojure’s transducers [2] are factory func- macro processor takes care of fusion based on the data-flow tions generating abstract list objects. The functions generated by them wait evaluation as a lazy evaluation partially. -

Java™ Performance

JavaTM Performance The Java™ Series Visit informit.com/thejavaseries for a complete list of available publications. ublications in The Java™ Series are supported, endorsed, and Pwritten by the creators of Java at Sun Microsystems, Inc. This series is the official source for expert instruction in Java and provides the complete set of tools you’ll need to build effective, robust, and portable applications and applets. The Java™ Series is an indispensable resource for anyone looking for definitive information on Java technology. Visit Sun Microsystems Press at sun.com/books to view additional titles for developers, programmers, and system administrators working with Java and other Sun technologies. JavaTM Performance Charlie Hunt Binu John Upper Saddle River, NJ • Boston • Indianapolis • San Francisco New York • Toronto • Montreal • London • Munich • Paris • Madrid Capetown • Sydney • Tokyo • Singapore • Mexico City Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals. Oracle and Java are registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners. AMD, Opteron, the AMD logo, and the AMD Opteron logo are trademarks or registered trademarks of Advanced Micro Devices. Intel and Intel Xeon are trademarks or registered trademarks of Intel Corporation. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC Inter- national, Inc. UNIX is a registered trademark licensed through X/Open Company, Ltd. -

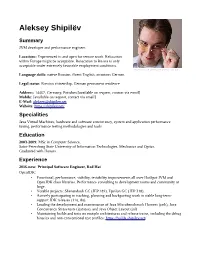

Aleksey Shipilev CV.Pdf

Aleksey Shipilëv Summary JVM developer and performance engineer. Locations: Experienced in and open for remote work. Relocation within Europe might be acceptable. Relocation to Russia is only acceptable under extremely favorable employment conditions. “Please read this CV carefully, there would be a quiz later” Language skills: native Russian, fluent English, atrocious German Legal status: Russian citizenship, German permanent residence Address: 14467, Germany, Potsdam [available on request, contact via email] Mobile: [available on request, contact via email] E-Mail: [email protected] Website: http s ://shipilev.net/ Specialities Java Virtual Machines, hardware and software concurrency, system and application performance tuning, performance testing methodologies and tools Education 2003-2009: MSc in Computer Science, Saint-Petersburg State University of Information Technologies, Mechanics and Optics. Graduated with Honors. Experience 2016-now: Principal Software Engineer, Red Hat OpenJDK: • Functional, performance, stability, testability improvements all over HotSpot JVM and OpenJDK class libraries. Performance consulting to development teams and community at large. • Notable projects: Shenandoah GC (JEP 189), Epsilon GC (JEP 318). • Actively participating in tracking, planning and backporting work in stable long-term- support JDK releases (11u, 8u). • Leading the development and maintenance of Java Microbenchmark Harness (jmh), Java Concurrency Stress tests (jcstress), and Java Object Layout (jol) • Maintaining builds and tests on -

Improving Energy Consumption of Java Programs

Wayne State University Wayne State University Dissertations January 2019 Improving Energy Consumption Of Java Programs Mohit Kumar Wayne State University Follow this and additional works at: https://digitalcommons.wayne.edu/oa_dissertations Part of the Computer Sciences Commons Recommended Citation Kumar, Mohit, "Improving Energy Consumption Of Java Programs" (2019). Wayne State University Dissertations. 2325. https://digitalcommons.wayne.edu/oa_dissertations/2325 This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState. IMPROVING ENERGY CONSUMPTION OF JAVA PROGRAMS by MOHIT KUMAR DISSERTATION Submitted to the Graduate School of Wayne State University, Detroit, Michigan in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY 2019 MAJOR: COMPUTER SCIENCE Approved by: Advisor Date ©COPYRIGHT BY Mohit Kumar 2019 All Rights Reserved ii DEDICATION This dissertation wouldn’t have been possible without the love, support, and care from my family. My mother (Usha Rani), who always nurture me with her positive thoughts. My father (Jagbir Singh), who always make sure that I had anything I needed. My sister (Sakshi), who always makes me laugh by reminiscing about happy memories. My wife (Namita), without whom I couldn’t have thought of starting it. iii ACKNOWLEDGMENTS My Ph.D. journey started in 2014 at Wayne State University. However, this journey became worthwhile when I joined MIST Lab in 2015. I would like to express my heartfelt thanks to Dr. Weisong Shi for accepting me as his Ph.D. student. His support and guidance helped me to work on various research projects. -

Mastering Clojure Macros Write Cleaner, Faster, Smarter Code

Extracted from: Mastering Clojure Macros Write Cleaner, Faster, Smarter Code This PDF file contains pages extracted from Mastering Clojure Macros, published by the Pragmatic Bookshelf. For more information or to purchase a paperback or PDF copy, please visit http://www.pragprog.com. Note: This extract contains some colored text (particularly in code listing). This is available only in online versions of the books. The printed versions are black and white. Pagination might vary between the online and printed versions; the content is otherwise identical. Copyright © 2014 The Pragmatic Programmers, LLC. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior consent of the publisher. The Pragmatic Bookshelf Dallas, Texas • Raleigh, North Carolina Mastering Clojure Macros Write Cleaner, Faster, Smarter Code Colin Jones The Pragmatic Bookshelf Dallas, Texas • Raleigh, North Carolina Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and The Pragmatic Programmers, LLC was aware of a trademark claim, the designations have been printed in initial capital letters or in all capitals. The Pragmatic Starter Kit, The Pragmatic Programmer, Pragmatic Programming, Pragmatic Bookshelf, PragProg and the linking g device are trade- marks of The Pragmatic Programmers, LLC. Every precaution was taken in the preparation of this book. However, the publisher assumes no responsibility for errors or omissions, or for damages that may result from the use of information (including program listings) contained herein. -

Exploring Performance Improvement for Java-Based Scientific Simulations

Exploring Performance Improvement for Java-based Scientific Simulations Xiaorong Xiang∗ Yingping Huang Gregory Madey Department of Computer Science and Engineering University of Notre Dame NotreDame, IN 46556 USA Telephone: 574-631-7596 Email:[email protected], [email protected], [email protected] Abstract and MacOS ) for their scientific studies. It is im- possible to deploy an application written in C, C++, There has been growing interest for using the Java or FORTRAN languages from one platform to the programming language in scientific and engineering other without rebuilding the application or changing applications. This is because Java offers several fea- the code. One of the most attractive features of Java tures, which other traditional languages (C, C++, is its portability, “write once, run anywhere.” Java andFORTRAN) lack, including portability, garbage runtime environment (JVM) provides an automatic collection mechanism, built-in threads, and the RMI garbage collection feature that reduces the burden of mechanism. However, the historic poor performance explicitly managing memory for programmer. The of Java stops it from being widely used in scientific Java built-in threads implementation and Java’s Re- applications. Although research and development on mote Method Invocation (RMI) mechanism make it Java resulting in JIT compilers, JVM improvement, easy for parallel computing and distributed comput- and high performance compilers, have been done ing. much for runtime environment optimization and sig- Although there are many attractive features pro- nificantly speeded up the Java programs, we still be- vided by the Java language and the J2EE architec- lieve that creating hand-optimized Java source code ture makes Java a potential language for scientific ap- andoptimizing code for speed, reliability, scalability, plications, performance remains a prime concern for andmaintainability are also crucial during program program developers using Java.