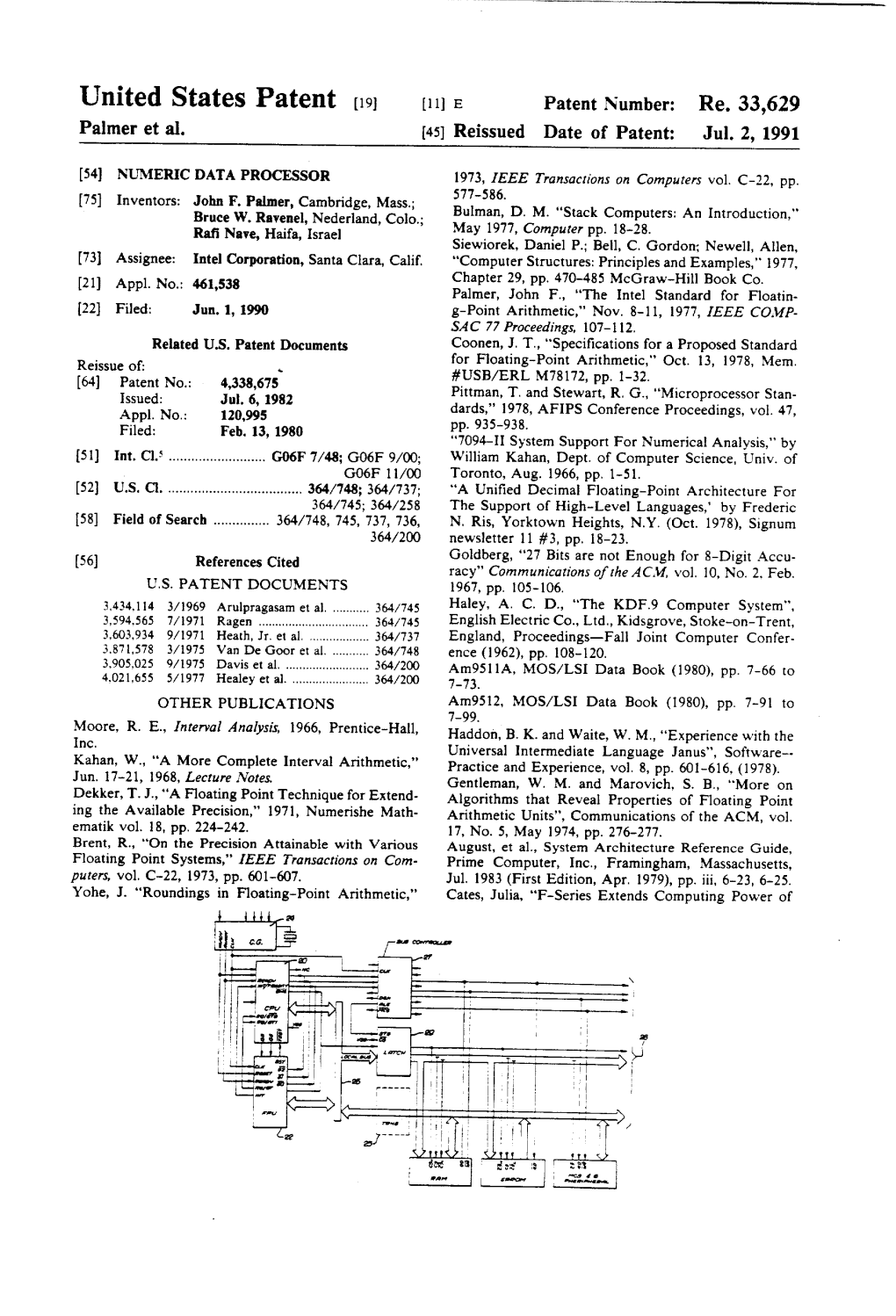

United States Patent [19] [11] E Patent Number: Re

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Faster Math Functions, Soundly

Faster Math Functions, Soundly IAN BRIGGS, University of Utah, USA PAVEL PANCHEKHA, University of Utah, USA Standard library implementations of functions like sin and exp optimize for accuracy, not speed, because they are intended for general-purpose use. But applications tolerate inaccuracy from cancellation, rounding error, and singularities—sometimes even very high error—and many application could tolerate error in function implementations as well. This raises an intriguing possibility: speeding up numerical code by tuning standard function implementations. This paper thus introduces OpTuner, an automatic method for selecting the best implementation of mathematical functions at each use site. OpTuner assembles dozens of implementations for the standard mathematical functions from across the speed-accuracy spectrum. OpTuner then uses error Taylor series and integer linear programming to compute optimal assignments of function implementation to use site and presents the user with a speed-accuracy Pareto curve they can use to speed up their code. In a case study on the POV-Ray ray tracer, OpTuner speeds up a critical computation, leading to a whole program speedup of 9% with no change in the program output (whereas human efforts result in slower code and lower-quality output). On a broader study of 37 standard benchmarks, OpTuner matches 216 implementations to 89 use sites and demonstrates speed-ups of 107% for negligible decreases in accuracy and of up to 438% for error-tolerant applications. Additional Key Words and Phrases: Floating point, rounding error, performance, approximation theory, synthesis, optimization 1 INTRODUCTION Floating-point arithmetic is foundational for scientific, engineering, and mathematical software. This is because, while floating-point arithmetic is approximate, most applications tolerate minute errors [Piparo et al. -

Version 0.2.1 Copyright C 2003-2009 Richard P

Modern Computer Arithmetic Richard P. Brent and Paul Zimmermann Version 0.2.1 Copyright c 2003-2009 Richard P. Brent and Paul Zimmermann This electronic version is distributed under the terms and conditions of the Creative Commons license “Attribution-Noncommercial-No Derivative Works 3.0”. You are free to copy, distribute and transmit this book under the following conditions: Attribution. You must attribute the work in the manner specified • by the author or licensor (but not in any way that suggests that they endorse you or your use of the work). Noncommercial. You may not use this work for commercial purposes. • No Derivative Works. You may not alter, transform, or build upon • this work. For any reuse or distribution, you must make clear to others the license terms of this work. The best way to do this is with a link to the web page below. Any of the above conditions can be waived if you get permission from the copyright holder. Nothing in this license impairs or restricts the author’s moral rights. For more information about the license, visit http://creativecommons.org/licenses/by-nc-nd/3.0/ Preface This is a book about algorithms for performing arithmetic, and their imple- mentation on modern computers. We are concerned with software more than hardware — we do not cover computer architecture or the design of computer hardware since good books are already available on these topics. Instead we focus on algorithms for efficiently performing arithmetic operations such as addition, multiplication and division, and their connections to topics such as modular arithmetic, greatest common divisors, the Fast Fourier Transform (FFT), and the computation of special functions. -

Unitary and Symmetric Structure in Deep Neural Networks

University of Kentucky UKnowledge Theses and Dissertations--Mathematics Mathematics 2020 Unitary and Symmetric Structure in Deep Neural Networks Kehelwala Dewage Gayan Maduranga University of Kentucky, [email protected] Author ORCID Identifier: https://orcid.org/0000-0002-6626-9024 Digital Object Identifier: https://doi.org/10.13023/etd.2020.380 Right click to open a feedback form in a new tab to let us know how this document benefits ou.y Recommended Citation Maduranga, Kehelwala Dewage Gayan, "Unitary and Symmetric Structure in Deep Neural Networks" (2020). Theses and Dissertations--Mathematics. 77. https://uknowledge.uky.edu/math_etds/77 This Doctoral Dissertation is brought to you for free and open access by the Mathematics at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Mathematics by an authorized administrator of UKnowledge. For more information, please contact [email protected]. STUDENT AGREEMENT: I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained needed written permission statement(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine) which will be submitted to UKnowledge as Additional File. I hereby grant to The University of Kentucky and its agents the irrevocable, non-exclusive, and royalty-free license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. -

Alan Mathison Turing and the Turing Award Winners

Alan Turing and the Turing Award Winners A Short Journey Through the History of Computer TítuloScience do capítulo Luis Lamb, 22 June 2012 Slides by Luis C. Lamb Alan Mathison Turing A.M. Turing, 1951 Turing by Stephen Kettle, 2007 by Slides by Luis C. Lamb Assumptions • I assume knowlege of Computing as a Science. • I shall not talk about computing before Turing: Leibniz, Babbage, Boole, Gödel... • I shall not detail theorems or algorithms. • I shall apologize for omissions at the end of this presentation. • Comprehensive information about Turing can be found at http://www.mathcomp.leeds.ac.uk/turing2012/ • The full version of this talk is available upon request. Slides by Luis C. Lamb Alan Mathison Turing § Born 23 June 1912: 2 Warrington Crescent, Maida Vale, London W9 Google maps Slides by Luis C. Lamb Alan Mathison Turing: short biography • 1922: Attends Hazlehurst Preparatory School • ’26: Sherborne School Dorset • ’31: King’s College Cambridge, Maths (graduates in ‘34). • ’35: Elected to Fellowship of King’s College Cambridge • ’36: Publishes “On Computable Numbers, with an Application to the Entscheindungsproblem”, Journal of the London Math. Soc. • ’38: PhD Princeton (viva on 21 June) : “Systems of Logic Based on Ordinals”, supervised by Alonzo Church. • Letter to Philipp Hall: “I hope Hitler will not have invaded England before I come back.” • ’39 Joins Bletchley Park: designs the “Bombe”. • ’40: First Bombes are fully operational • ’41: Breaks the German Naval Enigma. • ’42-44: Several contibutions to war effort on codebreaking; secure speech devices; computing. • ’45: Automatic Computing Engine (ACE) Computer. Slides by Luis C. -

Historical Perspective and Further Reading

Gresham's Law (“Bad Historical Perspective and Further money drives out Good”) for 3.10 computers would say, “The Reading 3.10 Fast drives out the Slow even if the Fast is wrong.” This section surveys the history of the floating point going back to von Neumann, including the surprisingly controversial IEEE standards effort, plus the rationale W. Kahan, 1992 for the 80-bit stack architecture for floating point in the IA-32. At first it may be hard to imagine a subject of less interest than the correctness of computer arithmetic or its accuracy, and harder still to understand why a sub- ject so old and mathematical should be so controversial. Computer arithmetic is as old as computing itself, and some of the subject’s earliest notions, like the eco- nomical reuse of registers during serial multiplication and division, still command respect today. Maurice Wilkes [1985] recalled a conversation about that notion during his visit to the United States in 1946, before the earliest stored-program computer had been built: . a project under von Neumann was to be set up at the Institute of Advanced Studies in Princeton. Goldstine explained to me the principal features of the design, including the device whereby the digits of the multiplier were put into the tail of the accumulator and shifted out as the least significant part of the product was shifted in. I expressed some admiration at the way registers and shifting circuits were arranged . and Goldstine remarked that things of that nature came very easily to von Neumann. There is no controversy here; it can hardly arise in the context of exact integer arithmetic so long as there is general agreement on what integer the correct result should be. -

Floating Point

Contents Articles Floating point 1 Positional notation 22 References Article Sources and Contributors 32 Image Sources, Licenses and Contributors 33 Article Licenses License 34 Floating point 1 Floating point In computing, floating point describes a method of representing an approximation of a real number in a way that can support a wide range of values. The numbers are, in general, represented approximately to a fixed number of significant digits (the significand) and scaled using an exponent. The base for the scaling is normally 2, 10 or 16. The typical number that can be represented exactly is of the form: Significant digits × baseexponent The idea of floating-point representation over intrinsically integer fixed-point numbers, which consist purely of significand, is that An early electromechanical programmable computer, expanding it with the exponent component achieves greater range. the Z3, included floating-point arithmetic (replica on display at Deutsches Museum in Munich). For instance, to represent large values, e.g. distances between galaxies, there is no need to keep all 39 decimal places down to femtometre-resolution (employed in particle physics). Assuming that the best resolution is in light years, only the 9 most significant decimal digits matter, whereas the remaining 30 digits carry pure noise, and thus can be safely dropped. This represents a savings of 100 bits of computer data storage. Instead of these 100 bits, much fewer are used to represent the scale (the exponent), e.g. 8 bits or 2 A diagram showing a representation of a decimal decimal digits. Given that one number can encode both astronomic floating-point number using a mantissa and an and subatomic distances with the same nine digits of accuracy, but exponent. -

Bibliography

Bibliography [1] E. Abu-Shama and M. Bayoumi. A new cell for low power adders. In Int. Midwest Symposium on Circuits and Systems, pages 1014–1017, 1995. [2] R. C. Agarwal, F. G. Gustavson, and M. S. Schmookler. Series approx- imation methods for divide and square root in the Power3 micropro- cessor. In Koren and Kornerup, editors, Proceedings of the 14th IEEE Symposium on Computer Arithmetic (Adelaide, Australia), pages 116–123. IEEE Computer Society Press, Los Alamitos, CA, April 1999. [3] T. Ahrendt. Fast high-precision computation of complex square roots. In Proceedings of ISSAC’96 (Zurich, Switzerland), 1996. [4] M. Ajtai. The shortest vector problem in L2 is NP-hard for random- ized reductions (extended abstract). In Proceedings of the annual ACM symposium on Theory of computing (STOC), pages 10–19, 1998. [5] M. Ajtai, R. Kumar, and D. Sivakumar. A sieve algorithm for the short- est lattice vector problem. In Proceedings of the annual ACM symposium on Theory of computing (STOC), pages 601–610, 2001. [6] L. Aksoy, E. Costa, P. Flores, and J. Monteiro. Optimization of area in digital FIR filters using gate-level metrics. In Design Automation Confer- ence, pages 420–423, 2007. [7] E. Allen, D. Chase, V. Luchangco, J.-W. Maessen, and G. L. Steele Jr. Object-oriented units of measurement. In OOPSLA ’04: Proceedings of the 19th Annual ACM SIGPLAN Conference on Object-Oriented Program- ming, Systems, Languages, and Applications, pages 384–403, New York, NY, 2004. ACM Press. [8] Altera Corporation. FFT/IFFT Block Floating Point Scaling, 2005. Appli- cation note 404-1.0. -

State of the Art and Future Directions of Computational Mathematics And

STANFORD 50: State of the Art & Future Directions of Computational Mathematics & Numerical Computing A conference celebrating the 50th anniversary of George Forsythe’s arrival at Stanford and Gene Golub’s 75th birthday Incorporating the Eighth Bay Area Scientific Computing Day (BASCD) Stanford University March 29–31, 2007 Contents Welcome from the Organizers! 3 Conference Schedule 4 Thursday, March 29, 2007 ...................................... 4 Friday, March 30, 2007 ........................................ 6 Saturday, March 31, 2007 ...................................... 8 Abstracts 9 Posters 20 Graduate Student Posters ...................................... 20 Junior Scientist Posters ....................................... 21 Judges ................................................. 21 Participants 22 FOR SYTHEtation 23 Some of George and Alexandra Forsythe’s Books ......................... 23 Some of Gene Golub’s Books .................................... 24 GENEalogy 25 George Forsythe’s PhD Students .................................. 25 Some of Gene Golub’s Postdocs ................................... 25 Gene’s PhD Students ......................................... 26 Fondly Remembered NA Graduates and Faculty 27 Acknowledgments 28 Sponsors ................................................ 28 Session Chairs ............................................ 29 Organizers ............................................... 29 Welcome from the Organizers! Stanford 50: State of the Art and Future Directions of Computational Mathematics and Numerical -

Acoustic Models for Speech Recognition Using Deep Neural

Acoustic Models for Speech Recognition Using Deep Neural Networks Based on Approximate Math by Leo Liu Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY June 2015 c Massachusetts Institute of Technology 2015. All rights reserved. Author.................................................................... Department of Electrical Engineering and Computer Science May 21, 2015 Certified by . James R. Glass Senior Research Scientist Thesis Supervisor Accepted by . Albert R. Meyer Chairman, Masters of Engineering Thesis Committee 2 Acoustic Models for Speech Recognition Using Deep Neural Networks Based on Approximate Math by Leo Liu Submitted to the Department of Electrical Engineering and Computer Science on May 21, 2015, in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science Abstract Deep Neural Networks (DNNs) are effective models for machine learning. Unfortunately, training a DNN is extremely time-consuming, even with the aid of a graphics processing unit (GPU). DNN training is especially slow for tasks with large datasets. Existing approaches for speeding up the process involve parallelizing the Stochastic Gradient Descent (SGD) algorithm used to train DNNs. Those approaches do not guarantee the same results as normal SGD since they introduce non-trivial changes into the algorithm. A new approach for faster training that avoids significant changes to SGD is to use low-precision hardware. The low-precision hardware is faster than a GPU, but it performs arithmetic with 1% error. In this arithmetic, 98 + 2 = 99:776 and 10 ∗ 10 = 100:863. -

Download and Use Untrusted Code Without Fear

2 KELEY COMPUTER SCIENC CONTENTS INTRODUCTION1 CITRIS AND2 MOTES 30 YEARS OF INNOVATION GENE MYERS4 Q&A 1973–20 0 3 6GRAPHICS INTELLIGENT SYSTEMS 1RESEARCH0 DEPARTMENT STATISTICS14 ROC-SOLID SYSTEMS16 USER INTERFACE DESIGN AND DEVELOPMENT20 INTERDISCIPLINARY THEOR22Y 30PROOF-CARRYING CODE 28 COMPLEXITY 30THEORY FACULTY32 THE COMPUTER SCIENCE DIVISION OF THE DEPARTMENT OF EECS AT UC BERKELEY WAS CREATED IN 1973. THIRTY YEARS OF INNOVATION IS A CELEBRATION OF THE ACHIEVEMENTS OF THE FACULTY, STAFF, STUDENTS AND ALUMNI DURING A PERIOD OF TRULY BREATHTAKING ADVANCES IN COMPUTER SCIENCE AND ENGINEERING. THE FIRST CHAIR OF COMPUTER research in theoretical computer science received a Turing Award in 1989 for this work. learning is bringing us ever closer to the dream SCIENCE AT BERKELEY was Richard Karp, at Berkeley. In the area of programming languages and of truly intelligent machines. who had just shown that the hardness of well- software engineering, Berkeley research has The impact of Berkeley research on the practi- Berkeley’s was the one of the first top comput- known algorithmic problems, such as finding been noted for its flair for combining theory cal end of computer science has been no less er science programs to invest seriously in com- the minimum cost tour for a travelling sales- and practice, as exemplified in these pages significant. The development of Reduced puter graphics, and our illustrious alumni in person, could be related to NP-completeness— by George Necula’s research on proof- Instruction Set computers by David Patterson that area have done us proud. We were not so a concept proposed earlier by former Berkeley carrying code. -

Co-Authorship Proximity of A. M. Turing Award and John Von Neumann Medal Winners to the Disciplinary Boundaries of Computer Science

Fields, p. 1 of 23 Co-authorship proximity of A. M. Turing Award and John von Neumann Medal winners to the disciplinary boundaries of computer science Chris Fields 528 Zinnia Court Sonoma, CA 95476 USA [email protected] Keywords: Biomedical sciences; Computer science; Cross-disciplinary brokers; Erdős numbers; Graph centrality; Interdisciplinarity Abstract It is shown that winners of the A. M. Turing Award or the John von Neumann Medal, both of which recognize achievement in computer science, are separated from some other A. M. Turing Award or John von Neumann Medal winner by at most 1.4 co-authorship steps on average, and from some cross- disciplinary broker, and hence from some discipline other than computer science, by at most 1.6 co- authorship steps on average. A. M. Turing Award and John von Neumann Medal recipients during this period are, therefore, on average closer in co-authorship terms to some other discipline that typical computer scientists are, on average, to each other. Introduction How are the most prominent and widely-recognized members of any scientific discipline distributed within the social network formed by that discipline? More specifically, how are the most prominent members of a discipline distributed within the co-authorship graph of that discipline? Studies of co- authorship paths traversing cross-disciplinary brokers (Fields, 2015) and of co-authorship connections of Nobel laureates in Physiology or Medicine (Fields, 2014; in press) suggest a surprising answer: prominent intellectual and, in many cases, political leaders of several disciplines appear to be located near the co-authorship boundaries of their disciplines, in close proximity to cross-disciplinary brokers. -

William Kahan Discusses the Whole of His Career to Date, with Particular Reference to His Involvement with Numerical Software and Hardware Design

An interview with WILLIAM M. KAHAN Conducted by Thomas Haigh On August 5-8, 2005 In Berkeley, CA Interview conducted by the Society for Industrial and Applied Mathematics, as part of grant # DE-FG02-01ER25547 awarded by the US Department of Energy. [Version 1.1, revised March 2016 with corrections from Prof. Kahan] Society for Industrial and Applied Mathematics 3600 University City Science Center Philadelphia, PA 19104-2688 Transcript donated to the Computer History Museum by the Society for Industrial and Applied Mathematics © Computer History Museum Mountain View, California ABSTRACT William Kahan discusses the whole of his career to date, with particular reference to his involvement with numerical software and hardware design. Kahan was born in Canada in 1933, growing up around Toronto. He developed an early interest in science and mathematics, tinkering with mechanical and electronic devices. Kahan earned a B.A. in mathematics from the University of Toronto in 1954. He discusses in detail his experiences with the FERUT computer from 1953 onward, including its operation and use and the roles of Kelly Gotlieb, Beatrice Worsley, Cecily Popplewell, Joe Kates, and others. During the summer of 1954 he worked with Kates to produce a prototype airline reservation system for Trans-Canada Airlines. Kahan then began work on a Ph.D. from Toronto, graduating in 1958 under the direction of Byron A. Griffith. He explains the state of its mathematics program and curriculum at this time, and outlines his own thesis work on successive overrelaxation methods and the beginning of his interest in backward error analysis. Kahan spent the summer of 1957 at the University of Illinois, where used the ILLIAC and met Dave Muller, Don Gillies and Gene Golub.