A Look at SW Performance Since 1940S

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Desktop Computer – Dell Optiplex

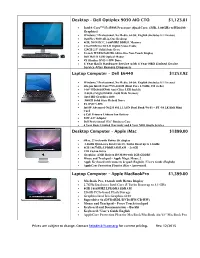

Desktop – Dell Optiplex 9030 AIO CTO $1,123.81 • Intel® Core™ i5-4590S Processor (Qual Core, 6MB, 3.00GHz w/HD4600 Graphics) • Windows 7 Professional, No Media, 64-bit, English (includes 8.1 License) • OptiPlex 9030 All-in-One Desktop • 8GB, NON-ECC, 1600MHZ DDR3L Memory • C2G HDMI to DVI-D Digital Video Cable • 128GB 2.5" Solid State Drive • 23-inch WLED Full-HD All-in-One Non-Touch Display • Dell MS111 USB Optical Mouse • 8X Slimline DVD+/-RW Drive • 4 Year Basic Hardware Service with 4 Year NBD Limited Onsite Service After Remote Diagnosis Laptop Computer – Dell E6440 $1253.92 • Windows 7 Professional, No Media, 64-bit, English (includes 8.1 License) • 4th gen Intel® Core™ i5-4300M (Dual Core 2.7GHz, 3M cache) • 14.0" HD(1660X900) Anti-Glare LED backlit • 8.0GB,(2x8gb) DDR3L-1600 MHz Memory • Intel HD Graphics 4600 • 500GB Solid State Hybrid Drive • 8X DVD+/-RW • Intel® Advanced-N6235 801.11 AGN Dual Bank Wi-Fi + BT 4.0 LE Half Mini Card • 6 Cell Primary Lithium Ion Battery • 90W A/C Adapter • Dell Professional 15.6” Business Case • 4 Year Basic Limited Warranty and 4 Year NBD Onsite Service Desktop Computer – Apple iMac $1899.00 • iMac, 27 inch with Retina 5K display • 3.2GHz Quad-core Intel Core i5, Turbo Boost up to 3.6GHz • 8GB 1867MHz LPDDR3 SDRAM - 2x4GB • 1TB Fusion Drive • Graphics: AMD Radeon R9 M390 with 2GB GDDR5 • Mouse and Trackpad – Apple Magic Mouse 2 • Apple Keyboard with numeric keypad (English) / User's Guide (English) • AppleCare Protection Plan for iMac - Auto-enroll Laptop Computer – Apple MacBookPro $1,399.00 • MacBook Pro, 13-inch with Retina Display • 2.7GHz Dual-core Intel Core i5 Turbo Boost up to 3.1 GHz • 8GB 1866MHZ LPDDR3 SDRAM • 256GB PCIe-based Flash Storage • Graphics Intel Iris Graphics 6100 • Superdrive 8x (DVD±RDL/DVD±RW/CD-RW) • Mouse and Trackpad – Force Touch trackpad • Keyboard and Documentation – Backlit • Keyboard / User’s Guide English • AppleCare Protection Plan for MacBook/MacBook Air/13" MacBook Pro Prices are subject to change. -

Computer Service Technician- CST Competency Requirements

Computer Service Technician- CST Competency Requirements This Competency listing serves to identify the major knowledge, skills, and training areas which the Computer Service Technician needs in order to perform the job of servicing the hardware and the systems software for personal computers (PCs). The present CST COMPETENCIES only address operating systems for Windows current version, plus three older. Included also are general common Linux and Apple competency information, as proprietary service contracts still keep most details specific to in-house service. The Competency is written so that it can be used as a course syllabus, or the study directed towards the education of individuals, who are expected to have basic computer hardware electronics knowledge and skills. Computer Service Technicians must be knowledgeable in the following technical areas: 1.0 SAFETY PROCEDURES / HANDLING / ENVIRONMENTAL AWARENESS 1.1 Explain the need for physical safety: 1.1.1 Lifting hardware 1.1.2 Electrical shock hazard 1.1.3 Fire hazard 1.1.4 Chemical hazard 1.2 Explain the purpose for Material Safety Data Sheets (MSDS) 1.3 Summarize work area safety and efficiency 1.4 Define first aid procedures 1.5 Describe potential hazards in both in-shop and in-home environments 1.6 Describe proper recycling and disposal procedures 2.0 COMPUTER ASSEMBLY AND DISASSEMBLY 2.1 List the tools required for removal and installation of all computer system components 2.2 Describe the proper removal and installation of a CPU 2.2.1 Describe proper use of Electrostatic Discharge -

Thinkcentre M700 Tower Platform Specifications Product Specifications Reference (PSREF)

ThinkCentre M700 Tower Platform Specifications Product Specifications Reference (PSREF) Processor Intel Celeron, Intel Pentium, or 6th Generation Intel Core™ i3 / i5 / i7 Processor Security features ● One lock to secure both cover and ● Power-on password Cores / Frequency Integrated entire system to fixed object: ● Administrator password Processor Cache Memory Types Threads Base/Max(GHz) Graphics -Padlock loop (in rear for opt padlock) ● Hard disk password -Security slot (in rear for optional Boot sequence control Celeron G3900 2 / 2 2.8 G 2 MB DDR4-2133 HD 510 ● Kensington MicroSaver cable) ● Boot without keyboard and mouse Pentium G4400 2 / 2 3.3G 3 MB DDR4-2133 HD 510 ● Optional cable lock to physically lock ● Individual USB port disablement Pentium G4500 2 / 2 3.5G 3 MB DDR4-2133 HD 530 both keyboard and mouse ● Optional chassis intrusion switch Core i3-6100 2 / 4 3.7 G 3 MB DDR4-2133 HD 530 Keyboard Some: PS/2 Keyboard (PS/2 connector), Lenovo logo Core i3-6300 2 / 4 3.8 G 4 MB DDR4-2133 HD 530 Some: Preferred Pro USB Keyboard (USB connector), Lenovo logo Some: Lenovo USB Fingerprint Keyboard (USB connector) Core i5-6400 4 / 4 2.7 G / 3.3 G 6 MB DDR4-2133 HD 530 Some: Ultraslim Plus Wireless Keyboard (2.4GHz via USB receiver), black Core i5-6500 4 / 4 3.2 G / 3.6 G 6 MB DDR4-2133 HD 530 Mouse Some: PS/2 Optical Wheel Mouse, black, Lenovo logo Core i5-6600 4 / 4 3.3 G / 3.9 G 6 MB DDR4-2133 HD 530 Some: Enhanced Optical USB Mouse, black, Lenovo logo Core i7-6700 4 / 8 3.4 G / 4.0 G 8 MB DDR4-2133 HD 530 Some: Ultraslim Plus Wireless -

Comptia A+ Exam Storage Notes

CompTIA A+ Exam Storage Notes Sky D. Semone September 2018 1 Questions All questions taken from 2016 reference guides and various helpful online sources. [2];[1] 1. Which of the following answers list(s) example(s) of storage media type(s) that can be read, but not written to? • CD-ROM • DVD-ROM 2. Which of the terms listed below refers to computer data storage systems, data storage devices, and data storage media that can be written to once, but read from multiple times? • WORM 3. Which of the following is an example of Write Once, Read Many (WORM) storage media type? • BD-R 4. What are the storage limitations of a standard CD-ROM media format? • Less than 800 MB of data storage capacity • Up to 80 minutes of uncompressed audio 5. Which of the following answers list(s) example(s) of storage media type(s) that can be erased and written to multiple times? • DVD-RW • BD-RE • CD-RW 6. Platters of a magnetic hard drive spin at a rate measured in: • Revolutions per minute 1 7. Which of the acronyms listed below refers to a dedicated storage appliance that can be added to a local network? • NAS 8. Which of the following answers list(s) example(s) of hot-swappable drives? • USB drive • FireWire drive • SATA drive • eSATA drive 9. A type of storage device with no moving parts that uses memory chips instead of magnetic platters is commonly referred to as a Solid-State Drive (SSD). • True 10. Flash memory card formats include: • xD-Picture Card • CompactFlash (CF) • Secure Digital (SD) 11. -

Fight, Less Energy, at Lower Cost!

CNO’s Naval-Industry R&D Partnership Conference 2003 Ronald Reagan Building, Washington, DC, 5 August 2003 More Fight, Less Energy, at Lower Cost! Amory B. Lovins Chief Executive Officer Chairman of the Board Rocky Mountain Institute Hypercar, Inc. www.rmi.org www.hypercar.com [email protected] Copyright © 2003 Rocky Mountain Institute. All rights reserved. Hypercar® is a registered trademark of Hypercar, Inc. .PDF-formatted posting and hard-copy reproduction are licensed to the U.S. Navy for noncommercial public use. Transformational objectives ◊ Radically reduce the energy consumption of land, sea, and air platforms ◊ Increase their combat effectiveness, agility, deployability, and sustainability ◊ Reduce their capital and operating costs ◊ No compromise, no tradeoff ―If we are to achieve results never before accom- plished, we must employ methods never before attempted.‖ — Sir Francis Bacon How can breakthrough design make big energy savings cost less than small or no savings? Let’s start with some building designs… Rocky Mountain Institute ◊ At 2200 m nr Aspen ◊ ―Winter and July,‖ frost any day, 39-d midwinter cloud ◊ Integrated design ◊ Superinsulated: k- 0.05 W/m2K roof, -0.14 walls, -0.47 to -0.7 [COG] glazings, air-to-air heat exchangers ◊ Thermally passive, 95% daylit ◊ Superefficient lts/eqt Savings (1983 tech.): ◊ 90% in home el. 2 (~120 Wav/372 m ) ◊ 99% in space & Grow bananas with water heating ◊ 10-month payback, no furnace at –44°C would be ≤0 now PG&E ACT2 House Davis, California ◊ Comfort without air conditioning at +45°C, even in 3-day heat storm ◊ Mature-market building cost $1,800 lower ◊ Present-valued mainten- ance cost $1,600 lower ◊ Original design’s energy use ~82% below California Title 24 standard (1992) ◊ Last 7 improvements jus- tified by savings of energy plus capital cost (last 1.5 T of a/c), not of energy alone ◊ Saved 3/4 of wall wood ◊ Later done at 46˚C too New design mentality: turn diminishing returns.. -

SSHD Goes the Distance

Marketing Bulletin SSHD goes the Distance Acquire Maximum Performance and Reliability with Seagate® Solid State Hybrid Drives With new technology breakthroughs seeming to emerge almost daily, it is easy to become a bit jaded. Claims of newer, faster, better are so commonplace that it is difficult for genuinely innovative products to capture the attention they deserve. A noteworthy exception is solid state drives (SSDs), which fire the imagination of business laptop users with their extraordinary speed and implicit (no moving parts) reliability. Could SSDs spell the end for hard disc drives (HDDs)? Well, not so fast. Cost is an immediate obstacle, as even consumer-grade SSDs cost an order of magnitude more than comparable-capacity HDDs; and high-performance, enterprise-class SSDs are much pricier. More worryingly, SSDs have issues with data integrity and long-term durability. Like a battery, SSDs gradually lose their ability to hold a charge (retain data) with frequent use (erasures/writes). Wear levelling delays this phenomenon but fragments data and slows performance... and defragging to restore speed adds to disc wear. The bottom line is that SSD speed comes at a price, in terms of both cost and diminished resilience. But what if SSDs could be paired with another technology, so that their respective strengths could complement each other, in effect making a whole greater than the sum of its parts? Melding SSD performance with HDD economy and capacity sounds ideal, but this hybrid approach only makes sense if the stumbling block of SSD’s long-term reliability issues can be resolved. Seagate has done precisely that, using sophisticated algorithms to monitor data usage dynamically, and intelligently determine what data should be copied to its hybrid drive’s solid state memory. -

Mushkin Enhanced MKNSSDBRKT2535 3.5-Inch to 2.5-Inch Drive Adapter Bracket Affordable Deal

Mushkin Enhanced MKNSSDBRKT2535 3.5-Inch to 2.5-Inch Drive Adapter Bracket Affordable Deal Budget friendly prices for Mushkin Enhanced MKNSSDBRKT2535 3.5-Inch to 2.5-Inch Drive Adapter Bracket for sale, a high quality Computer and Accessory inside the marketplace right now. See Product Image | Check Price Now | Customer Reviews Many customer comments recognize that the Mushkin Enhanced MKNSSDBRKT2535 3.5-Inch to 2.5-Inch Drive Adapter Bracket are really good Computer & Accessory and it's also affordable priced. It can be look for every testimony from users to make sure you find out more about any encounter. The consumer reviews will give you a good warning with the cost and reliability of these products. Total, It's the high quality product and we're extremely offer the product. If you searching for high quality Computer and Accessory. Only now we have the inexpensive available for Mushkin Enhanced MKNSSDBRKT2535 3.5-Inch to 2.5-Inch Drive Adapter Bracket with enjoyable offers plus fast shipping available to you. Where to Order Mushkin Enhanced MKNSSDBRKT2535 3.5-Inch to 2.5-Inch Drive Adapter Bracket Quickly? So now low priced Computer Accessory offered for sale, search for a item specs that suits your requirements and at a price you should be satisfied. Best buy Mushkin Enhanced MKNSSDBRKT2535 3.5-Inch to 2.5-Inch Drive Adapter Bracket one of really good item should do right now with low-cost, low cost shipping and 100% secure online payment system at Amazon.com the top webstore. Immediately after our check for cheap product, we have found inexpensive with low cost shipping and delivery. -

WD Blue™ PC SSHD

WD Blue™ PC SSHD The best of both worlds – HDD capacity meets SSD-like speed. WD Blue Solid State Hybrid Drives (SSHD) combine a generous amount of NAND flash SSD technology and massive HDD storage capacity into a single drive. WD engineers team up the best of SSD and HDD to produce a hybrid that can increase overall system performance – resulting in quicker system boots, faster application loads, and improved responsiveness when compared to traditional hard drives. FORM FACTOR MODEL NUMBERS CAPACITIES INTERFACE 2.5-inch WD10J31X 1 TB SATA 6 Gb/s 3.5-inch WD40E31X 4 TB SATA 6 Gb/s Product Features Inspiring performance Self-learning technology Simple installation with Gaming, owned and capacity Utilizing an advanced set of algorithms, no special software required A gaming rig equipped with WD WD Blue SSHD introduces high- WD Blue SSHDs track data usage, The WD Blue SSHD hybrid drive Blue SSHD can deliver faster game performance NAND flash SSD prioritizing frequently used data for is self-contained in a traditional loads, auto saves, and can reduce technology to the huge storage fast access in the solid state portion HDD form factor, and installs lag between levels, when compared capabilities of traditional HDD of the device, adapting, learning and as easily as any traditional hard to traditional hard drives. Ultra-fast storage - uniting both to enhance optimizing as new applications and drive without special drivers or drive response results in a smoother the computing experience. A single command requests change over time. downloads required. WD Blue gaming experience and the added WD Blue SSHD drive provides an These advanced algorithms reside in SSHDs are compatible with most capacity means gamers can store optimized, all-in-one solution which the SSHD firmware, enabling it to make typical computer configurations, more of today’s larger game files. -

Dell™ Latitude™ E6440 Technical Guidebook

Dell™ Latitude™ E6440 Technical Guidebook July 2013 Table of Contents Latitude E6440 Product Views and Detailed Engineering Specifications 17 – 44 3 - 9 Technical Specifications Primary storage 18-25 E6440 Weight, Dimensions, Top/Right 4 Optical drives 26-27 View Ports and connectors 28 E6440 Back/Left View 5 Webcam 29 E6440 Bottom View 6 Wireless LAN 30-33 Latitude E6440 Technical Specifications 7-9 Mobile Broadband 34 Wired communications 35 Marketing System Configurations 10 - 16 Integrated Graphics Controller 36 Operating Systems 11 Discrete Graphics Controller 37 Intel Architecture 12 Displays 38-39 Memory 13 Batteries 40 Primary Storage and Intel Rapid Start 14 Power Adapters 41 Technology Keyboards 42 Connectivity Options 15 Touchpad 43 Security and Keyboard specifications 16 Operating conditions and 44 MIL-STD-810G Testing 2 Latitude E6440 Product Views and Technical Specifications 3 Latitude E6440 Weight, Dimensions, Top/Right View 1. Microphone 15. ODD 1 2. Display release button 16. ODD tray release button 2 3 3. Camera 17. Wireless switch. 4 29 5 4. Camera status indicator 18. Express card reader. 6 7 5. Microphone 19. Fingerprint reader. 28 6. Display latch 20. SD card reader 7. Display 21. Contactless smart card reader 27 8. HDD activity indicator 22. Touchpad button. 9. Battery status indicator 23. Touchpad. 26 10. Wireless status indicator 24. Track stick buttons 25 11. Power button 25. Keyboard 24 8 12. USB 3.0 connector. 26. Track stick 9 13. Audio/microphone 27. Mute button. 10 combo connector 28. Volume down button. 14. E-module release button 29. Volume up button. 11 23 Starting weight: 12 4.68lbs / 2.12kg (with 6-cell battery and ODD) 22 13 21 14 20 15 16 Dimensions: 19 17 18 Width: 338.0 mm (13.31 inches) Depth: 232.6 mm (9.16 inches) Height; 30.8 mm (1.21 inches) 4 Latitude E6440 Back/Left View 1. -

Ideacentre Y700 Platform Specifications

Product Specifi cations Reference (PSREF) ideacentre Y700 Platform Specifi cations Processor 6th Generation Intel® Core™ i5 / i7 Processors Security features ● Security slot (in rear for Kensington® MicroSaver® cable) Cores / Frequency Integrated ● Power-on password Processor Cache Memory Types Threads (Base/Max) Graphics ● Administrator password Core i5-6400 4 / 4 2.7 GHz / 3.3 GHz 6 MB DDR4-2133 Keyboard Some: full-size, Gaming K600 USB keyboard , Fn keys, black Core i5-6500 4 / 4 3.2 GHz / 3.6 GHz 6 MB DDR4-2133 Intel HD Some: full-size USB keyboard, Fn keys, black silk Core i5-6600 4 / 4 3.3 GHz / 3.9 GHz 6 MB DDR4-2133 Graphics 530 Mouse Some: USB mouse Gaming M600, black Some: USB optical mouse, black silk Core i7-6700 4 / 8 3.4 GHz / 4.0 GHz 8 MB DDR4-2133 Mechanical ● Tower (34L), black color Memory 24GB max, PC4-17000 2133MHz DDR4, four 288-pin UDIMM sockets ● Dimensions (WxDxH): 8.12" x 19.82" x 18.85"; 206.4mm x 503.5mm x 478.9mm Disk Some: Solid State Hybrid Drive (SSHD) with 8GB MLC NAND fl ash memory, ● Weights (net weight): 33.1 lb (15 kg), vary by confi guration SATA 6.0Gb/s, 7200 rpm, 3.5" wide ● Top water cooling (under top) Some: SATA 6.0Gb/s, 3.5" wide, 7200 rpm Bay 1: 5.25", access, optical (optional) Some: SSD / 2.5" wide, SATA 6.0Gb/s Bay 2: 5.25", no access, disk Optical Some: DVD±RW SATA Bay 3: 3.5'', no access, disk (with 3.5'' to 2.5'' bracket) Some: Blu-ray burner DVD±RW SATA Bay 4: 3.5'', no access, disk (with 3.5'' to 2.5'' bracket) Onboard SATA SATA 6.0Gb/s controller (integrated in chipset), six SATA 6.0Gb/s -

INTERNAL SOLID STATE HYBRID DRIVE KIT Data Sheet SSD Speed. HDD Capacity. Affordable Price

INTERNAL SOLID STATE HYBRID DRIVE KIT Data Sheet SSD Speed. HDD capacity. Affordable Price. The Seagate® Laptop SSHD combines a 1TB hard drive and 8GB of solid state MLC flash to add SSD-like performance to any laptop. The Laptop SSHD boots and launches applications within seconds like a solid state drive, but is more affordable because the combined technology leverages the cost efficiency of a hard disk drive. Adaptive Memory™ technology intelligently monitors the frequently used files and stores them in the solid state memory for blazing fast recall. The SATA 6Gb/s interface enables the use of the industry’s latest and fastest hard drive controllers while providing backward compatibility to SATA 3Gb/s. The Laptop SSHD is designed to work in most laptops and is optimised for mobile computing and small form factor PCs to simultaneously run multiple applications like video and photography editing, video playback and computer games. SOLID STATE HYBRID DRIVE KIT Specifications Retail Packaging Product Dimensions Box Dimensions Master Carton Dimensions Pallet Dimensions Length (in/mm) 3.92/99.57 4.67/119.0 6.5/165 39.88/1,012 Width (in/mm) 2.75/69.72 6.25/158.7 5.5/139.7 43.06/1,093 Depth (in/mm) 0.37/9.4 1.75/44.45 4.81/122.2 43.69/1,109 Weight (lb/kg) 0.244/0.111 0.43/0.194 1.516/0.69 694.523/315.692 Quantities Boxes per Master Carton 3 Master Cartons per Pallet 392 Pallet Layers 8 System Requirements1 6Gb/s SATA (backward compatible to SATA 3Gb/s) Windows® 10, Windows 8 or Windows 7 MacBook®, MacBook Pro or Mac Mini computer with Intel® processor running Mac® OS X operating system Linux Inside the Box Seagate® Laptop SSHD (2.5-inch solid state hybrid drive) 5-year limited warranty Region Product Capacity2 Model Number UPC Code EAN Code Multi-Pack UPC WW Seagate Laptop SSHD 1TB STBD1000400 763649046852 7636490045400 10763649046859 1 Consult your authorised service centre or notebook manufacturer for information about compatibility with this hard drive. -

Comparative Analysis Study on SSD, HDD, and SSHD

Turkish Journal of Computer and Mathematics Education Vol.12 No.3(2021), 3635-3641 Research Article Comparative Analysis Study on SSD, HDD, and SSHD Ms.Hepisuthara, Dr. Priyankasharmab aDepartment Of Research and Publication divisionRashtriyaraksha university Gandhinagar bDepartment of Research and Publication Division, RashtriyaRaksha University Gandhinagar Article History: Received: 10 November 2020; Revised 12 January 2021 Accepted: 27 January 2021; Published online: 5 April 2021 _____________________________________________________________________________________________________ Abstract: In the Current Century, permeant storage devices and methods of storing data changed from traditional HDD to SDD. In this document, we discuss the merge of HDD and SSD. The Abbreviation of SSHD is called the solid-state hybrid disk. A mixture of both secondary devices to enhance the performance of the system. Inside the SSD, data movement events occur without any user input. Recent research has suggested that SSD has only the Replacement of secondary storage. HDD is also good in life span with longer life. It‟s more reliable for long time data contained in this. HDD storage has typical magnetic fields for store data. SSD contains NAND flash memory to write the data in the drive. Based on the method and material of storing different. HDD and SSD feature well to upgrade with technology in Computer filed. For enhancing computing speed and excellent processing SSHD good to use in computer.Ratio increase of SSHD usage in current laptop and in computer system. Keywords: SSD, Secondary Storage Device, NAND Flash Memory, HDD, SSHD, Hybrid Drive ___________________________________________________________________________ 1. Introduction As the design of computers has improved with time, many manufacturers have moved from traditional HDDs to SSDs.