Bicmos Cold Cathode Fluorescent Lamp Driver Controller Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Replacement Lamp Guide

VALLEYMED Replacement Lamp Guide • MINATURE • SCIENTIFIC • X-RAY • OPERATING ROOM • SURGICAL • ENDOSCOPY • PHOTO-THERAPY • MICROSCOPE • ILLUMINATOR • ANALYZER • DIAGNOSTIC • INFRA-RED • OPTHALMIC • GERMICIDAL • DENTAL • ULTRAVIOLET Valley is Out to Change the Way You Buy Specialty Replacement Lamps! e’re committed to providing our Wcustomers with the highest quality FREE DELIVERY ON ORDERS OVER $200 of service and product knowledge. We understand your business; the daily pressures; the equipment and we want to make your job We pay the shipping* on lamp orders of over $200. net value. easier. *Covers standard ground delivery from our central Burlington, So when you need a replacement lamp why Ontario warehouse to any location in Canada. Need it faster? not take advantage of all the benefits that Valley has to offer – like lamp identification, We’ll ship your order via the courier of your choice and bill you same-day shipping, product support, fully the cost, or charge it to your own carrier account. tested and validated products? There’s only one number you need to know for specialty lamps: 1-800-862-7616 WARRANTY This catalogue identifies only part of our full We want our customers to be satisfied. range of high quality lamps, such as those used in the medical, scientific, ophthalmic, ValleyMed Inc. carefully researches all products offered to ensure that they surgical, dental, germicidal, non-destructive meet our high standards of quality. If for any reason your purchase does not meet your standards, we want to know about it -- and we will make it right testing and diagnostic fields, as well as lamps for you. -

CATHODE LIGHT STRIP Single-Lamp Modular Cold Cathode Fluorescent Fixture • Model CLS

CATHODE LIGHT STRIP Single-Lamp Modular Cold Cathode Fluorescent Fixture • Model CLS U.S. and international patents pending. Conference Room, Anadarko Petroleum Photo: Eric Long Washington, DC Architect: Davis Carter Scott © 2002 Cathode Lighting Systems Inc. 8020 Queenair Drive, Gaithersburg, MD 20879 • ph: 301 921 4120 • fax: 301 963 3050 e-mail: [email protected] • website: www.CathodeLightingSystems.com INALLY, THE LOOK OF A CUSTOM COLD CATHODE INSTALLATION IN AN OFF- FTHE-SHELF MODULAR SYSTEM. OUR ARCHITECTURAL-GRADE COLD CATHODE FIXTURE MAKES DESIGNING SEAMLESS SPECIAL EFFECTS LIGHTING EASIER THAN EVER. LAMPS ARE ILLUMINATED FROM END TO END, CREATING TRUE SHADOWLESS LINEAR FLUORESCENT LIGHT. STANDARD INTEGRAL DIMMING BALLASTS, SIMPLE INSTALLATION, AND A LAMP LIFE OF 50,000 HOURS MAKE CATHODE LIGHT STRIP THE CLEAR CHOICE WHEN THE HIGHEST-QUALITY LONG-LIFE LIGHTING EFFECTS ARE REQUIRED. CATHODE LIGHT STRIP, PERFECT ELEGANCE WAS NEVER SO EASY. Model CLS-4 shown equipped with a warm white (30TC) lamp. FEATURES: • SEAMLESS ILLUMINATION: Lamp illumination is • DIMMABLE: Fixtures are supplied standard with integral complete, from end to end, with no dark spots or socket dimmable ballasts. shadow. • ALL FIXTURES DIM AT THE SAME RATE: Cathode Light • ULTRA-LONG LAMP LIFE: The cold cathode lamp has Strip has been engineered to dim evenly from fixture to a life of 50,000 hours +. fixture, regardless of length or combinations of differing • LOW PROFILE: Just 2 5/8" wide and 3 1/2" tall, much lengths. smaller than traditional custom cold cathode. • STREAMLINED AND LIGHTWEIGHT: Fixtures are • AVAILABLE IN A VARIETY OF LENGTHS: With eight made from satin anodized architectural-grade, snap-fit standard sizes available, fixtures can be combined or aluminum extrusion. -

Leveraging Open Source Software

1 Leveraging Open Source Software (Text of talk delivered by Justice Yatindra Singh Judge Allahabad High Court at the 9th e- Governance conference on 3rd February 2006 at Kochi, Kerala) FUD is an abbreviation of fear, uncertainty and doubt; it is often a salesman's strategy: spreading false rumours regarding others' products. Open source software (OSS) is its victim. In our country FUD for OSS arises out of ignorance. I am glad that, we are discussing OSS as it has crucial role to play in the IT world. WHAT IS OSS? A computer programme consists of two parts: Source Code and Object Code. Nowadays, computer programmes are written in high level computer languages using compact English words. This part is known as source code. These languages also have a programme called compiler and with their help, source code is compiled into machine language so that computers may understand it. When it is so done, it is called object code or machine code. Description―if it complies with certain conditions―is protected as a Copyright. Source code is a kind of description and can be protected as copyright provided it is published or disclosed. In the proprietery software, source code is generally not disclosed and in such a situation it is protected as a trade secret or undisclosed information. There was a debate whether object code is protected as a copyright or not but after TRIPS, it has to be protected as a copyright and now object code is so protected. Everyone is not using copyrights to have rights in computer programme. -

Paper / Subject Code: 82103 / Free & Open Source Software. (2 1/2

Paper / Subject Code: 82103 / Free & Open Source Software. (2 1/2 Hours) [Total Marks: 75] N.B. 1) All questions are compulsory. 2) Figures to the right indicate marks. 3) Illustrations, in-depth answers and diagrams will be appreciated. 4) Mixing of sub-questions is not allowed. 5) Assume suitable data wherever required. Q1 Attempt All(Each of 5 marks) (15) a) Multiple Choice Questions 1) GPL stands for i) General Public License ii) General Public License ii) Generic Public License iv) General Private License 2) Which of the following is not a phase of Life Cycle Paradigm / waterfall model? i) Analysis ii) Manufacturing iii) Design iv) Coding 3) is the founder of FSF i) Richard Stallman ii) Denis Ritchie iii) Ken Thomson iv) All of these 4) is a form of licensing 1n which an author surrenders some but not all rights under copyright law i) Copydown ii) License ii) Copyleft iv) Patent 5) The term BSD stands for 1) Binary software distribution ii) Berkley software distribution iii) Binary software development iv) Berkley software development b) Fill in the blanks (Waterfall model, full, internationalization, Prototyping model, Firefox, localization, chrome, free hardware design, partial, open source software) 1) __________is a Static, sequential and procedural approach in software engineering methodology. 2) _______copyleft is when all parts of work can be modified by consecutive authors. 3) ____________is the process of adapting software for a specific region or language by adding locale-specific components and translating text. 4) _____________is a web browser project descended from Mozilla application suite. 5) ___________refers to design which can be freely copied, distributed, modified and manufactured. -

Project Proposal a Comparative Analysis of the LAMP (Linux, Apache, Mysql and PHP) and Microsoft .NET (Windows XP, IIS, Microsof

Project Proposal A comparative analysis of the LAMP (Linux, Apache, MySQL and PHP) and Microsoft .NET (Windows XP, IIS, Microsoft SQL Server and ASP.NET) frameworks within the challenging domain of limited connectivity and internet speeds as presented by African countries. By: Christo Crampton Supervisor: Madeleine Wright 1.) Overview of the research With the recent releases of ASP.NET and PHP 5, there has been much debate over which technology is better. I propose to develop and implement an industry strength online journal management system (AJOL – African Journals OnLine) using both frameworks, and use this as the basis for comparative analysis of the two frameworks against eachother. 2.) Product Specification AJOL is an existing website ( www.ajol.org ) which acts as an aggregation agent for a number of publishers of African journals who wish to publish their journals online and of course for researchers looking for information. The existing system is based on the OJS (Open Journal System) developed by Berkeley University. The system consists of a user frontend – where users can browse and search the contents of the database online – and an administration frontend – where publishers can log in and manage their journals on the database by performing tasks such as adding new abstracts or editing existing abstracts. It is currently developed in PHP with a MySQL backend. The proposed system will consist of an online user interface, and online administration interface for publishers, as well as an offline administration interface for publishers. The online and offline administration interfaces are complementary and publishers can use either or both according to their preference. -

Operation Manual

DIGITAL MOTION PICTURE CAMERA F65 OPERATION MANUAL [English] 1st Edition Before operating the unit, please read this manual thoroughly Egenskaper för intern lasermodul and retain it for future reference. Våglängd : 850 nm Strålningens varaktighet : Pulsmodulation Lasereffekt : 4 mW/kanal (max) WARNING Standard : IEC60825-1 (2007) To reduce the risk of fire or electric shock, Egenskaper for innvendig lasermodul do not expose this apparatus to rain or Bølgelengde : 850 nm Strålingsvarighet : Pulsmodulasjon moisture. Utgangseffekt for laser : 4 mW / kanal (maks.) Standard : IEC60825-1 (2007) To avoid electrical shock, do not open the Caution cabinet. Refer servicing to qualified The use of optical instruments with this product will increase personnel only. eye hazard. For the customers in the U.S.A. Caution This equipment has been tested and found to comply with the Use of controls or adjustments or performance of procedures limits for a Class A digital device, pursuant to Part 15 of the other than those specified herein may result in hazardous FCC Rules. These limits are designed to provide reasonable radiation exposure. Do not open the outer case and protection against harmful interference when the equipment is disassemble or otherwise modify. operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense. This Digital Motion Picture Camera is classified as a CLASS 1 LASER PRODUCT. -

G-Tran Series Sensor Unit Model Sc1 Cold-Cathode Ion

No. SK00-8431-EI-023-03 G-TRAN SERIES SENSOR UNIT MODEL SC1 COLD-CATHODE ION GAUGE INSTRUCTION MANUAL This manual is for the SC1 cold-cathode ion gauges of the following serial numbers. Serial No. 02300G and higher Read this manual before operation and keep it at hand for immediate reference. Components Division, ULVAC , Inc. 2500 Hagizono, Chigasaki City, Kanagawa-ken, Japan http://www.ulvac.co.jp/ Prior to Operation Upon receipt of this gauge, make sure that it is the correct model you ordered and that it is not damaged in transit. Read this instruction manual before installing, operating, inspecting, or maintaining the product and fully understand the safety precautions, specifications and operating procedures regarding the product. The copyright of this instruction manual is held by ULVAC, Inc. You are prohibited from copying any portion of this instruction manual without the consent of ULVAC Inc. You are also prohibited from disclosing or transferring this instruction manual to third parties without the express written consent of ULVAC Inc. The contents described in this instruction manual are subject to change without prior notice because of changes in specifications or because of product improvements. Safety Denotations Safety symbols are used throughout this instruction manual to call the operator's attention to safety. The terminology used in safety symbols is classified below. Indicate status of urgency of danger when failure to comply with DANGER results in serious personal injury or death The work ignoring this warning will lead to serious damage to human life or factory facility (including this equipment) at a high probability. -

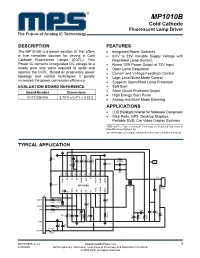

MP1010B Cold Cathode Fluorescent Lamp Driver the Future of Analog IC Technology

MP1010B Cold Cathode Fluorescent Lamp Driver The Future of Analog IC Technology DESCRIPTION FEATURES The MP1010B is a power solution IC that offers • Integrated Power Switches a true complete solution for driving a Cold • 6.0V to 23V Variable Supply Voltage with Cathode Fluorescent Lamps (CCFL). This Regulated Lamp Current. Power IC converts unregulated DC voltage to a • Rated 12W Power Output at 12V Input nearly pure sine wave required to ignite and • Open Lamp Regulation operate the CCFL. Based on proprietary power • Current and Voltage Feedback Control topology and control techniques it greatly • Logic Level Burst Mode Control increases the power conversion efficiency. • Supports Open/Short Lamp Protection EVALUATION BOARD REFERENCE • Soft-Start Board Number Dimensions • Short Circuit Protected Output • High Energy Start Pulse EV1010B-00A 3.75”X x 0.4”Y x 0.25”Z • Analog and Burst Mode Dimming APPLICATIONS • LCD Backlight Inverter for Notebook Computers • Web Pads, GPS, Desktop Displays, Portable DVD, Car Video Display Systems “MPS” and “The Future of Analog IC Technology” are Registered Trademarks of Monolithic Power Systems, Inc. The MP1010B is covered by US Patents 6,633,138, 6,316,881, 6,114,814. TYPICAL APPLICATION Rs Cft2 Rdamp Cft1 Cref N1 CbaR Ccomp CbtR Rft Cp N/A 20 19 18 17 16 15 14 13 12 11 HV IN FT FB OL 2 REF BSTR OUTR PGND AGND COMP Rbosc 1 MP1010B T1 CN1 BR IL BOS T/B EN DR IN OUTL PGND BSTL 1 2 3 4 5 6 7 8 9 J1 10 ABRT 5 Rabr Cabr CbtL DBRT 4 Cdrv Rbdr EN 3 Cisb Ren1 N/A Cs1 Cs2 Rlfb Resd Cen Cdbr Rbleed Ren2 CbaL Cbosc Risb Csfb Rsfb GND 2 Cba2 F1 / 1A Cba1 VBATT 1 FUSE MP1010B Rev. -

Building a Secure Wordpress Server (Lamp) with Centos 7

Essential Linux Skills with CentOS 7 BUILDING A SECURE WORDPRESS SERVER (LAMP) WITH CENTOS 7 Ray Heffer @rayheffer VERSION 1.1 - SEPTEMBER 2017 Building A Secure Wordpress Server (LAMP) With CentOS 7 © 2017 Ray Heffer. All rights reserved. No part of this eBook shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, or otherwise, without written permission from the author. No patent liability is assumed on the use of the information contained herein. Every precaution has been taken in the preparation of this eBook, the author assumes no responsibility for errors or omissions. This product is protected by U.S. and international copyright and intellectual property laws. All other marks and names mentioned herein may be trademarks of their respective companies. Original content by the author (Ray Heffer) first published as a blog series on https://www.rayheffer.com Due to the dynamic nature of the internet, any website links or references contained herein may have changed since the publication and may no longer be valid. The views expressed in this eBook are solely those of the author and do not necessarily reflect the views of any technology vendors, or third parties, and herby disclaims any responsibility. Essential Linux Skills with CentOS 7 | Page 2 © 2017 Ray Heffer | https://rayheffer.com @rayheffer Building A Secure Wordpress Server (LAMP) With CentOS 7 Table of Contents Introduction 5 Assumptions ............................................................................................................................................................. -

Letter Circular 817: Fluorescent Lamps

. RPT : RMC U. S. DEPARTMENT OF COMMERCE Letter IV- 3 NATIONAL BUREAU OF STANDARDS Circular WASHINGTON 25 LC-817 ‘February 4, 1946 ^^(Sup^geding FLUORESCENT LAMPS Contents^" - O* _ , Page I. Introduction . ........ jg*,. ..... 1 II. Work of the National Bureau- of, Standards on Fluorescent Lamps ...... .X ........ 4 III. Description of the . Lamp\ . ^ 4 IV. General Information .... ...... 3 V. Does the Fluorescent Lamp Have Any Deleterious Effect on Vision or the Eye? 4 VI. Bibliography .......... 6 I . Introduction The development of fluorescent lamps and their possibilities for general and decorative lighting purposes have brought many requests for information to the Bureau. This letter circular has been prepared to answer such inquiries. It contains information which has been accumulated in answering these letters, but is not an exhaustive treatise on the subject. II Work of the National Bureau of Standards on Fluorescent Lamps. , The development of fluorescent lamps by their manufacturers is progressing so rapidly that, although the Bureau has studied the radiation from these lamps, as discussed in Section V, it has as yet made no extensive tests to compare the efficiencies or costs of operation of fluorescent and incandescent lamps. Such information is given by the manufacturers and is referred to below. A letter circular on Fluorescence and Phosphorescence, LC-550, was issued by the Bureau under date of April 1, 1939; it is available, without cost, upon written request. Ill Description of Lamps The most commonly used type of fluorescent lamp is made in the form of a tubular bulb with a filament- type electrode sealed in each end. -

Open Source and Third Party Documentation

Open Source and Third Party Documentation Verint.com Twitter.com/verint Facebook.com/verint Blog.verint.com Content Introduction.....................2 Licenses..........................3 Page 1 Open Source Attribution Certain components of this Software or software contained in this Product (collectively, "Software") may be covered by so-called "free or open source" software licenses ("Open Source Components"), which includes any software licenses approved as open source licenses by the Open Source Initiative or any similar licenses, including without limitation any license that, as a condition of distribution of the Open Source Components licensed, requires that the distributor make the Open Source Components available in source code format. A license in each Open Source Component is provided to you in accordance with the specific license terms specified in their respective license terms. EXCEPT WITH REGARD TO ANY WARRANTIES OR OTHER RIGHTS AND OBLIGATIONS EXPRESSLY PROVIDED DIRECTLY TO YOU FROM VERINT, ALL OPEN SOURCE COMPONENTS ARE PROVIDED "AS IS" AND ANY EXPRESSED OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. Any third party technology that may be appropriate or necessary for use with the Verint Product is licensed to you only for use with the Verint Product under the terms of the third party license agreement specified in the Documentation, the Software or as provided online at http://verint.com/thirdpartylicense. You may not take any action that would separate the third party technology from the Verint Product. Unless otherwise permitted under the terms of the third party license agreement, you agree to only use the third party technology in conjunction with the Verint Product. -

INFORMATION CIRCULAR Original: ENGLISH (Unofficial Electronic Edition) ______

INF INFCIRC/254/Rev.3/Part 2*/ 24 February 1998 International Atomic Energy Agency GENERAL Distr. INFORMATION CIRCULAR Original: ENGLISH (Unofficial electronic edition) ___________________________________________________________________________ COMMUNICATION RECEIVED FROM CERTAIN MEMBER STATES REGARDING GUIDELINES FOR THE EXPORT OF NUCLEAR MATERIAL, EQUIPMENT AND TECHNOLOGY Nuclear-related Dual-use Transfers 1. The Director General has received notes verbales dated 30 September 1997 from the Resident Representatives to the Agency of Argentina, Australia, Austria, Belgium, Bulgaria, Canada, the Czech Republic, Denmark, France, Germany, Greece, Hungary, Ireland, Italy, Japan, Republic of Korea, New Zealand, Norway, Poland, Portugal, Romania, the Russian Federation, the Slovak Republic, South Africa, Spain, Sweden, Switzerland, Ukraine, the United Kingdom of Great Britain and Northern Ireland, and the United States of America relating to the export of nuclear material, equipment and technology. 2. The purpose of the notes verbales is to provide further information about the Guidelines for Transfers of Nuclear-related Dual-use Equipment, Material and related Technology in accordance with which the relevant Governments act. 3. In the light of the wish expressed at the end of each note verbale, the text of the notes verbales is attached. The attachment to these notes verbales is also reproduced in full. _____________________ */ INFCIRC/254/Rev.3/Part 1 contains Guidelines for Nuclear Transfers ANNEX NOTE VERBALE The Permanent Mission of [Member State] presents its compliments to the Director General of the International Atomic Energy Agency and has the honour to refer to its [relevant previous communication(s)] concerning the decision of the Government of [Member State] to act in accordance with the Guidelines for Transfers of Nuclear-Related Dual-Use Equipment, Material and Related Technology currently published as document INFCIRC/254/Rev.2/Part 2/MOD.