CBTL06122 High-Performance Displayport/Pcie Gen2 Hex Display Multiplexer Rev

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

TUSB1046-DCI USB Type-C™ Displayport™ ALT Mode 10 Gbps Linear Redriver Crosspoint Switch 1 Features 2 Applications

Product Order Technical Tools & Support & Folder Now Documents Software Community TUSB1046-DCI SLLSEW2D –AUGUST 2016–REVISED APRIL 2019 TUSB1046-DCI USB Type-C™ DisplayPort™ ALT Mode 10 Gbps Linear Redriver Crosspoint Switch 1 Features 2 Applications 1• USB Type-C crosspoint switch supporting • Tablets – USB 3.1 SSP + 2 DisplayPort lanes • Notebooks – 4 DisplayPort lanes • Desktops • USB 3.1 Gen 1/Gen 2 up to 10 Gbps • Docking stations • DisplayPort 1.4 up to 8.1 Gbps (HBR3) • VESA® DisplayPort Alt mode DFP redriving 3 Description crosspoint switch supporting C, D, E and F The TUSB1046-DCI is a VESA USB Type-C™ Alt configurations Mode redriving switch supporting USB 3.1 data rates up to 10 Gbps and DisplayPort 1.4 up to 8.1 Gbps for • Ultra-low-power architecture downstream facing port (Host). The device is used for • Linear redriver with up to 14 dB equalization configurations C, D, E, and F from the VESA • Transparent to DisplayPort link training DisplayPort Alt Mode on USB Type-C Standard Version 1.1. This protocol-agnostic linear redriver is • Automatic LFPS de-emphasis control to meet also capable of supporting other USB Type-C Alt USB 3.1 certification requirements Mode interfaces. • Configuration through GPIO or I2C The TUSB1046-DCI provides several levels of • Hot-plug capable receive linear equalization to compensate for cable • Industrial temperature range: -40ºC to 85ºC and board trace loss due to inter-symbol interference (TUSB1046I-DCI) (ISI). The device operates on a single 3.3 V supply • Commercial temperature range: 0ºC to 70ºC and comes in a commercial temperature range and industrial temperature range. -

USB-C to Displayport Adapter with Alternate Mode

USB-C to Displayport Adapter with Alternate Highlights Mode - DP 1.2, 4K60 ● Supports USB DisplayPort Alternate Mode for transmitting MODEL NUMBER: U444-06N-DP-AM audio/video ● Delivers UHD picture quality at resolutions up to 4096 x 2160 (4K) @ 60 Hz ● Compact and easy to carry in a pocket, purse or laptop bag ● Reversible USB-C plug connects in either direction ● Plug-and-play operation with no software or drivers required System Requirements ● Source device with USB-C or Connects your existing 4K DisplayPort TV, monitor or projector to the USB-C or Thunderbolt 3 port on Thunderbolt 3 port that supports your tablet, laptop, notebook, MacBook, Chromebook, smartphone or PC. USB DisplayPort Alternate Mode Description The U444-06N-DP-AM USB 3.1 Gen 1 USB-C to DisplayPort 4K Adapter (M/F) helps you transmit digital ● Display device with DisplayPort audio and 4K video from your tablet, laptop, Chromebook, MacBook, smartphone or PC to a DisplayPort- enabled television, monitor or projector. It’s an ideal tool for giving video presentations in conference input rooms and classrooms, editing multiple documents on a larger screen, or streaming video for digital signage in crystal-clear 4K. Package Includes With a source device that also supports USB DisplayPort Alternate Mode, you can extend video from your primary display to another, duplicate the same video on both displays, or change the second display to ● U444-06N-DP-AM USB 3.1 Gen your primary. 1 USB-C to DisplayPort 4K The plug-and-play U444-06N-DP-AM requires no software, drivers or external power. -

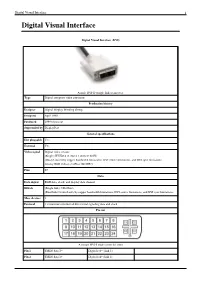

Digital Visual Interface (DVI)

Digital Visual Interface 1 Digital Visual Interface Digital Visual Interface (DVI) A male DVI-D (single link) connector. Type Digital computer video connector Production history Designer Digital Display Working Group Designed April 1999 Produced 1999 to present Superseded by DisplayPort General specifications Hot pluggable Yes External Yes Video signal Digital video stream: (Single) WUXGA (1,920 × 1,200) @ 60 Hz (Dual) Limited by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Analog RGB video (−3 dB at 400 MHz) Pins 29 Data Data signal RGB data, clock, and display data channel Bitrate (Single link) 3.96 Gbit/s (Dual link) Limited only by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Max. devices 1 Protocol 3 × transition minimized differential signaling data and clock Pin out A female DVI-I socket from the front Pin 1 TMDS data 2− Digital red− (link 1) Pin 2 TMDS data 2+ Digital red+ (link 1) Digital Visual Interface 2 Pin 3 TMDS data 2/4 shield Pin 4 TMDS data 4− Digital green− (link 2) Pin 5 TMDS data 4+ Digital green+ (link 2) Pin 6 DDC clock Pin 7 DDC data Pin 8 Analog vertical sync Pin 9 TMDS data 1− Digital green− (link 1) Pin 10 TMDS data 1+ Digital green+ (link 1) Pin 11 TMDS data 1/3 shield Pin 12 TMDS data 3- Digital blue− (link 2) Pin 13 TMDS data 3+ Digital blue+ (link 2) Pin 14 +5 V Power for monitor when in standby Pin 15 Ground Return for pin 14 and analog sync Pin 16 Hot plug detect Pin 17 TMDS data 0− Digital blue− (link 1) and digital sync Pin 18 TMDS data 0+ Digital blue+ (link 1) and digital sync Pin 19 TMDS data 0/5 shield Pin 20 TMDS data 5− Digital red− (link 2) Pin 21 TMDS data 5+ Digital red+ (link 2) Pin 22 TMDS clock shield Pin 23 TMDS clock+ Digital clock+ (links 1 and 2) Pin 24 TMDS clock− Digital clock− (links 1 and 2) C1 Analog red C2 Analog green C3 Analog blue C4 Analog horizontal sync C5 Analog ground Return for R, G, and B signals Digital Visual Interface (DVI) is a video display interface developed by the Digital Display Working Group (DDWG). -

Multiport M.2 NGFF PS/2 HDMI Firewire Network SATA IDE Mini

Connection-Know-How www.delock.com RF Memory SATA Displayport Graphics / Video radio frequency technology Cards SATA SATA male female Dualport HDMI + Displayport Cinch Video Cinch Video Cfast female female male female N plug F plug eSATA SATA male female S-Video female Compact Flash female Sub-D Displayport Displayport male female eSATAp eSATAp TNC Coaxial NEW male female Scart male plug plug Serial Serial mini mini 9 pin 9 pin Displayport Displayport Contact Golden Strip male female male female eSATApd male SD SD 4.0 DMS male DMS female female female RP-TNC RP-TNC UHS-I-Card UHS-II-Card plug jack Slim SATA 13 pin male Null Modem 8 pin male HDMI VGA Micro SATA 16 pin VGA Parallel 25 pin male female M.2 NGFF male male HDMI A HDMI A FME FME male female plug jack M.2 NGFF Key B+M Micro SATA 16 pin female Parallel 25 pin female VHDCI-68 male HDMI HDMI mini-C mini-C M.2 NGFF Key B male female SATA 22 pin male BNC BNC Sub-D 15 pin Gameport VHDCI-68 female plug jack male M.2 NGFF Key M SATA 22 pin female HDMI HDMI micro-D micro-D male female Sub-D 15 pin Gameport SMA SMA female LFH 60 male plug jack mini PCIe SAS male Multiport Sub-D 37 pin male PS/2 miniPCIe female mSATA female RP-SMA RP-SMA NEU plug jack BNC Stecker miniPCIe male mSATA male Sub-D 37 pin female Multiport female BNC Buchse PS/2 female SMB SMB plug jack Audio USB Mobile DVI FireWire MCX MCX plug jack Audio Stereo iPhone 30 pin female DVI-D Dual Link 24+1 USB 2.0 A USB 2.0 A FireWire A FireWire A female male male female 6 pin 6 pin male female UHF UHF Stereo 3 pin Stereo 3 pin -

GUD3C05 Datasheet

GUD3C05 USB-C Docking Station with Power Delivery 3.0 Instantly dock up to 10 devices Charge laptop & devices with up to100W pass-through1&2 Fast Role Swap provides safe operation for connected devices during power changes Versatile video options: HDMI (4K), Mini DisplayPort (4K) or VGA (1080p) Dual video outputs available via HDMI & Mini DisplayPort for up to 1080p @60Hz3 Laptop Expandability for up to 10 Devices Connect and expand your USB-C laptop to accommodate up to 10 must-need devices. Quickly turn your MacBook or Windows laptop or tablet into a powerhouse of productivity through a single USB-C cable. Connect a wide variety of devices such as a full- sized keyboard and mouse, an external hard drive, a printer, a microphone, headphones or speaker set, and transfer files through its built-in SD/MicroSD card reader. Enjoy the flexibility of the dock's versatile video options including 4K resolutions through the HDMI or Mini DisplayPort connections or 1080p video through the VGA port. Quickly connect up to 10 devices through one USB-C cable Works with the latest USB-C iPad Pro (2018 late) under mirror-mode Charge laptop & devices with up to100W pass-through1&2 Fast Role Swap provides safe operation for connected devices during 1 Power Delivery 3.0 pass0through offers up to 100W of charging power power changes utilizing the laptop's USB-C power adapter. USB-C power adapter not Versatile video options: HDMI (4K), Mini DisplayPort (4K) or VGA included. (1080p) 2 Maximum of up to 85W of power can be delivered to the laptop after Dual video outputs available via HDMI & Mini DisplayPort for up to deduction of 15W used by the docking station. -

Mini Displayport +Toslink Audio Tohdmi Adapter

Best Connectivity www.LogiLink.com Art No. CV0043 Mini DisplayPort +Toslink Audio toHDMI Adapter Mini DisplayPort of MacBook can only transmit video signal but no audio. However, this unique designed Adapter solved this trouble for users. It integrates Mini DisplayPort video signal and digital audio signal from MacBook into HDMI output. To connect the digital audio through stereo port, a piece of special fiber cable is provided by us. It allows users to enjoy perfect image and sound on HDTV. Feature: • Supports Mini DisplayPort 1.1a input, USB 2.0 input and HDMI High Speed output • Works by integrating mini DisplayPort video source and digital audio source of the MacBook into HDMI output • Supplied a piece of special fiber cable • Powered from Mini DisplayPort and USB Port • Supports HDMI 225MHz/2.25Gbps per channel (6.75 Gbps all channel) bandwidth. • Supports HDMI resolution of max up to 1080p • Supports HDMI 12bit per channel (36bit all channel) deep color • Supports uncompressed audio such as LPCM Package Contents: • 1 x Main Unit • 1 x Special Fiber Cablel Packaging Information: • Packing Dimension: 162x230x2 mm • Packing Weight: 0.12kg • Carton Dimension: 570x420x260 mm • Carton Q'ty: 90pcs • Carton Weight: 12.5kg CV0043 * The specifications and pictures are subject to change without notice. *All trade names referenced are the registered namework of their respective owners. Made in China - 1 - Best Connectivity www.LogiLink.com Art No. CV0043 Mini DisplayPort +Toslink Audio toHDMI Adapter Specification: Signal Inputs/Output Input -

USB-C to HDMI Adapter with USB-A Hub, Gigabit Ethernet

USB-C to HDMI Adapter with USB-A Hub, Gigabit Highlights Ethernet, Thunderbolt 3, 4K - PD Charging, 30 ● Transmits DisplayPort signals Hz, Black from sources supporting USB DisplayPort Alt Mode MODEL NUMBER: U444-06N-H4GUBC ● Delivers UHD picture quality at resolutions up to 3840 x 2160 (4K x 2K) @ 30 Hz ● Connects you to a wired Ethernet network when no Wi-Fi is available ● Powers and charges PD Charging-compliant devices, such as MacBooks and Chromebooks ● Easy installation with plug-and- play operation—no software required Features Applications Mini Docking Station Turns Your Device’s USB-C or Thunderbolt 3 Port into a Multiport Workstation ● Play 4K video from your laptop This USB 3.1 to HDMI adapter expands the potential of your tablet, laptop, Chromebook, MacBook, or PC on an HDMI display, such smartphone or PC’s USB-C or Thunderbolt 3 port. It’s ideal for transmitting digital audio and 4K video to a large display, adding a thumb drive or other USB peripheral, powering and charging a PD Charging- as an HDTV or projector compliant mobile device, and connecting to a Gigabit Ethernet network—all at the same time. ● Access a wired Ethernet network in a location with no or Supports USB DisplayPort Alternate Mode for Transmitting Audio/Video DisplayPort and USB Signals spotty Wi-Fi With a source device that also supports USB DisplayPort Alt Mode, you can extend video from your ● Transfer data from a USB flash primary display to another, duplicate the same video on both displays, or change the second display to drive or connect your computer your primary. -

Displayport to HDMI Converter Cable - 6 Ft (2M) - 4K

DisplayPort to HDMI Converter Cable - 6 ft (2m) - 4K Product ID: DP2HDMM2MB This 6-foot (2M) DisplayPort™ to HDMI® adapter cable lets you connect your DisplayPort equipped Ultrabook™, laptop or desktop computer to an HDMI display or projector with no additional adapters or cables required. The passive adapter supports video resolutions up to Ultra HD 4K. Astonishing picture quality This adapter cable ensures you can maintain an astonishing picture quality, four times the resolution of 1080p, when converting DisplayPort to HDMI. The adapter is also backward compatible with lower resolution displays and video sources. With support for high-definition resolutions of 1080p and 720p, you can future-proof your existing setup for 4K video. www.startech.com 1 800 265 1844 Hassle-free setup For the simplest and most discreet installation, this DP to HDMI adapter connects directly from your DisplayPort video source to the HDMI port on your display. It doesn't need a power source, unlike some converter dongles that require active power and separate bulky video cabling. Clutter-free installation At 6ft (2m) in length, this adapter cable delivers a compact connection that eliminates excess to ensure a tidy, professional installation. For shorter installations, we also offer a 3 ft DP to HDMI cable (DP2HDMM1MB), enabling you to choose the right cable length for your custom installation needs. The DP2HDMM2MB is backed by a 2-year StarTech.com warranty and free lifetime technical support. www.startech.com 1 800 265 1844 Certifications, Reports Applications -

State of Michigan Monitor Comparison Guide

State of Michigan Monitor Comparison Guide As of 08/23/2021 For the purpose of this document, we define a monitor as a display screen to provide visual output from a computer, desktop, laptop, or tablet. There are three (3) monitors that are available in Sigma: the Dell 24” Ultrasharp (D123), Dell 27” monitor (D104), and the Dell 24” Touch monitor (T36). NOTE: Numbers listed in this document (DXX, LXX, TXX) are Sigma numbers. Details on each model are on the following pages Dell P2418HT 24” Touch Monitor (T36) – $239.99 This monitor is 24 inches, measured from corner to corner. Full HD with a resolution of 1920 x 1080. 10- point touch system. Articulating monitor stand. Technical Specifications • Diagonal size: 24” • Aspect ratio: Widescreen (16:09) • Resolution: Full HD 1920 X 1080 • Contrast ratio: 1000:1 • Brightness: 250 cd/m2 • 1 x HDMI • 1 x DisplayPort • 1 x VGA • Size without Stand: 21.17” X 2.13” X 12.65” • Weight: 6.88lbs • Cables included: 1 x VGA cable, 1 x DisplayPort cable, 1 x USB cable SOM-Monitor Standard FY21 v13.0 JS Dell U2422H 24” Ultrasharp Monitor (D123) – $209.00 This monitor is 24 inches, measured from corner to corner. Full HD with a resolution of 1920 x 1080. Technical Specifications • Diagonal size: 24” • Aspect ratio: Widescreen (16:09) • Resolution: Full HD 1920 X 1080 • Contrast ratio: 1000:1 • Brightness: 250 cd/m2 • 1 x HDMI port • 1 x DisplayPort (out) • 1 x USB-C upstream port (data only) • 2 x Super speed USB 10Gbps (USB Gen 2) Type-A • 1 x Super speed USB 10Gbps (USB 3.2 Gen 2) Type-A w/power charging • 1 x USB-C downstream port (10Gbps, 15W) • Size with Stand: 21.7” X 7.07” X 14.33” • Weight: 7.75lbs SOM-Monitor Standard FY21 v13.0 JS Dell P2719H 27” Monitor (D104) – $245.00 This monitor is 27 inches, measured from corner to corner. -

Overview of Digital and Analog Connections Digital Video

Overview of Digital and Analog Connections Digital Video connectors are used to deliver the highest quality video signal. The technology uses TMDS (Transition Minimized Differential Signaling) to transmit large amounts of digital data from the source to the display, resulting in a high-quality image. DVI (Digital Visual Interface) was developed by the industry governing organization DDWG (Data Display Working Group) to send digital information from a computer to a digital display, such as a flat-panel LCD monitor. HDMI took a step forward by integrating audio and video into a more compact interface. DisplayPort is an interface technology that is designed to connect high-graphics capable PCs and displays as well as home theater equipment and displays. DisplayPort is similar to HDMI in that the DisplayPort signal carries both digital audio and video. HDMI HDMI stands for High Definition Multimedia Interface. This technology carries the same video information as DVI but adds the capacity for digital audio and control signals as well. The current version of HDMI carries one TMDS link of digital video. Found on many home-theater/consumer electronics devices, HDMI uses a 19-pin connector that is held in place by friction. This connector is technically described as a Type A HDMI connector. See our Available HDMI Cables HDMI Mini The Type C connector HDMI, the HDMI mini connector has the same number of pins but with its compact size, it is used for portable devices. See our Available HDMI Mini Cables DisplayPort™ DisplayPort™ is an interface technology that is designed to connect high-end graphics capable PCs and displays as well as home theater equipment and displays. -

USB 3.0 to Displayport External Video Card Multi Monitor Adapter – 2560X1600 Startech ID: USB32DPPRO

USB 3.0 to DisplayPort External Video Card Multi Monitor Adapter – 2560x1600 StarTech ID: USB32DPPRO The USB32DPPRO USB 3.0 to DisplayPort® Multi Monitor Adapter functions as an external DisplayPort video card, turning an available USB 3.0 port into a DisplayPort output, with support for high resolution 2560x1600 video, and 5.1 surround sound audio. The USB 3.0 DisplayPort adapter delivers a convenient, high-performance external video solution that makes it easy to add multi-monitor capability to a USB 3.0-enabled desktop or laptop computer (optimal performance from USB 3.0, backward compatible with USB 2.0). Leveraging the high-bandwidth (5 Gbps) SuperSpeed USB 3.0 interface, the adapter delivers smooth, high- definition content to your DisplayPort-capable display, and can be used to mirror your primary desktop, showing the same image on each display, or to extend your desktop to double your workspace and increase your productivity. Backed by a StarTech.com 2-year warranty and free lifetime technical support. Recommended System Requirements: CPU: Quad Core 2.4GHz or Higher (i5 recommended) RAM: 4GB or higher www.startech.com 1 800 265 1844 Applications Add a secondary DisplayPort display and extend your desktop, without taking apart your computer to install a new video card Add multi-monitor capability to a single computer, to enhance multimedia presentations Great for researchers and writers, offering the ability to have reference material on one display while working on a separate document on another Increase productivity by running -

Thunderbolt 3 to 10Gbe NIC Chassis + Card

Thunderbolt 3 to 10GbE NIC Chassis + Card Product ID: BNDTB10GI This Thunderbolt™ 3 to 10GbE NIC lets you connect your Thunderbolt 3 enabled device to a 10 GbE network. This adapter combines the StarTech.com Thunderbolt 3 PCIe Expansion Chassis (TB31PCIEX16) and the PCI Express 10G NIC (ST10000SPEXI), giving you one DisplayPort output, one additional Thunderbolt 3 port and one RJ45 (10GbE) port. www.startech.com 1 800 265 1844 Reliable, high-performance and versatile multimode connectivity This 10G network card utilizes the Intel® X550 chipset with Intel® Virtualization Technology for connectivity, delivering the power, performance and enhanced capabilities you need for dependable network connections. Install and assemble with ease Requiring only a Phillips type screwdriver, this Thunderbolt 3 to 10GbE NIC can be assembled and connected in minutes. It connects easily through a single Thunderbolt 3 port on your computer. Change up your chassis The Thunderbolt 3 chassis not only pairs well with the 10GbE NIC--you can swap the NIC out for other PCIe cards, to help support other functionality and performance. With the extra TB3 port and DP output built into the chassis, you will always have the ability to hook up extended displays to effortlessly multitask. The TB31PCIEX16 and ST10000SPEXI are backed by a StarTech.com 2-year warranty. www.startech.com 1 800 265 1844 Certifications, Reports Applications and Compatibility • Upgrade your workstation to provide enhanced performance, advanced features and greater reliability • Upgrade a 10/100/1000