Charge Pump IC Test Plan

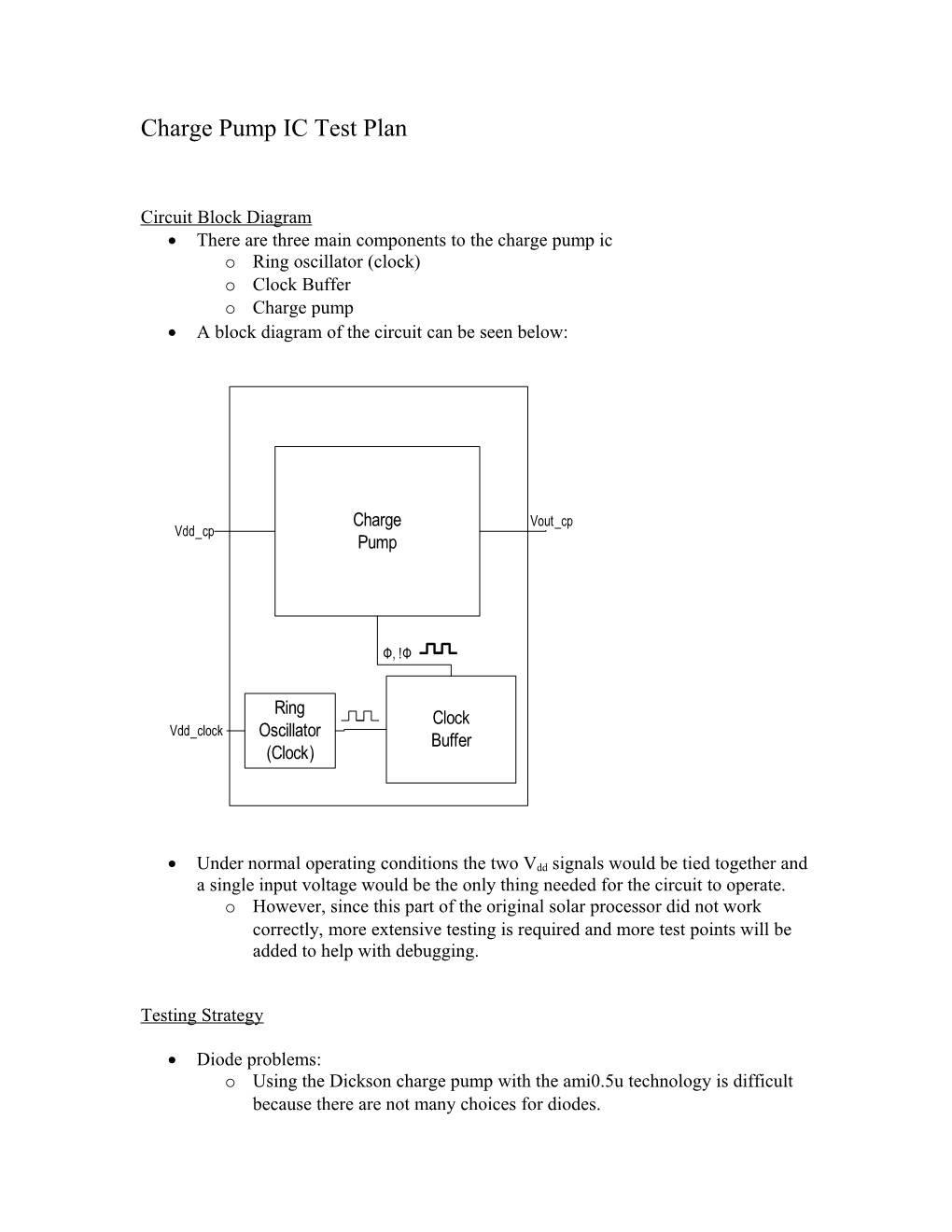

Circuit Block Diagram There are three main components to the charge pump ic o Ring oscillator (clock) o Clock Buffer o Charge pump A block diagram of the circuit can be seen below:

Charge Vout_cp Vdd_cp Pump t e x t

Φ, !Φ

Ring Clock Vdd_clock Oscillator Buffer (Clock)

Under normal operating conditions the two Vdd signals would be tied together and a single input voltage would be the only thing needed for the circuit to operate. o However, since this part of the original solar processor did not work correctly, more extensive testing is required and more test points will be added to help with debugging.

Testing Strategy

Diode problems: o Using the Dickson charge pump with the ami0.5u technology is difficult because there are not many choices for diodes. o To make a diode, the drain-body junctions of PMOS were used. These parasitic diodes are not modeled well in simulation and varying their width areas does not show much change in their conductivities. o The IC has been designed with this in mind. If the large diode-connected PMOS do not function properly, the design allows for discrete diodes to replace them. o Problems may include: Recovery times being too long. Parasitic effects negating current/power flow. Junction areas being too small to efficiency charge such large capacitors. The figure below shows the signals that can be taken off-chip for testing/debugging: S2_in S3_in S4_in

S1_out S2_out S3_out

cp_in cp_out

Φ2_in !Φ_in Φ1_in Φ Vdd_clock Clock Clock Buffer !Φ

Clock signal o The clock is generated using relatively small transistors and must be buffered to drive the large charge pump capacitors. This signal is taken off-chip after the buffer, because stray capacitance would degrade the un- buffered clock signal. o The clock signal is brought back into the chip separately for each of the three capacitors. This allows for them to be driven by another source if the clock signal and buffer are inadequate to drive them properly. Vdd’s o Separate Vdd signals are used for the clock and for the charge pump in order for the two to be decoupled. Also, clock frequency is a strong function of Vdd and the buffer may not be strong enough to charge the caps at high frequencies. Diodes o The diodes are wired in such a way that if they can be completely replaced by external components if they appear to be functioning poorly. A small resistance is introduced to the internal diodes by the jumpers needed to connect them, but this should only be few ohms or less.

Test Procedure I. Clock signal test a. Voltage is only applied to the Vdd_clock pin and the Vdd for the voltage protection diodes. b. Clock frequency is measured as Vdd_clock is varied over the range of input voltages. i. 0.7-1.5V (possibly higher) c. The capacitive load on the output of the clock is increased to determine the functional range that the buffer can drive. II. Charge pump test (using on-chip clock) a. Jumpers are attached from the outputs to the inputs of the next stage between the diodes. b. Apply the Vdd and gnd for the safety diodes. c. Separate voltages sources are applied to the Vdd_clock and Vdd_cp. i. This allows the frequency to be independently controlled. d. A small capacitive load is initially attached to the output of the chargepump. i. This is gradually increased if the smaller load works. ii. Transient charging times can be observed with changes in the load capacitance. e. Each of the two Vdd signals is swept while the other is held constant. i. This allows for the charging time and power to be observed as a function of frequency. III. Charge pump test(using off-chip clock) a. This is only necessary if the on-chip clock does not work or if it is not strong enough to properly drive the caps. b. Jumper the diodes in the same way as test II. c. Do not apply Vdd_clock. Get the clock signal from an external square- wave generator. There needs to be phi and !phi(anti-phase clock signals), so an ic may need to be used if a suitable square wave generator is not available. d. Apply Vdd_cp to the input of the charge pump. e. Sweep the frequency of the clock signals and see how output power is affected. f. Sweep the input voltage at several frequencies and see how output voltage and transient charging are affected. IV. Circuit testing using discretes a. Instead of using jumpers to connect the internal diodes, place the external diodes between the input stages. b. If the internal clock is functioning, it is used. Otherwise use an external clock, as mentioned above, is used. c. The frequency and charge pump input voltage are swept and power measurements are taken. V. Power Measurements a. Power measurements can be taken by placing a large resistor in series with the reservoir capacitor. i. This will slow the charging time down a lot. b. The power is I^2*R. The resistor can be varied to find the max power. i. This is the maximum power delivered that will not cause the voltage to drop far (%10) the steady state maximum voltage.