Register Transfer Logic

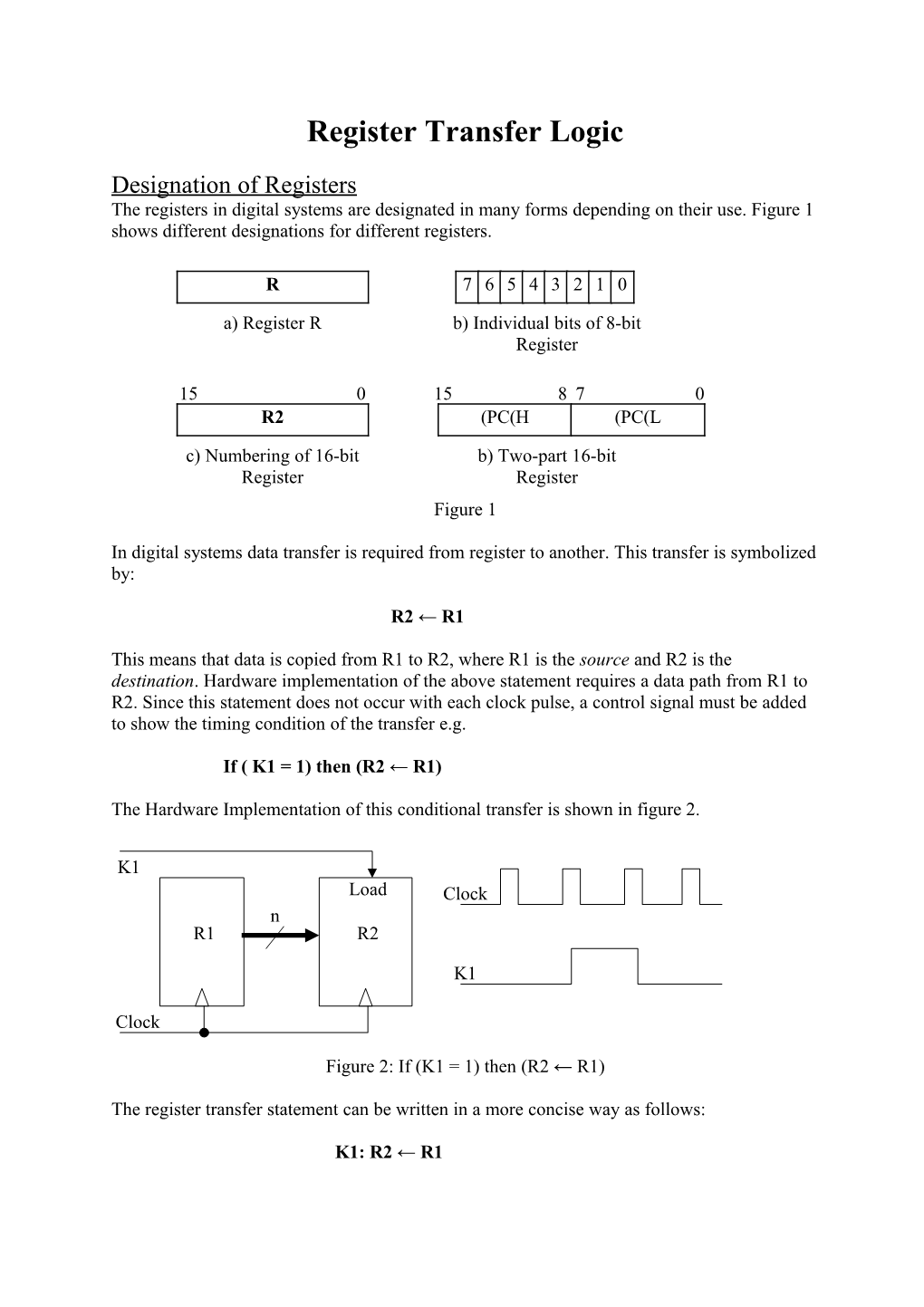

Designation of Registers The registers in digital systems are designated in many forms depending on their use. Figure 1 shows different designations for different registers.

R 7 6 5 4 3 2 1 0

a) Register R b) Individual bits of 8-bit Register

15 0 15 8 7 0 R2 (PC(H (PC(L

c) Numbering of 16-bit b) Two-part 16-bit Register Register Figure 1

In digital systems data transfer is required from register to another. This transfer is symbolized by:

R2 ← R1

This means that data is copied from R1 to R2, where R1 is the source and R2 is the destination. Hardware implementation of the above statement requires a data path from R1 to R2. Since this statement does not occur with each clock pulse, a control signal must be added to show the timing condition of the transfer e.g.

If ( K1 = 1) then (R2 ← R1)

The Hardware Implementation of this conditional transfer is shown in figure 2.

K1 Load Clock n R1 R2

K1

Clock

Figure 2: If (K1 = 1) then (R2 ← R1)

The register transfer statement can be written in a more concise way as follows:

K1: R2 ← R1 where the control condition is a Boolean function terminated by a colon.

The following table gives the basic symbols used in register transfer notation:

Symbols Description Examples Letters Denotes a register AR, R2, DR, IR (and Numerals) ( ) Denotes a part of register R2(1), R2(7:1), AR(L) ← Denotes transfer of data R1 ← R2 , Separates simultaneous transfer R2 ← R1, R1 ← R2 [ ] Specifies a memory address DR ← M[AR]

Sometimes it is required to transfer data from two sources to one destinations at different timing conditions. For example consider the following statement:

If ( K1 = 1) then (R0 ← R1) else If ( K2 = 1) then (R0 ← R2) or

K1: R0 ← R1, K1 K2: R0 ← R2

This statement can be implemented as shown in figure 3 assuming 4- bit Registers.

K2 4 K1 R2 S 4 Load 0 MUX R0 1 4 R1

Figure 3.

Note that the multiplexer shown in figure 3 is dedicated to R0. if R2 and R1 are also used as destination for some transfer statements, a dedicated multiplexer will be required for each destination register. In this case the system will be as shown in figure 4. This configuration is called Multiplexed-Based Transfer. For 3 n-bit registers this configuration uses three n-bit 2;1 multiplexers, each with its own select signal and each register has its own load signal. If the number of registers increased the number of interconnections for this configuration will be increased. Another effective and simpler configuration is the single shared Bus. The bus is characterized by a set of common lines driven by selection logic and the control logic selects a single source and one or more destinations during the clock time of the transfer. The Bus configuration for 3 n-bit registers uses single n-bit 3:1 multiplexer and parallel load registers. Figure 5 shows the single shared bus equivalent to the Multiplexed-based Transfer shown in figure 4. The disadvantage of the bus configuration is that it is impossible to transfer the contents of 2 sources simultaneously in one clock cycle. Assuming that single-source transfer is required for each clock cycle, the bus configuration will be better than the multiplexed-base transfer. n n

n L0 S0 L1 S1 L2 S2 1 0 S S 1 0 S 1 0 n 2:1 MUX n 2:1 MUX n 2:1 MUX n n n Load R0 Load R1 Load R2

Figure 4 : Dedicated multiplexers transfer

Another construction is possible for the Bus transfer using three-state buffers instead of multiplexers. This construction is further reducing the number of connections. Using three- state buffers is better than multiplexers because three-state buffers are single-level logic gates, while the multiplexers are two-level logic gates. Another advantage for the three-state buffers is that many of the buffer outputs can be connected together to for one bit line. n n

S0 2 1 0 Select S0 S1 n 3:1 MUX n S1 n

Load Load L0 R0 R1 Load R2 L1 L2

Figure 5 : Single Bus transfer

The three-state buffers bus has another advantage. It can use the same lines as input or output to the logic gates. Figure 6a shows an n-bit register with n lines used as both output and inputs. The figure also gives the symbol used for n lines bidirectional buffered register. If the buffers are enabled the lines serve as output, and they serve as inputs if the buffers are disabled. For comparison, the multiplexed bus used with 3 registers requires 6 connections per bit. For three-state buffer bus the same configuration requires 3 connections only per bit. Figure 6b shows the three-state buffer Bus in case of three three-state buffered registers with parallel load and three enable signals. En Load Enable L0L1L2 E0E1E2 LOAD R n n n

Load

R0 R1 R2 R n n n n n Bus En a) bidirectional register b) three-state bus using and its symbol bidirectional register and its symbol

Figure 6

Memory Transfer

n address R lines MAR 2n * m bits (n bits) Memory W

m data lines MBR (m bits)

Figure 7: Memory unit

The memory unit is shown in fig 7. It consists of MAR (Memory Address Register), MBR (Memory Buffer Register) and the memory array. If the memory size is 2n * m bits, then the size of the MAR should be n bits and the size of the MBR is m bits.

Memory unit is used to store and retrieve data. There are two memory transfer operations: read and write. The Read operation is a transfer of data from the selected memory location into MBR. Selection of memory location is achieved by writing the address of the selected location into MAR. Read operation is symbolized by the following statement:

R: MBR ← M[MAR]

Where R is the control signal used with Read operations. The Write operation is a transfer of data from MBR into the selected memory location. Again the selection of memory location is achieved by writing the address of the selected location into MAR. Write operation is symbolized by the following statement:

W: MBR ← M[MAR]

Microprocessor Address MAR

Data MBR Memory Unit Read Control Internal Write Bus

Figure 8

The Access Time of memory unit must be synchronized with the master clock pulses of the system. In faster systems the memory access time may be shorter than or equal to the clock pulse period. In slow memories, it may be necessary to wait for a number of clock pulses for the transfer to be complete.

Address Data Write S1 S0 Bus Bus En S1 S0 Decoder 2:4 2:4 Decoder 3 2 1 0 0 1 2 3 En A0 B0 En Load

En A1 B0 En Load

En A2 B0 En Load

B0 En En A3 Load

0 1 2 3 2:4 Decoder En S1 S0 Figure 9 Read the memory unit is not a part of the microprocessor chip in most cases, while the MAR and the MBR are registers inside the microprocessor. Thus both MAR and MBR have two buses one external for connection with memory and the other is internal for connecting with the internal microprocessor Bus. This is shown in figure 8.

In some systems the memory unit receives addresses and data from many registers connected to common buses. Figure 9 shows a memory unit receives address from 4 address registers (A0, A1, A2, and A3) and the memory data bus is also connected to 4 data registers (B0, B1, B2, and B3). In this system three-state buffer buses are used for transferring data and addresses. Multiplexed Bus may also be used but the three-state buffer bus is simpler.

In single bus all the CPU registers, ALU and the instruction decoder are connected to the bus. This bus is a single shared three-state buffer bus and it is shown in figure 10. Memory Bus

Address Data Lines Lines

Operand Address A and IR PC MAR MDR Y ALU Z instruction decoder B

Internal CPU Bus

Figure 10

The Instruction Format The Instructions of any CPU take one of the following format depending on the kind of the instruction: 1. Implied 2. Immediate operand 3. Direct address operand 4. Indirect address operand

The Implied format instruction consists of just operation code for the instruction or operation. The operation code does not need to any parameter or operand.

The Immediate operand format instruction consists of the operation code of the instruction followed immediately by the operand. The Direct address operand format instruction consists of the operation code of the instruction followed by the address of the operand. The operand address may be a location in memory and this is called direct addressing. The operand of the instruction may also located in one of the CPU registers. In this case the instruction is called register direct addressing or simply register addressing.

The Indirect address operand format instruction consists of the operation code of the instruction followed by a location for the address of the operand. This location may be a location in memory containing the address of the operand and this is called indirect addressing. The location may also be one of the CPU registers. In this case the instruction is called register indirect addressing or simply indirect register addressing. A displacement value may be added to the contents of the memory or the register to calculate the address.

Figure 11 shows the different instruction formats.

Operation code Operation code Operand

a) Implied b) Immediate operand

Operation code Direct Address Operation code Indirect Address

c) Direct Addressing d) Indirect Addressing

Figure 11: Instructions Format 8086/8088 Microprocessor

The internal architecture of the 8086/8088 microprocessor is as shown in figure 1. The processor contains the following units:

Figure 1: Internal structure of the 8086/8088 microprocessor

Bus Interface Unit (BIU): generates the memory and IO addresses for the transfer of data and instructions and realize these transfers. BIU for the 8086 is 16 bits, while the BIU of the 8088 is 8 bits. It consists of the following parts:

- Instruction pointer IP for generating the offset address of the instructions.

- 4 Segment registers for generating the segment address of instructions and data (CS, DS, SS, and SS).

- 20-bit adder for generating physical address.

- Instruction queue for storing the fetched instructions.

The BIU unit generates the 20-bit address by adding the segment address multiplied by 16 with the offset address as follows:

Physical Address (20-bit) = Segment base (16-bit) * 16 + offset (16-bit) Generation of physical addressing is shown in figure 2.

16-bit segment base 0 0 0 0 16-bit segment base

+

20-bit Physical Address

Figure 2; generation of physical address

The sources of the offset and the segment base depend on the instruction. For example:

* Fetching instruction takes the offset from IP and segment base from CS.

* All instructions except those related to the stack use DS or ES as a segment base and offset calculated from the instruction itself.

* The stack instructions use SS as a segment base and offset calculated from the instruction itself.

The Instruction queue is used to store the prefetched instructions. These instructions are fetched during the execution of previous instructions to safe time.

Execution Unit (EU): receives program instruction codes and data from the BIU, executes these instructions and stores the results either in the general registers or output them through the BIU. It has no connections to the system busses. It receives and outputs all its data through the BIU. The BIU consists of the following parts:

* Control unit: used to decode and control the different parts of the EU during execution of the instructions. It also generates the control signals required to execute the prefetched instructions.

* General Purposes Registers: These registers are used to give the operand or (and) store the result of the instructions. They are 4 16-bits registers as follows: • AX - the accumulator register (divided into AH / AL). It uses to give the operand or (and) store the result of the instructions. • BX - the base address register (divided into BH / BL). It uses to give the operand or (and) store the result of the instructions. It may hold the address of some instructions • CX - the count register (divided into CH / CL). It uses to give the operand or (and) store the result of the instructions. It is used as a counter with some instructions. • DX - the data register (divided into DH / DL). It uses to give the operand or (and) store the result of the instructions. * Index and Pointers Registers: These are 4 16-bits registers as follows: • SI - source index register. • DI - destination index register. • BP - base pointer. • SP - stack pointer. These registers are uses as pointer or index for calculating the offset of the address of many instructions.

* Special Purposes Registers: The following Registers are special purposes registers: • IP – Instruction Pointer. • FLAGS - Flags register.

Both BIU and EU are working in parallel, which means that, when the BIU fetches an instruction the EU executes a prefetched instruction.

Memory addressing of the 8086/8088:

Figure 3: the general purpose registers, Segment registers and the Flag register of the 8086/8088 microprocessors

The memory size of the 8086/8088 microprocessor is 1 Mbyte. The size of the registers of the 8086/8088 used for addressing memory is 16 bits only. This means that these registers can address 64 Kbytes of memory only. The 1 Mbytes memory is divided by this way into segments. The size of each segment ranges from 16 bytes to 64 Kbytes. This also means that the 1 Mbytes memory is divided into a number of segments between 16 and 64 K segments.

Since the size of the registers of the 8086/8088 is not enough for addressing 1 Mbytes memory, the absolute address (consists of 20 bits) is calculated - as shown in figure 2 - using 2 16-bit address components called Segment address (or segment number) and offset (or effective address). The source of the segment address is one of 4 segment registers depending on the instruction. The source of the offset, depending on the address modes of the CPU may be included with the instruction or the contents of one or more registers other than the segment registers. Table 1 gives the default 16-bit segment register and the source register of the offset for the instructions. Table 1 Segment Address Offset Instruction kind CS IP Instruction address (code segment) SS SP or BP Stack Address (Stack Segment) DS BX, DI, SI, 8-bit number Data address (Data Segment) or 16-bit number ES DI for string instructions String destination address (Data Segment)

Addressing Modes of 8086/8088 microprocessor:

The operand of the instructions of any microprocessor is given in many forms as mentioned before in the instruction format section. For the 8086/8088 microprocessors the two registers BP and BX are called BASE REGISTERS and the DI and SI registers are called the INDEX REGISTERS. The operand of the instructions of the 8086/8088 microprocessor is given in one of the following forms called addressing modes:

1. Register Addressing: Which means that a register contains the operand. (e.g. MOVE AL,BL, MOVE AX,BX, ADD AX,CX).

2. Immediate Addressing: This means that the operand immediately follows the OpCode (Operation Code) of the instruction in memory. (E.g. MOVE AL,5, MOVE AX,0BC30H, ADD AX,50).

3. Direct Addressing: In this mode the operand of the instruction is located in a memory location and the address of this location is immediately follows the OpCode (Operation Code) of the instruction in memory. This address is called the Effective Address (EA) (or Offset). The absolute address is the sum of the contents of DS multiplied by 16 plus the EA. (E.g. MOVE AL,LISTB, MOVE AX,LISTW, ADD AX,LISTW where LISTB and LISTW are a byte-sized location and a word-sized location in memory respectively).

4. Register Indirect addressing: In this mode the address of the operand (EA) of the instruction is stored in one of the base registers or index register. The absolute address is the sum of the contents of DS (or SS depending on the register used in addressing. Refer to Table 1) multiplied by 16 plus the EA. (E.g. MOVE AL,[BX], ADD AX,[BX]).

5. Register relative addressing: In this mode the address of the operand (EA) of the instruction is the sum of the contents of one of the base registers or the index registers plus a displacement. The absolute address is the sum of the contents of DS (or SS depending on the register used in addressing. Refer to Table 1) multiplied by 16 plus the EA. (E.g. MOVE AL,[BX]ARRAY, ADD AX,[BX+5]).

6. Base Plus Index addressing: In this mode the address of the operand (EA) of the instruction is the sum of the contents of one of the base registers plus the contents of one of the index registers. The absolute address is the sum of the contents of DS (or SS depending on the register used in addressing. Refer to Table 1) multiplied by 16 plus the EA. (E.g. MOVE AL,[BX+DI], ADD AX,[BX+SI]). 7. Base-Relative Plus Index addressing: In this mode the address of the operand (EA) of the instruction is the sum of the contents of one of the base registers plus the contents of one of the index registers plus a displacement. The absolute address is the sum of the contents of DS (or SS depending on the register used in addressing. Refer to Table 1) multiplied by 16 plus the EA. (E.g. MOVE AL,[BX+DI]ARRAY, ADD AX,[BX+SI+5]).

Absolute Addresses Calculation:

In the 8086/8088 any program consists of at least 3 segments: code segment that contains the instructions of the program, data segment that contains the data of the program and the stack segment. Accessing the different segments of the program requires two address components offset or Effective Address (AE) and Segment Number or address. The sources of these addresses differ from segment to another. To fetch an instruction (accessing the code segment), the absolute address is calculated as follow:

Absolute Address (code segment) = CS * 16 + IP

Where CS is the contents of the Code Segment Register and IP is the Instruction Pointer contents.

Accessing data segment, depends on the addressing mode of the instruction. For example, to access data segment for executing the instruction MOV AX,[BX] the absolute address is calculated as follow:

Absolute Address (data segment) = DS * 16 + BX

To execute the instruction PUSH AX , which access the stack segment, the absolute address is calculated as follow:

Absolute Address (data segment) = SS * 16 + SP

Example: Suppose that the register contents of some of the 8086/8088 registers are as follows: DS = 0200H, SS = 0100H, BX = 0300H, SP = 0300H, DI = 0400H, and SI = 0200H. If the displacement LIST = 0250H, calculate the Effective Address (EA) and the Absolute Address of the following instructions: a) MOV AL, [1234H] b) MOV LIST[DI],AL c) MOV CH,[BX+SI] d) PUSH SI

Solution: a) This instruction is a Direct Addressing Instruction, thus the EA or Offset is a part of the instruction. The Offset is 1234H and the segment address is contained in DS. The Absolute Address is 200H * 10H + 1234H = 3234H. b) The addressing mode of this instruction is Register Relative Addressing. Thus: The EA or Offset of this instruction = DI + LIST = 400H + 250H = 650H The Absolute Addressing = 200H * 10H + 650H = 2650H c) The addressing mode of this instruction is Base Plus Index Addressing. Thus: The EA or Offset of this instruction = SI + BX = 200H + 300H = 500H The Absolute Addressing = 200H * 10H + 500H = 2500H d) The addressing mode of this instruction is Register Addressing which uses both SS and SP registers for addressing. Thus: The EA or Offset of this instruction = contents of SI = 200H The Absolute Addressing = 100H * 10H + 300H = 1300H

Instructions and OpCodes: Each assembly language instruction is translated into machine language instruction that is translated and executed inside the processor. The machine language code of the instructions depends on the instructions type and the addressing mode of the assembly language instructions. The translated machine code of each instruction varies according to the registers used in addressing the operand. This means that the same instruction mnemonic generate different opcode for different addressing modes. Table 7 gives a 8086/8088 instruction set summary. The table gives the mnemonics used with the different instructions, the operand used with this mnemonic, the opcode of the instruction and a brief description for the instruction. To generate the complete machine code of each instructions, it is required to replace the values of w, oo, reg and r/m. The w value if any depends on the length of the operand where w = 0 for one byte operand and w = 1 for 2-byte operand. The values of oo, reg and r/m are given in tables 2, 3, 4, 5 and 6 respectively. The Instruction Formats of the 8086/8088 are as follows:

1. One-Byte Instruction (Implied Operand)

OP Code

2. One-Byte Instruction (Register Mode) OP Code reg

3. Register to Register

OP Code 1 1 reg r/m

4. Register to/from memory with no displacement OP Code mod reg r/m

5. Register to/from memory with displacement OP Code mod reg r/m Low Disp. High Disp.

6. Immediate operand to Register OP Code 1 1 opcode r/m Low Data High Data

7. Immediate operand to Memory with 16-bit displacement OP Code 1 1 opcode r/m Low Disp. High Disp. Low Data High Data Table: 2 oo: Values oo Value Meaning 00 If r/m = 110, then a displacement follows the operation; otherwise, no displacement is used 01 An 8-bit signed displacement follows the opcode 10 A 16-bit signed displacement follows the opcode 11 r/m specifies a register, instead of an addressing mode

Table: 3 r/m : Values Table: 4 reg : Values r/m Value Meaning reg Value W = 0 W = 1 000 DS:[BX+SI] 000 AL AX 001 DS:[BX+DI] 001 CL CX 010 SS:[BP+SI] 010 DL DX 011 SS:[BP+DI] 011 BL BX 100 DS:[SI] 100 AH SP 101 DS:[DI] 101 CH BP 110 SS:[BP] 110 DH SI 111 DS:[BX] 111 BH DI

Table: 5 reg : Values reg Value Segment Registers 000 ES 001 CS 010 SS 011 DS

Table: 6: cccc : Values (Conditions of Jumps) cccc Value Mnemonic condition cccc Value Mnemonic condition 0000 JO Overflow 0001 JNO No Overflow 0010 JB/JNAE Below 0011 JNB/JAE Not Below 0100 JE/JZ Equal/zero 0101 JNE/JNZ Not Equal / Not Zero 0110 BE/NA Below or Equal / 0111 JNBE/A Not Below or Not Not Above Equal / Above 1000 S Sign 1001 NS Not Sign 1010 P/PE Parity / Even 1011 NP/PO Not Parity / Odd 1100 L/NGE Less than / Not 1101 NL/GE Not Less than / Greater or Equal Greater or Equal 1110 LE/NG Less than or Equal 1111 NLE/G Not Less than or / Not Greater than Equal / Greater than Table 7: 8086/8088 instruction set summary with OpCodes and brief descriptions Name Operand(s) Opcode Description AAA 00110111 ASCII Adjust After Addition AAD 1101010100001010 ASCII Adjust Register AX Before Division AAM 1101010000001010 ASCII Adjust AX Register After Multiplication AAS 00111111 ASCII Adjust AL Register After Substraction ADC Reg,Reg/Mem 0001001wooregr/m Add Integers with Carry Mem,Reg 0001000wooregr/m Add Integers with Carry Acc,Imm 0001010w Add Integers with Carry Reg/Mem,Imm 1000001woo010r/m Add Integers with Carry ADD Reg,Reg/Mem 0000001wooregr/m Add Integers Mem,Reg 0000000wooregr/m Add Integers Acc,Imm 0000010w Add Integers Reg/Mem,Imm 1000001woo000r/m Add Integers AND Reg,Reg/Mem 0010001wooregr/m Logical AND Mem,Reg 0010000wooregr/m Logical AND Acc,Imm 0010010w Logical AND Reg/Mem,Imm 1000000woo100r/m Logical AND CBW 10011000 Convert Byte to Word CLC 11111000 Clear Carry Flag (CF) CLD 11111100 Clear Direction Flag (DF) CLI 11111010 Clear Interrupt Flag (IF) CMC 11110101 Complement Carry Flag (CF) CMP Reg,Reg/Mem 0011101wooregr/m Compare Mem,Reg 0011100wooregr/m Compare Acc,Imm 0011110w Compare Reg/Mem,Imm 1000000woo111r/m Compare CMPSB 10100110 Compare String - Byte CMPSW 10100111 Compare String - Word CWD 10011001 Convert Word to Doubleword DAA 00100111 Decimal Adjust Register After Addition DAS 00101111 Decimal Adjust AL Register After Substraction DEC RegWord 01001reg Decrement by One Reg/Mem 1111111woo001r/m Decrement by One DIV Reg/Mem 1111011woo110r/m Unsigned Integer Divide HLT 11110100 Halt IDIV Reg/Mem 1111011woo111r/m Signed Divide IMUL Reg/Mem 1111011woo101r/m Signed Integer Multiply IN Acc,Imm8 1110010w Input from Port Acc,DX 1110110w Input from Port INC RegWord 01000reg Increment by 1 Reg/Mem 1111111woo000r/m Increment by 1 INT 3 11001100 Call to Interrupt Procedure Imm8 11001101 Call to Interrupt Procedure INTO 11001110 Interrupt on Overflow IRET 11001111 Return from Interrupt LAHF 10011111 Load Flags into AH Register LDS Reg16,Mem32 11000101ooregr/m Load Pointer Using DS LES Reg16,Mem32 11000100ooregr/m Load Pointer Using ES LEA RegWord,Mem 10001101ooregr/m Load Effective Address LODSB 10101100 Load Byte LODSW 10101101 Load Word

Name Operand(s) Opcode Description MOV MemOfs,Acc 1010001w Move Data Acc,MemOfs 1010000w Move Data Reg,Imm 1011wreg Move Data Mem,Imm 1100011woo000r/m Move Data Reg,Reg/Mem 1000101wooregr/m Move Data Mem,Reg 1000100wooregr/m Move Data Reg16/Mem16,Seg 10001100ooregr/m Move Data Seg,Reg16/Mem16 10001110ooregr/m Move Data MOVSB 10100100 Move Byte MOVSW 10100101 Move Word MUL Reg/Mem 1111011woo100r/m Unsigned Integer Multiply of AL, AX or EAX NEG Reg/Mem 1111011woo011r/m Negate(Two's Complement) NOP 10010000 No Operation NOT Reg/Mem 1111011woo010r/m Negate(One's Complement) OR Reg,Reg/Mem 0000101wooregr/m Logical Inclusive OR Mem,Reg 0000100wooregr/m Logical Inclusive OR Acc,Imm 0000110w Logical Inclusive OR Reg/Mem,Imm 1000000woo001r/m Logical Inclusive OR OUT Imm8,Acc 1110011w Output To Port DX,Acc 1110111w Output To Port CMP Reg,Reg/Mem 0011101wooregr/m Compare Mem,Reg 0011100wooregr/m Compare Acc,Imm 0011110w Compare Reg/Mem,Imm 1000000woo111r/m Compare CMPSB 10100110 Compare String - Byte CMPSW 10100111 Compare String - Word CWD 10011001 Convert Word to Doubleword DAA 00100111 Decimal Adjust Register After Addition DAS 00101111 Decimal Adjust AL Register After Substraction DEC RegWord 01001reg Decrement by One Reg/Mem 1111111woo001r/m Decrement by One DIV Reg/Mem 1111011woo110r/m Unsigned Integer Divide HLT 11110100 Halt IDIV Reg/Mem 1111011woo111r/m Signed Divide IMUL Reg/Mem 1111011woo101r/m Signed Integer Multiply IN Acc,Imm8 1110010w Input from Port Acc,DX 1110110w Input from Port INC RegWord 01000reg Increment by 1 Reg/Mem 1111111woo000r/m Increment by 1 INT 3 11001100 Call to Interrupt Procedure Imm8 11001101 Call to Interrupt Procedure INTO 11001110 Interrupt on Overflow IRET 11001111 Return from Interrupt LAHF 10011111 Load Flags into AH Register LDS Reg16,Mem32 11000101ooregr/m Load Pointer Using DS LES Reg16,Mem32 11000100ooregr/m Load Pointer Using ES LEA RegWord,Mem 10001101ooregr/m Load Effective Address LODSB 10101100 Load Byte LODSW 10101101 Load Word

Name Operand(s) Opcode Description POP RegWord 01011reg Pop a Word from the Stack MemWord 10001111oo000r/m Pop a Word from the Stack SegOld 00reg111 Pop a Word from the Stack POPF 10011101 POP Stack into FLAGS PUSH RegWord 01010reg Push Operand onto Stack MemWord 11111111oo110r/m Push Operand onto Stack SegOld 00reg110 Push Operand onto Stack PUSHF 10011100 PUSH FLAGS Rotate Left through Carry - Uses CF for RCL Reg/Mem,1 1101000woo010r/m Extension Rotate Left through Carry - Uses CF for Reg/Mem,CL 1101001woo010r/m Extension Rotate Right through Carry - Uses CF for RCR Reg/Mem,1 1101000woo011r/m Extension Rotate Right through Carry - Uses CF for Reg/Mem,CL 1101001woo011r/m Extension RET NEAR 11000011 Return from subprocedure RET imm NEAR 11000010 Return from subprocedure RET FAR 11001011 Return from subprocedure RET imm FAR 11001010 Return from subprocedure ROL Reg/Mem,1 1101000woo000r/m Rotate Left through Carry - Wrap bits around Reg/Mem,CL 1101001woo000r/m Rotate Left through Carry - Wrap bits around ROR Reg/Mem,1 1101000woo001r/m Rotate Right through Carry - Wrap bits around Reg/Mem,CL 1101001woo001r/m Rotate Right through Carry - Wrap bits around SAHF 10011110 Load Flags into AH Register SAL Reg/Mem,1 1101000woo100r/m Shift Arithmetic Left Reg/Mem,CL 1101001woo100r/m Shift Arithmetic Left SAR Reg/Mem,1 1101000woo111r/m Shift Arithmetic Right Reg/Mem,CL 1101001woo111r/m Shift Arithmetic Right SHL Reg/Mem,1 1101000woo100r/m Shift Logic Left Reg/Mem,CL 1101001woo100r/m Shift Logic Left SHR Reg/Mem,1 1101000woo101r/m Shift Logic Right Reg/Mem,CL 1101001woo101r/m Shift Logic Right SBB Reg,Reg/Mem 0001101wooregr/m Substract Integers with Borrow Mem,Reg 0001100wooregr/m Substract Integers with Borrow Acc,Imm 0001110w Substract Integers with Borrow Reg/Mem,Imm8 1000001woo011r/m Substract Integers with Borrow Reg/Mem,Imm 1000000woo011r/m Substract Integers with Borrow SCASB 10101110 Compare Byte SCASW 10101111 Compare Word STC 11111001 Set Carry Flag(CF) STD 11111101 Set Direction Flag(DF) STI 11111011 Set Interrupt Flag(IF) STOSB 10101010 Store String Data Byte STOSW 10101011 Store String Data Word SUB Reg,Reg/Mem 0010101wooregr/m Subtract Mem,Reg 0010100wooregr/m Subtract Acc,Imm 0010110w Subtract Reg/Mem,Imm8 1000001woo101r/m Subtract Reg/Mem,Imm 1000000woo101r/m Subtract Name Operand(s) Opcode Description TEST Reg,Reg/Mem 1000010wooregr/m Test Operands Mem,Reg 1000010wooregr/m Test Operands Acc,Imm 1010100w Test Operands Reg/Mem,Imm 1111011woo000r/m Test Operands WAIT 10011011 Wait for FPU AccWord,RegWor XCHG 10010reg Exchange d Reg,Reg/Mem 1000011wooregr/m Exchange XLAT 11010111 Translate XOR Reg,Mem/Reg 0011001wooregr/m Exclusive-OR Mem,Reg 0011000wooregr/m Exclusive-OR Acc,Imm 0011010w Exclusive-OR Reg/Mem,Imm 1000000woo110r/m Exclusive-OR CALL MemFar 11111111oo011r/m Call a Procedure Near 11101000 Call a Procedure Far 10011010 Call a Procedure RegWord/ 11111111oo010r/m Call a Procedure MemNear Jcc Short 0111cccc Jump on Some Condition Code JCXZ/JCXE Short 11100011 Jump if CX is zero or Equal zero JMP MemFar 11111111oo101r/m Jump Unconditional Short 11101011 Near 11101001 Far 11101010 RegWord/ 11111111oo100r/m MemNear LOOP Short 11100010 Loop Control While ECX Counter Not Zero LOOPZ/LOOPE Short 11100001 Loop while Zero LOOPNZ/LOOPNE Short 11100000 Loop while Not Zero LOCK 11110000 Assert Lock# Signal Prefix REP/REPE/REPZ 11110011 Repeat Following String Operation REPNE/REPNZ 11110010 Repeat while Not Equal CS: 00101110 CS segment override prefix DS: 00111110 DS segment override prefix ES: 00100110 ES segment override prefix SS: 00110110 SS segment override prefix PIN Description of the 8086/8088 microprocessor

Figure 3

Figure 3 shows the pin descriptions of the 8086/8088 microprocessor. This processor may work in one of 2 modes called Minimum mode (MN) and maximum mode (MX'). In the Minimum mode a DMA controller is connected to the external bus of the microprocessor. In the Maximum mode the arithmetic coprocessor 8087 is added to the 8086/8088 bus beside the DMA controller. Figure 4 shows The important groups of the 8086/8088 signals only which have a similar description in other microprocessors.

MN/MX' MN/MX' AD7-AD0 8086 CPU AD15-AD0 8088 CPU BHE'/S7 SS0 A15-A8 RD' A19-A16 / RD' LOCK WR' S6-S3 LOCK WR' A19-A16/S6-S3 'S2 IO/M' 'S2 IO/M' 'QS0 ALE INT 'QS0 ALE INT 'S0 DEN' NMI 'S0 DEN' NMI 'S1 DT/R' RESET 'S1 DT/R' RESET 'QS1 INTA CLOCK 'QS1 INTA CLOCK READY HOLD RQ/GT0 READY HOLD RQ/GT0 HOLDA RQ/GT1 HOLDA RQ/GT1 Figure 4: Important 8086/8088 Signals

8086/8088 Signals Functions Descriptions Signals Type Pins Minimum Mode Maximum Mode Direction

address/data bus Bidirectional, AD15-AD0 Address/ 3-state data/ status A19/S6- address/status bus output,3-state A16/S3 RD' read from memory/IO output,3-state Handshaking READY ready signal input for data read/write M/IO' / S2' select memory or IO output,3-state WR' / LOCK' Write to memory /IO output,3-state ALE Address latch enable output DT/R' / S1' data transmit/receive output DEN Data bus enable output BHE'/S7 bus high enable output INTR interrupt request input non-maskable input NMI Interrupt interrupt signals RESET reset input INTA' interrupt acknowledge output HOLD Hold request input

Bus access Hold output acknowledge,whether control HLDA the CPU is in hold state a status bit combined output SSO' with IO/M' and DT/R' test pin tested by input TEST' WAIT instruction Minimum/maximum input MN/MX' mode, 5V Others clock pin for basic input CLK timing signal power supply, +5.0V, Vcc ±10% ground connection, GND 0V

During the hold acknowledge, AD15-AD0,A19/S6-A16/S3,RD',M/IO',WR' pins are in high- impedance state.

Status bit s6 always remains a logic 0, bit s5 indicates the condition of the IF flag bit, and s4 and s3 show which segment is accessed during the current bus cycle.

Function of status bits s3 and s4

S4 S3 Function 0 0 ES, Extra segment 0 1 SS, Stack Segment 1 0 CS or no segment 1 1 DS, Data segment

Bus cycle status

The 8086/8088 processors use the memory and IO in periods of time called bus cycles. In 8086/8088 there are three basic cycles using data bus:

o Read bus cycle. reading instructions and data from memory or IO. o Write bus cycle. Writing data to memory or IO o Interrupt cycle. Getting interrupt vectors from interrupting devices. This is also a read operation.

IO/M' DT/R' SSO' Function 0 0 0 Interrupt acknowledge 0 0 1 Memory read 0 1 0 Memory write 0 1 1 Halt 1 0 0 Opcode fetch 1 0 1 IO read 1 1 0 IO write 1 1 1 Passive

Maximum mode operation

Maximum mode signals

Address/data/status address/data bus Bidirectional, AD15-AD0 3-state A19/S6-A16/S3 address/status bus output,3-state Handshaking for data read/write read from output,3-state RD' memory/IO READY ready signal input BHE'/S7 bus high enable output status/handshake bits output indicating the S2',S1',S0' function of the current bus cycle Interrupt signals INTR interrupt request input non-maskable input NMI interrupt RESET reset input Bus access control request/grant pins for bidirectional RO'/GT1',RO'/GT0' bus access used to lock the bus, output activated by LOCK LOCK' prefix on any instruction Others QS1,QS0 queue status output test pin tested by input TEST' WAIT instruction Minimum/maximum input MN/MX' mode, 0V clock pin for basic input CLK timing signal power supply, Vcc +5.0V, ground connection, GND 0V

Bus control functions

s2' S1' S0' Function 0 0 0 Interrupt acknowledge 0 0 1 Memory read 0 1 0 Memory write 0 1 1 Halt 1 0 0 Opcode fetch 1 0 1 IO read 1 1 0 IO write 1 1 1 Passive Maximum mode operation differs from minimum mode in that some of the control signals must be externally generated. This requires additional circuitry, however, a chip -the 8288 bus controller- designed for this purpose is available.