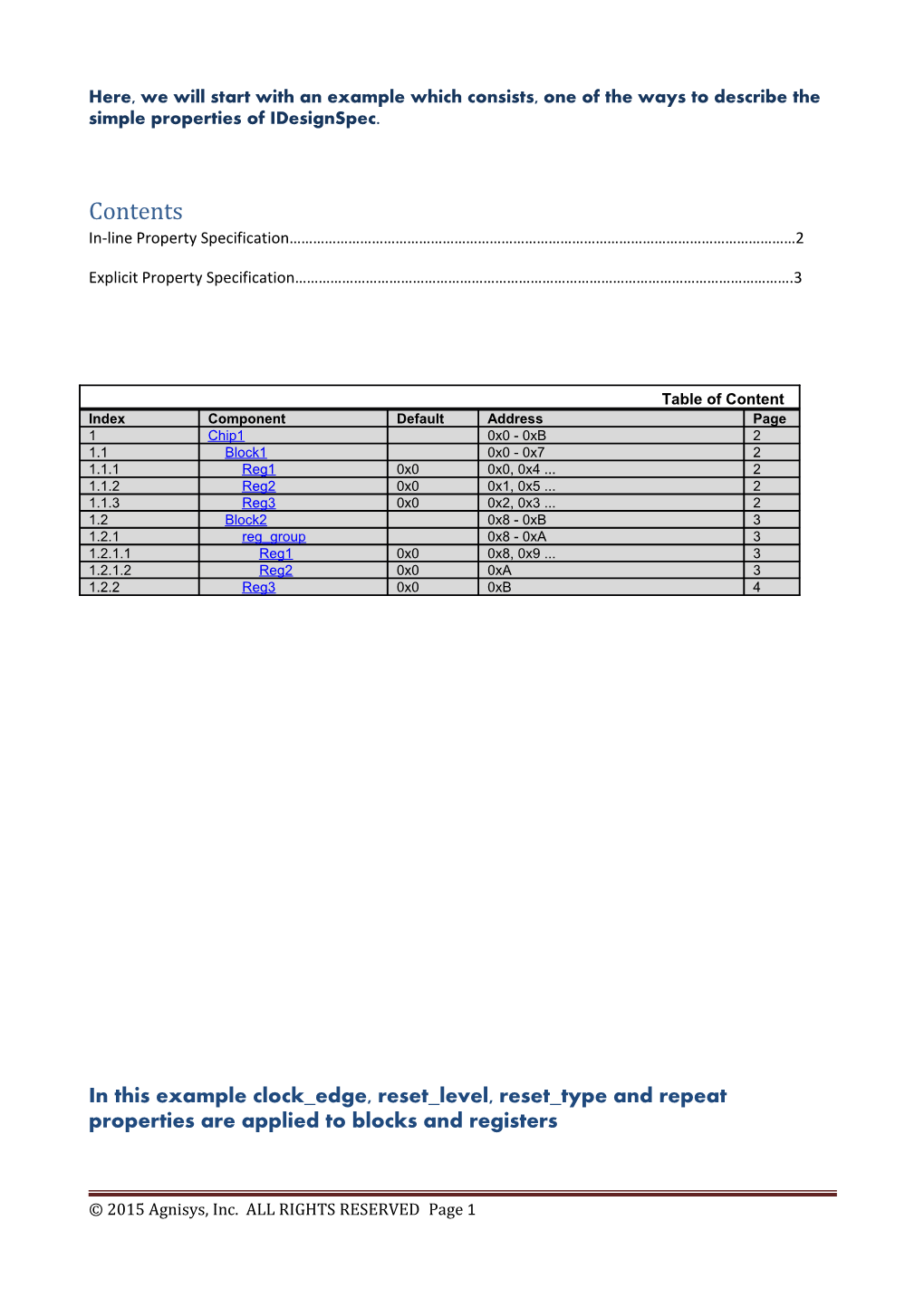

Here, we will start with an example which consists, one of the ways to describe the simple properties of IDesignSpec.

Contents In-line Property Specification…………………………………………………………………………………………………………………2

Explicit Property Specification……………………………………………………………………………………………………………….3

Table of Content TableIndex of ContentComponent Default Address Page 1 Chip1 0x0 - 0xB 2 1.1 Block1 0x0 - 0x7 2 1.1.1 Reg1 0x0 0x0, 0x4 ... 2 1.1.2 Reg2 0x0 0x1, 0x5 ... 2 1.1.3 Reg3 0x0 0x2, 0x3 ... 2 1.2 Block2 0x8 - 0xB 3 1.2.1 reg_group 0x8 - 0xA 3 1.2.1.1 Reg1 0x0 0x8, 0x9 ... 3 1.2.1.2 Reg2 0x0 0xA 3 1.2.2 Reg3 0x0 0xB 4

In this example clock_edge, reset_level, reset_type and repeat properties are applied to blocks and registers

© 2015 Agnisys, Inc. ALL RIGHTS RESERVED Page 1 1 Chip1 Chip1 0x0

offset external size oid=32c83938-a34d-4704-9935-70f88c5aa442

In-line Property specification

Properties specified in description column of each template within curly braces. Multiple properties are semicolon (;) separated

1.1 Block1 Block1 0x0, 0x4...

offset external size {clock_edge=posedge;oid=7259ed2e-bf20-414f-b2ac-607ce51515bf reset_type=async;repeat=2}

1.1.1 Reg1 Reg1 0x0, 0x4...

offset external size 32 default 0x0 {clock_edge=negedge;reset_type=sync}oid=e2150ca2-9e54-43b3-821c-7bf7365bec99 Bits name s/w h/w default description 31:0 Fld1 ro rw 0

1.1.2 Reg2 Reg2 0x1, 0x5...

offset external size 32 default 0x0 {reset_level=high}oid=c1cac1cc-5863-485a-818e-55a9ab052c23 Bits name s/w h/w default description 31:0 Fld1 rw rw 0

1.1.3 Reg3 Reg3 0x2, 0x3...

offset external size 32 default 0x0 {repeat=2}oid=e5147c0c-9bb3-47b9-80b9-7373110b977c bits name s/w h/w default description 31:0 fld ro rw 0

Explicitly Property Specification

© 2015 Agnisys, Inc. ALL RIGHTS RESERVED Page 2 Properties specified by adding columns in already existing row, and a third property row which can be added only below the second row of each IDS template.(Light Red background) Note: Number of columns in each row should be even

1.2 Block2 Block2 0x8

offset external size Clock_edge posedge Reset_level high Reset_type async oid=9699f37b-a2b1-4023-b062-3fdbc719f6c3

1.2.1 reg_group reg_group 0x8

offset external size repeat oid=0143c4f6-35b9-4098-8aac-7230d6e06e28

1.2.1.1 Reg1 Reg1 0x8, 0x9...

offset external size 32 default 0x0 repeat 2 oid=d5aca531-ce24-4ba4-b1d7-e51c6c4f6006 Bits name s/w h/w default description 31:0 Fld1 ro rw 0

Dividing the field’s description column intomultiple columns.

1.2.1.2 Reg2 Reg2 0xa

offset external size 32 default 0x0 Reset_type sync oid=ec631ff7-4dd3-4b5a-98c9-83e4708ba97e bits name s/w h/w default description registered rtl.hw_w1p 31:24 Fld1 ro rw 0 0 23:16 Fld2 r/w1c rw 0 false 1 15:8 Fld3 rw wo 0 1 7:0 Fld4 Rw rw 0 false 0

End RegGroup

1.2.2 Reg3 Reg3 0xb

© 2015 Agnisys, Inc. ALL RIGHTS RESERVED Page 3 offset external size 32 default 0x0 Clock_edge posedge Reset_level low oid=9f186e45-f3d2-4a74-bec1-5d6c34ddd39b bits name s/w h/w default description 31:0 Fld ro rw 0

© 2015 Agnisys, Inc. ALL RIGHTS RESERVED Page 4