2007 IC/CAD Contest

Problem A3:

Pattern Generation for Logic BIST

Source:SoC Technology Center/Industrial Technology Research Institute 1. Introduction:

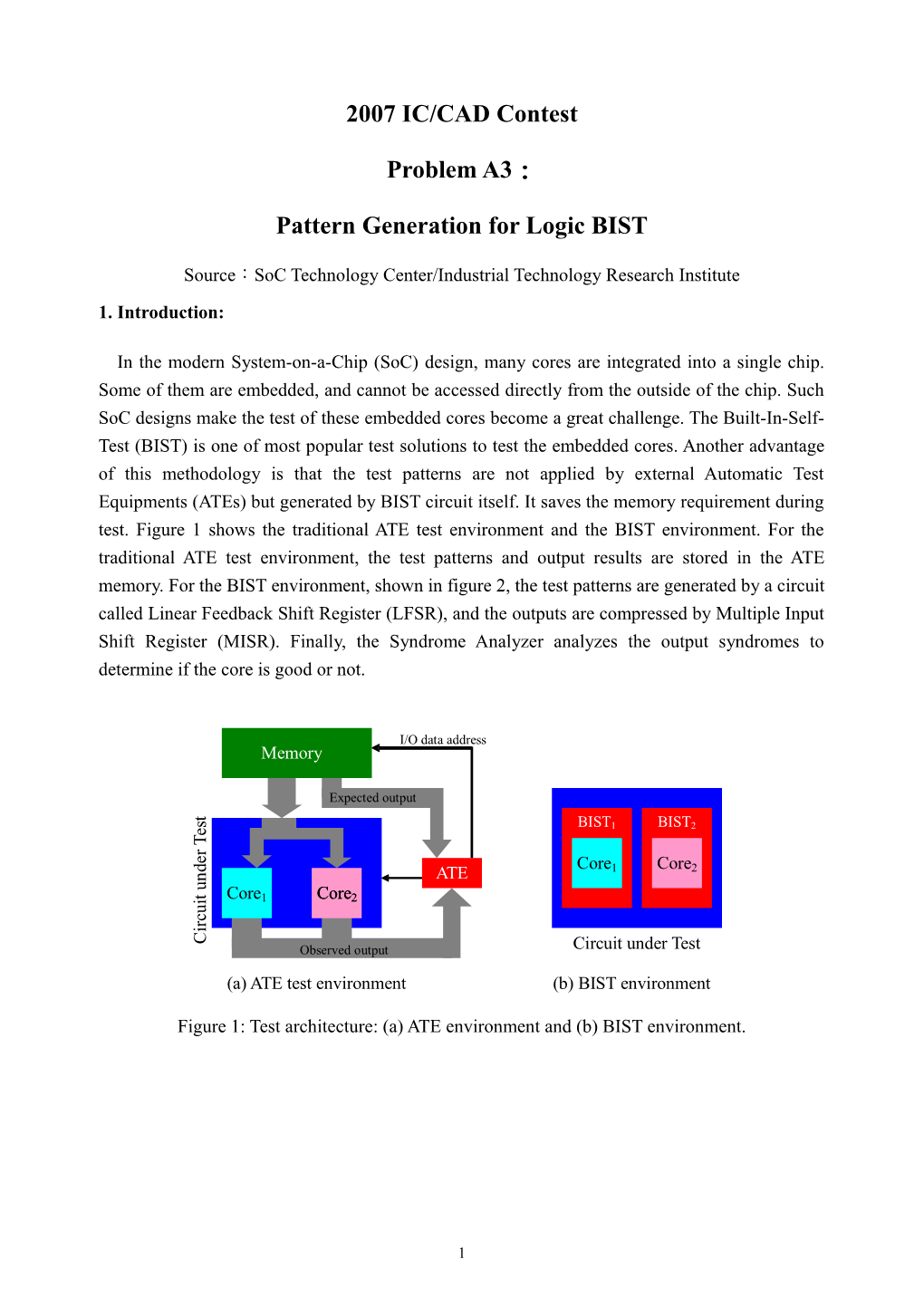

In the modern System-on-a-Chip (SoC) design, many cores are integrated into a single chip. Some of them are embedded, and cannot be accessed directly from the outside of the chip. Such SoC designs make the test of these embedded cores become a great challenge. The Built-In-Self- Test (BIST) is one of most popular test solutions to test the embedded cores. Another advantage of this methodology is that the test patterns are not applied by external Automatic Test Equipments (ATEs) but generated by BIST circuit itself. It saves the memory requirement during test. Figure 1 shows the traditional ATE test environment and the BIST environment. For the traditional ATE test environment, the test patterns and output results are stored in the ATE memory. For the BIST environment, shown in figure 2, the test patterns are generated by a circuit called Linear Feedback Shift Register (LFSR), and the outputs are compressed by Multiple Input Shift Register (MISR). Finally, the Syndrome Analyzer analyzes the output syndromes to determine if the core is good or not.

I/O data address Memory

Expected output

t

s BIST1 BIST2 e T

r e

d Core1 Core2

n ATE u

t Core1 Core2 i u c r i C Observed output Circuit under Test (a) ATE test environment (b) BIST environment

Figure 1: Test architecture: (a) ATE environment and (b) BIST environment.

1

LFSR

BIST Core Controller under Test

MISR

Syndrome Analyzer

Test Result Figure 2: BIST Architecture

The structures of LFSR are easily implemented. They are composed of D-FFs and exclusive- OR gates. Each structure can be expressed by a polynomial of X. In figure 3, we show the 4 3 division type LFSR with polynomial X + X + 1:

Coefficient 1 1 0 0 1 Exponent X4 X3 X2 X1 1

D-FF D-FF D-FF D-FF I0

O4 O3 O2 O1 4 3 Figure 3: The division type LFSR with polynomial X + X + 1

It is easy to figure out that the radix-N polynomial requires N D-FFs. The coefficient of each exponent denotes the insertion points of exclusive-OR gates in the shifting path. When the LFSR starts, the LFSR is reset to zero first. Then the seed value is applied sequentially from I 0. As the

LFSR is operating in test pattern generation mode, the I0 is set to 0.

Different structures of LFSR will generate different sequence of test pattern. It means that if the BIST time is limited, the structure of LFSR will affect the BIST time and Fault Coverage (F.C.) of Core Under Test (CUT).

2. LFSR Design Issue and Partition

It is not practical to implement a big LFSR to test a circuit with large number of inputs. It is because such implementation often results in lower F.C. and longer BIST time. A good partition of LFSR will improve F.C. and BIST time. Figure 4 shows a CUT with k-bit inputs (Ik, Ik-1, …,

I1). The LFSR is partitioned into m smaller LFSRs (LFSRm, LFSRm-1, …, LFSR1). Each LFSR is

2 with a size of Lm, Lm-1, …, L1, respectively.

Lm-bit L1-bit LFSRm LFSR1

k bits

Core Under

Test

Figure 4: LFSR partition

Assume that there are n test vectors (V1, V2, …, Vn) in the test set. If you cannot find any correlation (equivalent or inversion, i.e., Ii = Ij or Ii = Ij’) between inputs of test patterns, the optimal size of LFSR is Lm+Lm-1+…+ L1 = k. However, the correlations between inputs are possible in the test set. Hence, there are two cost considerations in test application:

2.1 The hardware cost:

You can use both of the bit broadcast and bit inversion techniques to reduce the required length of LFSRs if the correlations, Ii=Ij or Ii=Ij’, exist between inputs of test pattern. The total length of LFSRs, Lm+Lm-1+…+ L1 = Ltotal, will smaller than k. In the figure 5, the input length k is

10. The test set is composed of 18 test vectors (V1, V2, …, V10) . The minus sign denotes “don’t care”. The patterns are listed in descending order from I10 to I1. In the test set, the I8 and I5 in every test vector are equivalent or compatible. The I7 and I3 in every test vector are inversion or compatible. You can combine I8 and I5 into a single bit and combine I7 and I3 with adding an inverter to save 2 D-FFs of LFSRs.

3 Input I I I I I I I I I I Vector 10 9 8 7 6 5 4 3 2 1 Figure 5: Example of a test set V1 1 - 0 1 1 0 1 0 0 0 V 0 0 0 - 1 0 1 1 1 1 2 2.2 The test time V3 0 - - 0 0 - 0 1 0 - cost V4 - 0 0 - - - 1 0 1 0 V - 1 - 0 - 1 - 1 0 1 5 In some cases, if V - 0 - 1 1 - 1 0 0 1 6 we use all bits of V7 0 1 - 0 - 1 1 1 - 1 LFSRs to be test V8 - 0 - 1 - - 0 0 1 1 inputs, it will V9 - 0 1 - 1 - 1 1 1 1 expense more test V10 1 1 1 0 1 1 0 1 1 0

V11 0 1 - 0 0 0 1 1 1 1 time for the

V12 0 - - - 1 0 0 1 1 0 purpose of high

V13 1 0 0 0 - - 1 1 0 - Pattern Coverage

V14 - 1 1 - - - 0 1 1 0 (= Hit Patterns /

V15 0 - 1 0 - - 0 - 0 1 Total Test V16 0 1 - - - 1 0 0 - 1 Patterns). One of V17 0 - 1 1 0 1 0 - - 1 the solutions is to V18 1 0 0 1 1 0 0 0 1 1 appropriately increase the size of LFSRs and use some of them to be test inputs. In such condition, Ltotal will larger than k.

3. Subject of this problem:

Please write a program which can generate appropriate structures of LFSRs for the applied test set. The program must consider three factors: (1) the hardware test cost, (2) pattern coverage, and (3) BIST time. The pattern coverage should be larger than 90%, and the seed of each LFSR must be a fixed value when the BIST mode starts. The input file to the program is the description of test set. Its format will be described in detail in the Input Format section. You must generate two output files to describe the structures of LFSRs, and output report. The required formats are listed in the Output Format section. There is an example for the test set in figure 5, and it is shown in the Example section.

4. Input Format

The input file contains three keywords: INPUT_NO, VECTOR_NO, and VECTORS, which represent the number of input, the number of test vector, and the test vectors, respectively. In figure 5, the number of input is 10 and the number of test vector is 18. The input file is written as follows:

INPUT_NO 10

4 VECTOR_NO 18 VECTORS

1-01101000 // V1

000-101111 // V2 ….

1001100011 // V18

5. Output Format

There are two output files. The first one is the structure output file, and the other is the output report.

5.1 Structure Output

The output structure file contains five keywords: TOTAL_SIZE, LFSR_NO, POLY_n, SEED_n, and INPUT_SEQ, which represent: total size of LFSR, the number of LFSR, polynomial of LFSR_n, seed of LFSR_n, and input order, respectively. The LFSR_SIZE is the number of D-FFs used in test pattern generation. The LFSR_NO is the partition number of LFSRs. The index n of POLY and SEED present the identification number of each LFSR. The index’s range is from m (the LFSR_NO) to 1. The polynomial presentation is the list of 4 3 exponent item whose coefficient is 1. For example, the X + X + 1 is presented as 4 3 0. The numbers are separated by blank or tab keys, and are listed in a descending order. The seed is 4 3 listed in binary. For example, if the reset state of X + X + 1 is {0 0 1 0} in your design, denote it as 0010 without any space between digits. The LFSRs’ output IDs, which are not listed in the output file but used for INPUT_SEQ, are default set from TOTAL_SIZE to 1. The INPUT_SEQ specifies the connection from LFSRs’ outputs to CUT’s inputs. For example, a 3- 4 3 3 2 3 LFSR structure with X + X + 1, X + X + 1 and X + X + 1 forms a 10-bit test pattern generator. 8 of them are used as inputs of CUT. The output structure file is shown as follows, and the connection between LFSRs and CUT is shown in figure 6. In INPUT_SEQ, the 9,7 means that the O9 connects to both I9 and I7, the -3 means that O5 connects to I3 with an inversion, and two 0s mean that O4 and O2 are floating.

TOTAL_SIZE 10 LFSR_NO 3 POLY_3 4 3 0 SEED_3 0011 POLY_2 3 2 0 SEED_2 001 POLY_1 3 1 0 SEED_1 010 INPUT_SEQ 10 9,7 6 5 4,-1 -3 0 2 0 8

5 POLY_3 POLY_2 POLY_1

O10 O9 O8 O7 O6 O5 O4 O3 O2 O1

I10 I9 I8 I7 I6 I5 I4 I3 I2 I1

CUT

Figure 6: Example of an output structure file.

5.2 Output Report

The output report file must contain the required BIST clock cycles (including the initial reset period) and the pattern coverage for your LFSR design. Other information can be also recorded in this file. The format is free without any constraints.

6. Example

We can use exhaustive methods to search the best solution for the example in figure 5, but it is time consuming when the test data is enormous. If we use single LFSR as the pattern generation circuit, the polynomial of the best solution is X8 + X6 + X3+ X2 + 1. The BIST time is 42 clock cycles when the initial seed is 10001101 and INPUT_SEQ is 8,5 10 4 2 9 7,-3 6 1.The pattern coverage is 100%, i.e. total 18 vectors are hit during 42 clock cycles. If we unfortunately select another non-optimized polynomial, X8 + X5 + X4 + X + 1, it takes 28 clock cycles to hit 17 vectors when its initial seed is 01010111 and INPUT_SEQ is 8,5 10 4 2 9 7,-3 6 1. Its pattern coverage is 94.4% (= 17/18). The following table lists four LFSR structures and their results.

Table 1. Possible solutions for the test set in figure 5

BIST Time Hit Pattern LFSR Structure seeds INPUT_SEQ (clocks) Patterns Coverage (%) X8 + X6 + X3 + X2 + 1 42 10001101 8,5 10 4 2 9 7,-3 6 1 18 100.00% X8 + X6 + X5 + X + 1 28 01010111 8,5 10 4 2 9 6 7,-3 1 17 94.40% X3 + X2 + 1, X5 + X2 + 1 32 100, 00111 6 1 8,5 9 10 7,-3 2 4 17 94.40% X3 + X + 1, X5 + X4 + X3 + X + 1 42 010, 11001 2 4 9 7,-3 6 1 8,5 10 18 100.00%

If we choose the last one to be our final solution, the output structure file is list as follows:

6 TOTAL_SIZE 8 LFSR_NO 2 POLY_2 3 1 0 SEED_2 010 POLY_1 5 4 3 1 0 SEED_1 11001 INPUT_SEQ 2 4 9 7,-3 6 1 8,5 10

The output report is format-free, but it must contain two necessary results: the total required BIST clock cycles and the pattern coverage. The following is an example: cycle 1: LFSR=010 11001, LFSR out=10011100 Applied pattern=1001101000, Hit pattern V1 cycle 6: LFSR=101 01010, LFSR out=01101010 Applied pattern=0110110110, Hit pattern V14 cycle 9: LFSR=100 11101, LFSR out=10011011 Applied pattern=1001100011, Hit pattern V8 V18 cycle 12: LFSR=111 00100, LFSR out=01000111 Applied pattern=0100001111, Hit pattern V11 cycle 13: LFSR=10101000, LFSR out=01001010 Applied pattern=0100100110, Hit pattern V12 cycle 18: LFSR=110 01111, LFSR out=10101111 Applied pattern=1010111111, Hit pattern V9 cycle 21: LFSR=001 01110, LFSR out=01101001 Applied pattern=0110110101, Hit pattern V5 V15 cycle 24: LFSR=011 00110, LFSR out=01100101 Applied pattern=0110011101, Hit pattern V7 cycle 25: LFSR=110 01100, LFSR out=00001111 Applied pattern=0000101111, Hit pattern V2 cycle 27: LFSR=101 01011, LFSR out=11101010 Applied pattern=1110110110, Hit pattern V10 cycle 28: LFSR=001 10110, LFSR out=01110001

7 Applied pattern=0111010001, Hit pattern V16 V17 cycle 32: LFSR=110 11001, LFSR out=10011110 Applied pattern=1001101010, Hit pattern V4 cycle 36: LFSR=010 00101, LFSR out=10000101 Applied pattern=1000001101, Hit pattern V13 cycle 42: LFSR= 001 00010, LFSR out=01100000 Applied pattern=0110010100, Hit pattern V3 Required BIST clock cycles: 42 Pattern Coverage: 100.00%

7. Language & Platform: 1. Language: C or C++ 2. Platform: Linux

8. Grade criterion: 1. Pattern coverage rate 2. BIST time (the number of required BIST clock cycles) 3. Total LFSR size 4. Performance (Run time, Memory usage)

8 Appendix

Division type LFSR with polynomial: X3 + X2 + 1

D-FF D-FF D-FF 0

Cyclic pattern sequence:

1 1 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 1 1 0 1 0 1 1 0 1 1 1 1 0 1 1 0 1 0 1 1 0 0 0 0 0 1 1 0 0 1 1 0 1 0 0 1

9