Lesson 25 ENCODER Design

An encoder accepts an active level on one of its inputs, representing digit, such as a decimal or octal digits, and converts it to a coded output such as BCD or binary. Encoders can also be devised to encode various symbols and alphabetic characters.

The process of converting from familiar symbols or numbers to a coded format is called encoding.

An encoder has a number of input lines, only one of which input is activated at a given time and produces an N-bit output code, depending on which input is activated.

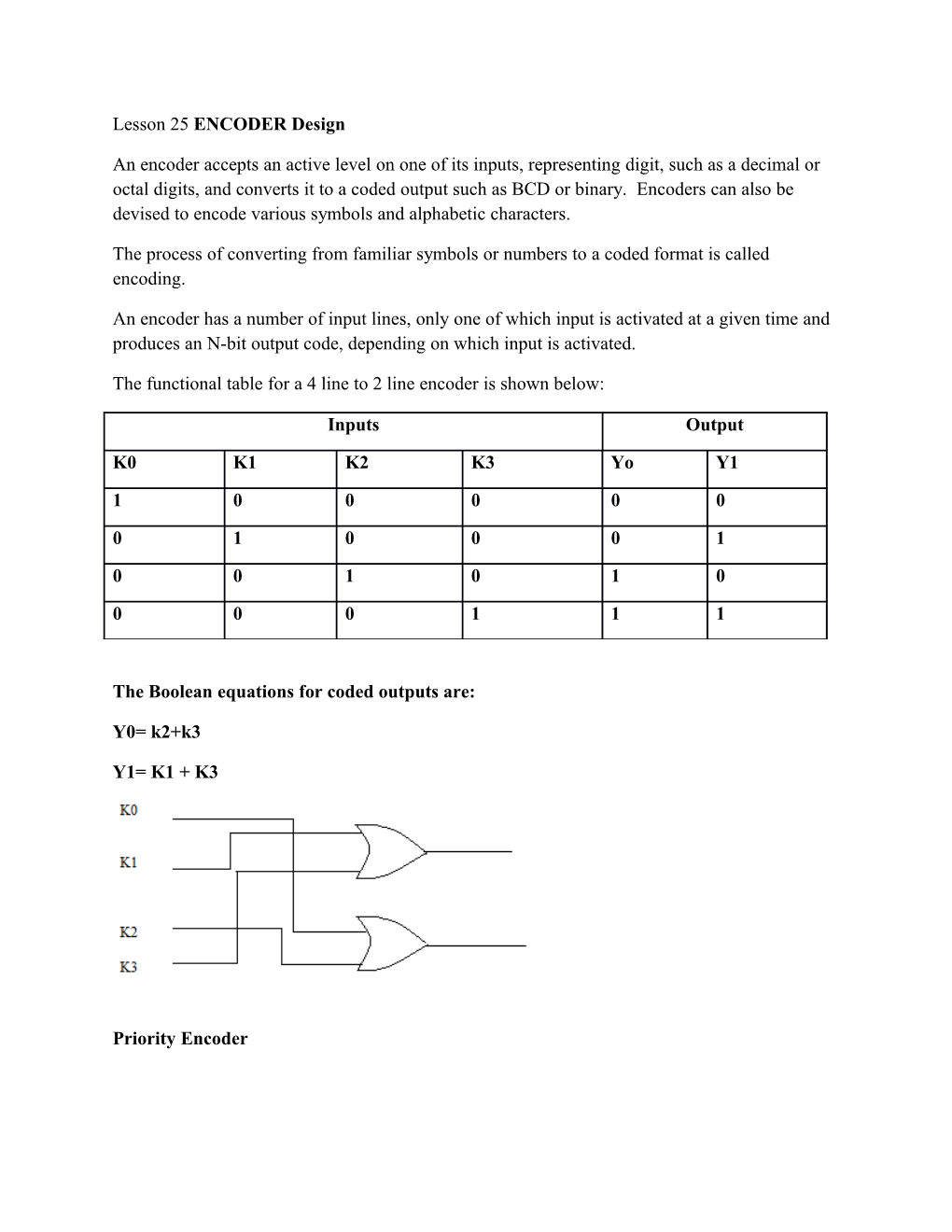

The functional table for a 4 line to 2 line encoder is shown below:

Inputs Output

K0 K1 K2 K3 Yo Y1

1 0 0 0 0 0

0 1 0 0 0 1

0 0 1 0 1 0

0 0 0 1 1 1

The Boolean equations for coded outputs are:

Y0= k2+k3

Y1= K1 + K3

Priority Encoder A priority Encoder encodes one of the many inputs but only the key having the highest priority is encoded first. If highest priority key is not pressed then the next lower priority key is encoded and so on.

The functional table is given below, In the table Y0Y1 are the encoded output, output V is an indicator of a valid key press and is high when one of the valid key is pressed:

K0 K1 K2 K3 Y0 Y1 V 0 0 0 0 x x 0 1 0 0 0 0 0 1 x 1 0 0 0 1 1 x x 1 0 1 0 1 x x x 1 1 1 1

The first row in table shows none of the key pressed , so the output (Y0, Y1) are don’t care, and V output is zero indicating none of the valid key pressed.

The other rows shows only one input is active and the least numbered keys are don’t cared, and a valid key press entry V is raised and corresponding binary output obtained at Y1, Y1.

The Boolean equations are:

The equation for V is: V = K0 + K1 + K2 + K3

The logic diagram for the 4 to 2 priority encoder is shown in figure below:

VHDL Code for 4:2 priority encoder

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity PRIORITY_ENCODER is

Port ( K : in STD_LOGIC_VECTOR (3 downto 0);

Y : out STD_LOGIC_VECTOR (1 downto 0);

V : out STD_LOGIC); end PRIORITY_ENCODER;

architecture Behavioral of PRIORITY_ENCODER is begin

Y(0) <= K(2) OR K(3);

Y(1) <= (K(3) OR (K(1) AND (not K(2))));

V <= K(0) OR K(1) OR K(2) OR K(3); end Behavioral;

Simulation:

Structural Modelling of 4:2 Priority Encoder entity or_4ip is

Port ( i : in STD_LOGIC_VECTOR (3 downto 0);

o : out STD_LOGIC); end or_4ip; architecture Behavioral of or_4ip is begin o <= i(0) or i(1) or i(2) or i(3); end Behavioral;

------entity OR_GATE is

Port ( i1 : in STD_LOGIC;

i2 : in STD_LOGIC;

o : out STD_LOGIC); end OR_GATE; architecture Behavioral of OR_GATE is begin

o <= i1 or i2; end Behavioral;

------entity NO_GATE is

Port ( i : in STD_LOGIC;

o : out STD_LOGIC); end NO_GATE; architecture Behavioral of NO_GATE is begin

o <= not i; end Behavioral;

------library IEEE; use IEEE.STD_LOGIC_1164.ALL; library my_logics_lib; use my_logics_lib.all; entity encoder_structure is

Port ( k : in STD_LOGIC_VECTOR (3 downto 0);

o : out STD_LOGIC_VECTOR (1 downto 0);

v : out STD_LOGIC); end encoder_structure; architecture Behavioral of encoder_structure is signal w1, w2: std_logic; begin x1: entity work.or_gate port map

(i1=> k(3), i2 => w1, o => o(1)); x2: entity work.NO_gate port map

(i=> k(2), o => w2); x3: entity work.and_gate port map

(i1=> k(1), i2 => w2, o => w1); x4: entity work.or_gate port map

(i1=> k(2), i2 => k(3), o => o(0)) ; x5: entity work.or_4ip port map

(i(0)=> k(0), i(1)=> k(1), i(2) => k(2), i(3) => k(3), o => v); end Behavioral;

------

Design Decoder and Encoder (octal to binary, decimal to BCD) Design 8-bit Priority Encoder