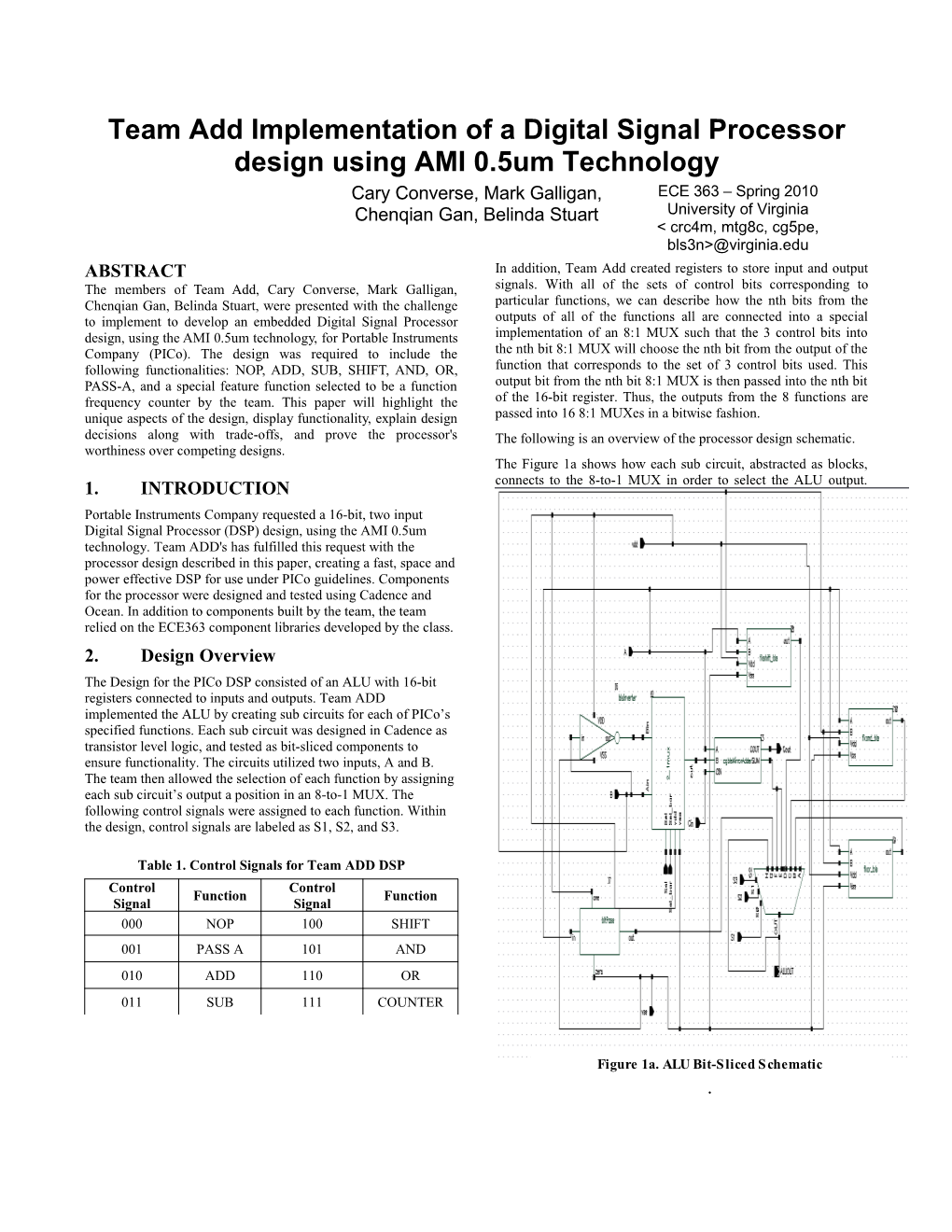

Team Add Implementation of a Digital Signal Processor design using AMI 0.5um Technology Cary Converse, Mark Galligan, ECE 363 – Spring 2010 Chenqian Gan, Belinda Stuart University of Virginia < crc4m, mtg8c, cg5pe, bls3n>@virginia.edu ABSTRACT In addition, Team Add created registers to store input and output The members of Team Add, Cary Converse, Mark Galligan, signals. With all of the sets of control bits corresponding to Chenqian Gan, Belinda Stuart, were presented with the challenge particular functions, we can describe how the nth bits from the to implement to develop an embedded Digital Signal Processor outputs of all of the functions all are connected into a special design, using the AMI 0.5um technology, for Portable Instruments implementation of an 8:1 MUX such that the 3 control bits into Company (PICo). The design was required to include the the nth bit 8:1 MUX will choose the nth bit from the output of the following functionalities: NOP, ADD, SUB, SHIFT, AND, OR, function that corresponds to the set of 3 control bits used. This PASS-A, and a special feature function selected to be a function output bit from the nth bit 8:1 MUX is then passed into the nth bit frequency counter by the team. This paper will highlight the of the 16-bit register. Thus, the outputs from the 8 functions are unique aspects of the design, display functionality, explain design passed into 16 8:1 MUXes in a bitwise fashion. decisions along with trade-offs, and prove the processor's The following is an overview of the processor design schematic. worthiness over competing designs. The Figure 1a shows how each sub circuit, abstracted as blocks, 1. INTRODUCTION connects to the 8-to-1 MUX in order to select the ALU output. Portable Instruments Company requested a 16-bit, two input Digital Signal Processor (DSP) design, using the AMI 0.5um technology. Team ADD's has fulfilled this request with the processor design described in this paper, creating a fast, space and power effective DSP for use under PICo guidelines. Components for the processor were designed and tested using Cadence and Ocean. In addition to components built by the team, the team relied on the ECE363 component libraries developed by the class. 2. Design Overview The Design for the PICo DSP consisted of an ALU with 16-bit registers connected to inputs and outputs. Team ADD implemented the ALU by creating sub circuits for each of PICo’s specified functions. Each sub circuit was designed in Cadence as transistor level logic, and tested as bit-sliced components to ensure functionality. The circuits utilized two inputs, A and B. The team then allowed the selection of each function by assigning each sub circuit’s output a position in an 8-to-1 MUX. The following control signals were assigned to each function. Within the design, control signals are labeled as S1, S2, and S3.

Table 1. Control Signals for Team ADD DSP Control Control Function Function Signal Signal 000 NOP 100 SHIFT 001 PASS A 101 AND 010 ADD 110 OR 011 SUB 111 COUNTER

Figure 1a. ALU Bit-Sliced Schematic . Figure 5.The output shows a bit-sliced A AND B

Figure 1b. Bit Sliced DSP Overview 3.4 ADD/SUB . Figure 1b shows the high level bit sliced view of the DSP. Inputs The adder/subtractor performs the functions A+B and A-B, and outputs of the design are stored. in registers. The ALU, depending on the imputed control signals. Space was saved by abstracted as a block, receives a clock signal, inputs A and B, a recycling hardware and using the same circuit for both ADD and carry signal, control signals, and connections for power and SUB. Because both the ADD and SUB are handled by the same ground. After incorporating input and control signals, the ALU circuit, the add/sub sub circuit output was connected to both the outputs a value based on the functionality specified by the control ADD and SUB position on the 8-to-1 MUX to match function bits through ALU out, as well as a carry out signal. The individual OPCODE conventions. ALU components are discussed in greater detail within the Sub Because a mirror adder was utilized for the addition and Circuit section of the paper. subtraction functionalities, bit slicing and cascading would cause additional and unnecessary inverters to be used in the design. 3. Sub Circuits Because of this, extra inverters would have to be used in order to The ALU portion of the DSP was created using an 8-to-1 MUX fully bit-slice the ALU. To improve the design, the ADD/SUB with each sub circuit. Most functions were implemented by was later un bit-sliced. connecting a sub circuit specific for each function to the MUX; however the NOP, ADD, and SUB are an exception. The functionality and specifics of each circuit is detailed within this section. 3.1 NOP The NOP function required that no change occurred at the output of the DSP. This was implemented by sending the output stored in the output register as an input to the NOP’s MUX position.

3.2 PASS A The PASS A required that the output of the DSP be the same as the A input. The PASS-A was implemented using sixteen 1-bit pass gates, which allowed the sixteen input bits of A to pass unaltered through the ALU. Figure 2 details the functionality of the PASS A sub circuit.

3.3 AND Figure 3a. Adder functionality The AND functionality required a bit-wise AND between inputs A and B. . Figure 3b. Adder/Subtractor functionality Figure 6.The output shows a bit-sliced A OR B

3.5 SHIFT . The shift function required that the DSP’s output produce the A 3.7 COUNTER input shifted by the bottom bits of the B input. The following PICo requested an additional function for the DSP, up to the mapping for the bottom B inputs was used to determine the shift discretion of the design team. . The special function we amount: implemented was a counter of source. This functionality allows Table 2. Shift Codes users of the DSP to keep track of how many times each function is called. The 3 least significant bits of the 16-bit input A correspond Bit Code Shift Bit Code Shift to the function to be monitored. 00 1 bit 10 3 bit This functionality was selected for its self-diagnostic benefits, as 01 2 bit 11 4 bit the frequency and type of function used in applications can be self-monitored using existing functionality on the Digital Signal Processor.

4. Innovations When designing the circuit, special considerations were made for space and usability. For this reason, an ADD/SUB was implemented to recycle hardware and save space that would have otherwise been used towards separate circuits for the ADD and SUB functionalities. Because circuits often undergo many tests, the additional functionality of a counter of source was used to aid in circuit diagnostics. The DSP was also bit sliced to improve flexibility of bit width. The tradeoff with this design decision was the increased complexity of buffering when simulating the design.

4.1 ADD/SUB The original PICo design called for both 16-bit addition and Figure 4. Output bits are shifted based on control subtraction functionality. Instead of building separate circuitry for signals S0 and S1 from the B input. each function, space was saved by implementing an adder- subtractor. 3.6 OR Because adders and subtractors use similar circuit structures and . the processor was specified in such a way as to only utilize one The AND functionality required a bit-wise OR between inputs A function at a time, the team chose to implement both and B. functionalities by reusing existing elements. To do this, an additional 2-to-1 MUX and inverter were added to a mirror adder on the B input. On an ADD, the B input remained unchanged; however, on a SUB the B input was inverted. Control signals played a large part in the design decision's success. ADD and SUB were assigned control bits 010 and 011 respectively. By specifying the control signals for add and subtract to be differentiable by one control bit, specifically, the last control bit, the B input could be inverted on a subtract command and a two's The active energy for the devices was 2.24134*10-9 J for when complement subtract could be preformed. VDD=5 V. An average power of 210.95*10-4 watts was found, so over 1700 ns, energy = 2.24134*10-9 J. Another energy value of 2.73063*10-10 J was found for when VDD=2.5 V 5.1.2 Delay The delay of the device was found to be 9.446 ns or 9.44600 *10-9 seconds using VDD=5 V. 5.1.3 Area The area of the device was calculated using the total sum of device widths within the DSP, excluding external buffers. The area of the devices was found to be 20676 um or .020676 meters. The area of each sub circuit is as follows: PASS 384 um, AND 264 um, OR 312 um, Add/Sub 5928 um, Shifter 807 um, A Special configuration of an “8:1” MUX was implemented to 2 2 speed up our adder/subtrator. The ADD/SUB function was Counter 2181 um , MUX 6192 um . The chip is space effective. connected to a 2:1 MUX that fed directly to the output. A 6:1 mux was used for all other functions and the output of the 6:1 MUX 5.1.4 Metric Calculation and the MUX output was an input to the 2:1 MUX. Since the 2:1 The final calculated metric was calculated to be: MUX output was preselected, the critical path delay of the Metric = (3.58615*10-8 J)*(9.44600 ×10-9 s)2 * .020676 m= ADD/SUB could be reduced. 4.13495*10-27 mJs2 4.2 Counter 5.1.5 Arbitrary Function Results The counter used the control code 111. Once the counter is called, The Arbitrary function was calculated separately. The results for the chosen function is counted until the counter is called again the arbitrary function are detailed in this section. using the 111 control code, and the result from the function count is outputted. The least significant bits for each call do not need to 5.1.6 Area correspond to each other. The counter can be used in applications The area of the arbitrary function is 2181 um or .002181 m where functionality usage is not determined by predefined code calls, or other scenarios where the exact frequency of function use is not easily obtainable. 6. Conclusions In conclusion, the Team ADD design provides for a fast, space and power effective DSP. Team ADD’s design meets all design 4.3 Optimization requirements and incorporates a unique additional function that In addition to reusing hardware for the adder and subtractor will be invaluable in chip diagnostics. The design minimizes chip functionalities, components were sized to be as small as possible, area by allowing one circuit to handle both add and subtract with the adder/subtractor circuit as an exception. [1] describes functionalities. The final PICo defined metric value for the chip optimal sizes for a mirror adder. Since the adder/subtractor circuit was 1.1799*10-25, making the Team ADD DSP an attractive was implemented using a mirror adder, the Rabaey sizes were choice for the PICo contract. Because the DSP was constructed used to speed up the carry. using bit-slicing, the design’s bit-width can be easily expanded or reduced, depending on the needs of PICo. Because of this 5. Results flexibility in design and optimal use of space, the Team ADD The PICo metric for DSP optimality was defined as follows: design is ideal for implementation in many different use cases. For this reason, the Team ADD design is the best choice for the Metric = (Active Energy)*Delay^2*Area PICo contract. For metric calculations, the additional function was omitted. The following sections discuss the Active Energy, Delay, and Area of 7. ACKNOWLEDGMENTS Team ADD’s board design. We would like to thank Benton Highsmith Calhoun for essential design knowledge. 5.1 Overall Findings Using the calculated active energy, delay, and area, the metric 8. REFERENCES outlined by PICo can be calculated. [1] ECE 363 Sub Circuit Library 5.1.1 Active Energy [2] Rabaey, J. Digital Integrated Circuits: A Design Perspective. Active energy is measured as the average energy of the design Prentice Hall, 2003 over 8 cycles, using a 10MHz clock, control counts from 000 to [3] Lamport, L. LaTeX User’s Guide and Document Reference 111, Input A: alternating between 0xAAAA and 0x5555, and Manual. Addison-Wesley, Reading, MA, 1986 Input B equal to 0xAA55