Assignment #5

1. Design a 3 input CMOS static NAND gate for: a) minimum area; b) minimum propagation delay; c) equal rise and fall time; d) determine the worst case rise and fall time if the NAND gate is driving a 0.1 pf load.

2. Design a gate to implement the function F(A,B,C,D) = (AB + CD)’ in Pseudo NMOS. Analyze the circuit for valid operation at logic high and logic

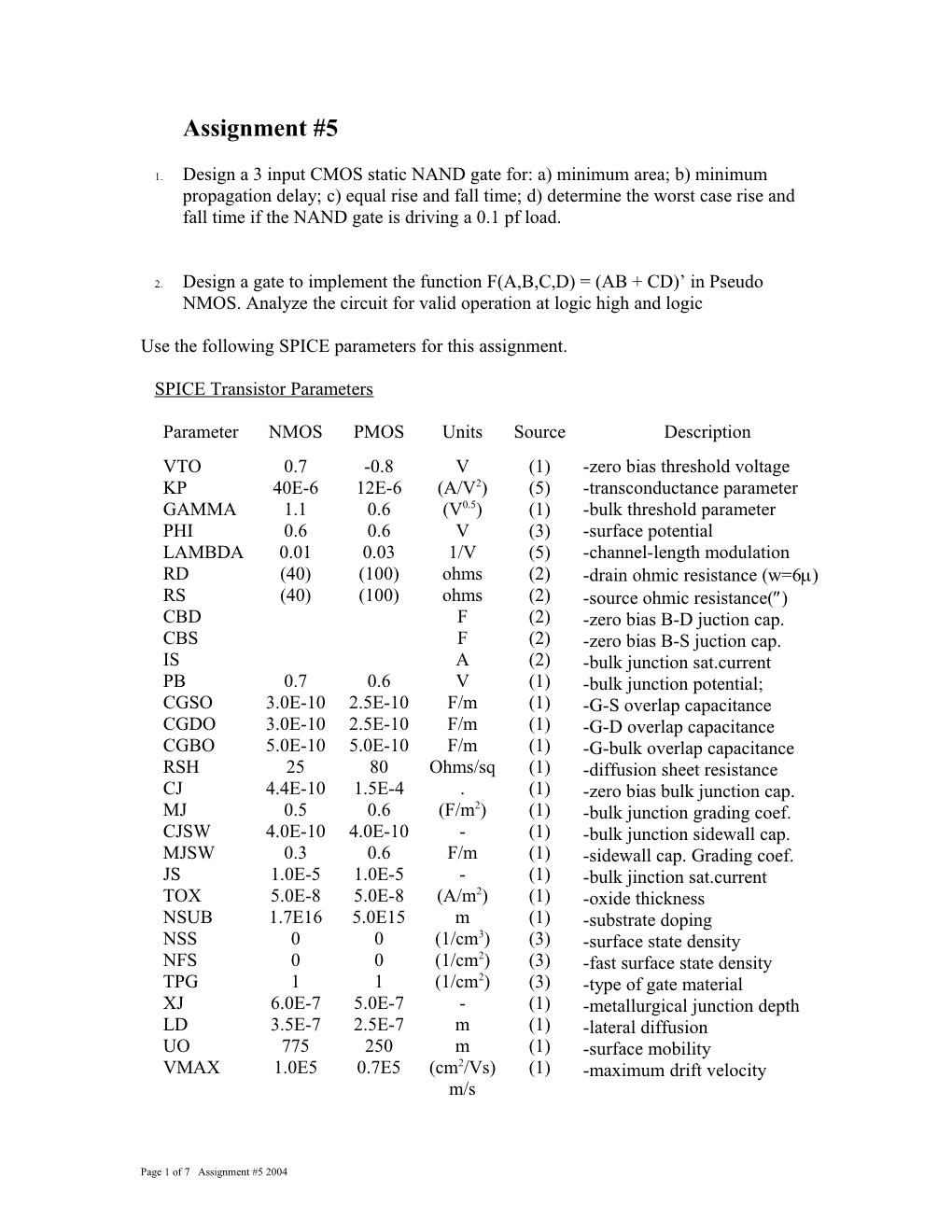

Use the following SPICE parameters for this assignment.

SPICE Transistor Parameters

Parameter NMOS PMOS Units Source Description VTO 0.7 -0.8 V (1) -zero bias threshold voltage KP 40E-6 12E-6 (A/V2) (5) -transconductance parameter GAMMA 1.1 0.6 (V0.5) (1) -bulk threshold parameter PHI 0.6 0.6 V (3) -surface potential LAMBDA 0.01 0.03 1/V (5) -channel-length modulation RD (40) (100) ohms (2) -drain ohmic resistance (w=6) RS (40) (100) ohms (2) -source ohmic resistance() CBD F (2) -zero bias B-D juction cap. CBS F (2) -zero bias B-S juction cap. IS A (2) -bulk junction sat.current PB 0.7 0.6 V (1) -bulk junction potential; CGSO 3.0E-10 2.5E-10 F/m (1) -G-S overlap capacitance CGDO 3.0E-10 2.5E-10 F/m (1) -G-D overlap capacitance CGBO 5.0E-10 5.0E-10 F/m (1) -G-bulk overlap capacitance RSH 25 80 Ohms/sq (1) -diffusion sheet resistance CJ 4.4E-10 1.5E-4 . (1) -zero bias bulk junction cap. MJ 0.5 0.6 (F/m2) (1) -bulk junction grading coef. CJSW 4.0E-10 4.0E-10 - (1) -bulk junction sidewall cap. MJSW 0.3 0.6 F/m (1) -sidewall cap. Grading coef. JS 1.0E-5 1.0E-5 - (1) -bulk jinction sat.current TOX 5.0E-8 5.0E-8 (A/m2) (1) -oxide thickness NSUB 1.7E16 5.0E15 m (1) -substrate doping NSS 0 0 (1/cm3) (3) -surface state density NFS 0 0 (1/cm2) (3) -fast surface state density TPG 1 1 (1/cm2) (3) -type of gate material XJ 6.0E-7 5.0E-7 - (1) -metallurgical junction depth LD 3.5E-7 2.5E-7 m (1) -lateral diffusion UO 775 250 m (1) -surface mobility VMAX 1.0E5 0.7E5 (cm2/Vs) (1) -maximum drift velocity m/s

Page 1 of 7 Assignment #5 2004 SPICE Level 3 Parameters

Parameter NMOS PMOS Units Source Description THETA 0.11 0.13 1/V (1) -mobility modulation KAPPA 1.0 1.0 - (1) -saturation field factor ETA 0.05 0.3 - (1) -static feedback

Page 2 of 4

Other Electrical Parameters

Capacitance Edge Component Source (pF/m2) (pF/m) Gate (Cox) 6.9E-4 0.5E-4 (1) Metal1 – Field 2.7E-5 0.4E-4 (1) Metal1 – Poly 5.0E-5 (1) Metal1 – Diffusion 5.0E-5 (1) Poly – Field 6.0E-5 0.2E-4 (1) Metal2 – Field 1.4E-5 2.0E-5 (4) Metal2 – Diffusion 1.6E-5 (4) Metal2 – Poly 2.0E-5 (4) Metal2 – Metal1 2.5E-5 (4) Capacitor P + - Poly 6.9E-4 0.5E-4 (*) (0.1%/V linearity) (1)

Resistance (ohms/sq.) Source

N+ Diffusion 25 (1) P+ Diffusion 80 (1) N+ Poly 18 (5) Capacitor P+ 300 (1) P-well 4K (1) Metal1 0.035 (4) Metal2 0.030 (4) 3 3 metal1 – P + Diffusion Contact 121 (5) 3 3 metal1 – N + Diffusion Contact 44 (5) 3 3 metal1 – N + Poly Contact 25 (5)

Maximum operating voltage: 5 volts.

Sources: (1) D. Smith of NTE, presented at CMC Workshop June 6-7, 1985.

Page 2 of 7 Assignment #5 2004 Answer Q1

3 input CMOS NAND

a) minimum area Wp = Wn = 3m

Lp = Ln = 3m Vdd WnA = WnB =WnC = WpA= WpB =WpC = 3m

LnA = LnB =LnC = LpA= LpB =LpC = 3m A B C

OUT

A

B

C

Vdd b) minimum propagation delay

Wp = n/p Wn = 1.7Wn 5.1 m Equivalent inverter

WnA = WnB =WnC = (3)(3) = 9 3 m

WpA= WpB =WpC = 5.1m

All lengths = 3 m Vdd c) equal rise and fall times 9 m p = n Wp = 3Wn

equivalent inverter 3 m WnA = WnB =WnC = (3)(3) = 9

WpA= WpB =WpC = 9m

All lengths = 3 m

Page 3 of 7 Assignment #5 2004 d) Worst case rise time

Vdd

A B C

OUT

A Charging 0.1pF B

C

The worst case rise time will be when only one input is low and the other two are high. ( one PMOS “ON” and top two NMOS “ON ‘a and B’).

tr = 2.2 charge

charge = Rp (3 CdPMOS + 3 CdNMOS + 2CsNMOS + CL) Assume all transistors are minimum size and that

CdPMOS + CdNMOS + CsNMOS = C

trworst = 2.2 Rp [8C +CL]

’ Rp = 1/p(Vgs -Vt) = 1/[Kp Wp/Lp(Vgs -Vt) ] = 1/Kp’(4.2) -6 Rp = 1/(12 10 )(4.2) = 19.8 k

Cd = CjAD + CjSWPD + CGSO W

Assume a drain capacitance of 40fF -15 -12 trworst = (2.2)(19.8k)[840x10 + 0.1 10 ] trworst = 18.3 ns

Page 4 of 7 Assignment #5 2004 Worst case fall time Vdd

A B C

OUT

A 0.1pF

B

C

Assume minimum size transistors Wn = Ln = 3m tf = 2.2 discharge

discharge = (3Rn)(3CdPMOS + 3CdNMOS +2CsNMOS +CL]

Again assume CdPMOS + CdNMOS + CsNMOS = C discharge = 3Rn (8C +CL) -6 Rn = 1/n(Vgs –Vt) = 1/4010 (4.3) = 5.8 k Assume C = 40fF -15 -12 tf = (2.2)(3)(5.8k)(84010 + 0.1 10 ) tf = 16.1 ns

Page 5 of 7 Assignment #5 2004 Question 2 Vdd = 5 V

M 5

F F = (AB + CD)’

When the function equal 1 there is no problem M M Since there is no path to ground and the PMOS A 1 3 C charges the output node to Vdd. Voff = Vdd M M B 2 4 D When the output is to be low we have a problem since there will be a path from Vdd to ground, and hence the output voltage will depend on the ratio Zpu/Zpd

Consider an inverter: When the output is low the PMOS is saturated. Since Vds < Vgs-Vtp Now assuming that VOL =0.5 V which is a reasonable Vdd value since it is less than Vtn. VOL < Vtn then the NMOS will be in linear region Vds < Vgs – Vt Vout

Idp(sat) = In (linear) Vin 2 p/2[Vgs –Vtp]2 = n[(Vgs – Vt)VOL – VOL /2]

Assuming Vgs =5V and Vtp=Vtn = 1V

2 2 2 p/2 (4) = n[(4) VOL – VOL /2] we can neglect VOL /2 2 p/2 (4) = n(4) VOL

VOL 2p/n = 2 (Kp’ Wp/Lp)/(Kn’ Wn/Ln) Let Lp= Ln =3m =2 (Kp’ /(Kn’)(Wp/Wn)

VOL = (2/3) (Wp/Wn)

Let VOL = 0.5V Wp/Wn = (3/2)(1/2) =3/4 Wp = (3/4)Wn

Page 6 of 7 Assignment #5 2004 Let Wn = 4 m Wp = 3 m Vdd

3 Voff = Vdd Vout VOL 0.5V Vin 4

We can use this equivalent inverter to size the gate

Vdd = 5 V

3 VOH = 5 V F VOL = 0.5 V

8 8 A C

8 8 B D

Page 7 of 7 Assignment #5 2004