ELEC 351L Electronics II Laboratory Spring 2002

Lab 5: JFET Common-Source Amplifier

Introduction

The common-source amplifier is the FET analog of the common-emitter amplifier. As in the BJT circuit, the design of a FET-based amplifier involves both biasing and small-signal modeling. Whether the device used is a MOSFET or a JFET, the biasing and small-signal analysis of the common-source amplifier are essentially the same. The only major difference is that the gate-source voltage vGS of the JFET cannot be allowed to rise above zero volts, whereas the MOSFET has no such restriction. (You should know why.) In this lab experiment you will investigate the operation of a JFET common-source amplifier with source degeneration.

Theoretical Background

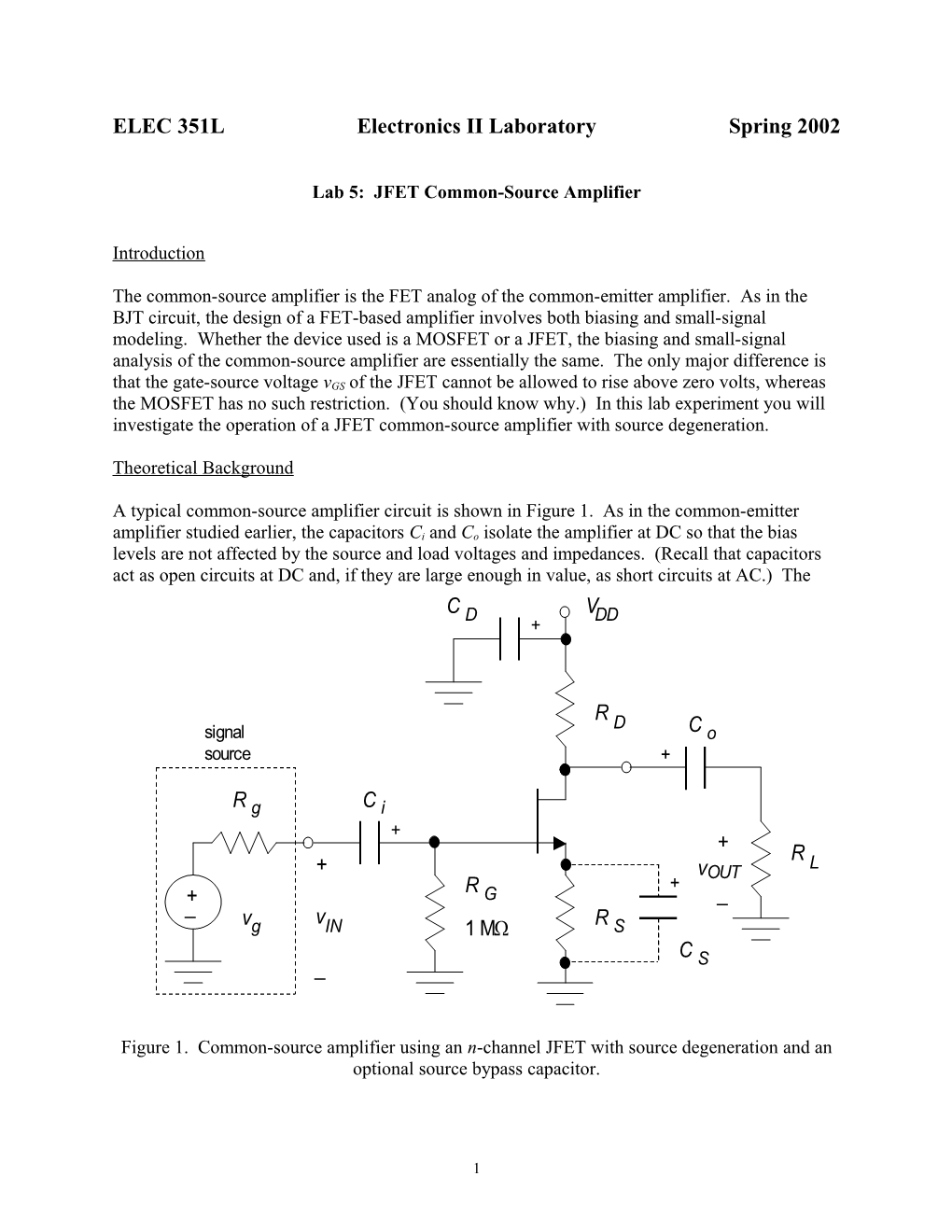

A typical common-source amplifier circuit is shown in Figure 1. As in the common-emitter amplifier studied earlier, the capacitors Ci and Co isolate the amplifier at DC so that the bias levels are not affected by the source and load voltages and impedances. (Recall that capacitors act as open circuits at DC and, if they are large enough in value, as short circuits at AC.) The

C D VDD +

R D signal C o source +

R g C i + + R L + vOUT + R G _ _+ v v R g IN 1 M S C _ S

Figure 1. Common-source amplifier using an n-channel JFET with source degeneration and an optional source bypass capacitor.

1 gate resistor RG is set to 1 M in order to provide a stable and resistive yet large input impedance. Note that a third capacitor is indicated across the source resistor and fourth across the power supply. Capacitor CS has no effect on the DC bias levels, but if it is large enough, it shorts out the resistor RS at AC and effectively connects the source directly to ground. As we will see, this increases the gain of the amplifier by a moderate amount. Capacitor CD also has no effect on the DC bias levels. Its purpose is to bypass the power supply at signal frequencies. This is good design practice, since power supplies (and batteries) don’t always provide low- impedance paths to ground for signals. Also, bypass capacitors short to ground any stray signals that may enter the circuit via long power supply leads.

As usual, we are interested in the small-signal voltage gain of the amplifier given by

vout av . vin

Note that this equation involves only signal voltages, not bias or total voltages. To find the gain in terms of resistor values and device parameters, we replace the JFET in the circuit with its small-signal model as shown in Figure 2. Note that JFETs are voltage-controlled devices; the dependent current source between the drain and the source has a value that depends upon the gate-source voltage. Also note that the path from the gate to the source is an open circuit; there is a voltage drop across it (vgs), but no current flows through it.

R g G D

+ + + v g v _ gs m gs + vg vIN R G _ vout R || R _ D L _ S signal source

R S

Figure 2. Small-signal model of common-source amplifier. If a source bypass capacitor is present, the source should be connected directly to ground.

2 The output voltage is given by

vout gmvgs RD RL ,

and vgs can be found by writing a KVL equation for the “input loop,” which involves the input voltage vin, the gate-source voltage vgs, and the source resistor RS. The resulting equation is

vin vgs gmvgs RS ,

which can be solved for vgs to give

vin vgs . 1 gm RS

Substituting this result into the equation for vout yields the formula for the small-signal voltage gain,

vout gm RD RL av . vin 1 gm RS

If gmRS >> 1, this equation simplifies and becomes independent of the parameter gm. However, because the transconductance (gm) of a typical JFET is relatively low, this assumption is not usually valid. Since the gain of the amplifier cannot generally be made independent of gm, the usual practice is to bypass the source resistor at AC using a capacitor (labeled CS in Figure 1). The effect of the capacitor is to make the source resistance equal to zero at AC, so the voltage gain becomes

av gm RD RL .

This can be substantially higher than the gain obtained with the source resistor active at AC. Bypassing the source resistor also simplifies the biasing, because the source resistor value does not have to satisfy simultaneously a small-signal voltage gain target and a bias current target.

Finally, if RL >> RD, then RD||RL RD, and the gain is

av gm RD .

The transconductance gm of the JFET is found via

iD I DSS 2 2I DSS 2I DSS gm 2 vGS VP 2 vGS VP 2 VGS VP . vGS vGS VP VP VP VGS ,I D VGS ,I D VGS ,I D

The subscripts “VGS, ID” indicate that gm is evaluated at the quiescent values of vGS and iD. The formula above is based only upon the quiescent value of vGS (that is, VGS). Usually the quiescent

3 value of iD (that is, ID) is specified instead; thus, an alternate formula for gm is needed. This is accomplished by starting with the relationship between ID and VGS, which is given by

I DSS 2 I D 2 VGS VP . VP

Solving for VGS yields

2 VP I D VGS VP , I DSS

which, upon substitution into the first equation for gm, leads to

2 I DSS I D gm . VP

We now have all of the design equations we need to determine the small-signal and bias quantities of interest. Including the biasing equations derived in an earlier experiment, the equations are (assuming that a bypass capacitor is used across RS, and that RL >> RD):

1. small-signal voltage gain: av gm RD

2 I DSS I D 2. JFET transconductance: gm VP

VDD VOUT 3. drain resistor value: RD I D

V I R P 1 D 4. source resistor value: S I D I DSS

where the substitutions ID = iD|Q and VOUT = vOUT|Q have been made in the two resistor formulas. (The bias voltages and currents are the quiescent voltages and currents; the two terms are synonymous.)

In a typical design, a target voltage gain av is usually the most important goal. Ranges of values for IDSS and VP are obtained from the data sheet, and nominal values for the two parameters are selected either by simply taking the average of the data sheet values, by screening the available stock of JFETs for devices that have parameters close to the desired values, or by using some other selection criterion. The quiescent output voltage is typically set to a value at or slightly above 0.5VDD. The main reason for selecting this value is to place the operating point near the middle of the “swing range” of the output voltage, which helps prevent the JFET from being

4 driven into the cut-off or triode region even if the values of IDSS and VP are far off from their assumed values. Recall that a JFET is in its constant current region only when VDS > VGS - VP; a large value of VOUT helps to ensure a large enough value of VDS to satisfy the inequality.

It remains next to set an appropriate value for ID. One approach is to note from the design equations above that the voltage gain depends only upon gm and RD, each of which is a function of only ID once VOUT is set and likely values of the parameters IDSS and VP have been chosen. Substituting the formulas for gm and RD into the formula for the voltage gain gives the result

2 I DSS I D VDD VOUT 2 I DSS VDD VOUT 1 av gm RD , VP I D VP I D

which, when solved for ID, yields

2 4I DSS VDD VOUT I D 2 2 . avVP

This value of ID is then used to find the values of resistors RD and RS. Once the design procedure is completed, it is necessary to check that the JFET does in fact operate in the CCR, that the quiescent gate-source voltage is greater than VP, and that the quiescent drain current has a reasonable value (for example, less than the minimum possible value of IDSS).

One disadvantage of the approach just described is that one or more bias levels or resistor values may not be satisfactory. For example, a value of RS could be obtained that is too small to produce sufficient negative feedback to control the bias point. More flexibility can be achieved by using the design technique shown in Figure 3. The drain resistance RD can be distributed

VDD

RD1

RD2 Cbypass

Figure 3. Design technique that allows different values of RD to be applied in the bias (DC) and small-signal (AC) analysis cases of an amplifier circuit.

5 among two resistors. The upper resistor (RD1) is bypassed at AC, which creates a smaller effective value for RD (RD2) at AC than at DC. This trick can also be used with resistor RS.

Recall that the value of ID cannot be set precisely because the parameters IDSS and VP fall within a wide range of values. As mentioned in an earlier handout, in practice this is not usually a problem because precise control of the voltage gain is often not required. The voltage gain of the common source amplifier, which is given by gmRD, varies with the value of gm, which in turn varies as the square root of ID. Thus, a 4:1 variation in ID would yield a 2:1 variation in gain. A variation of that amount is often quite tolerable.

Experimental Procedure

Construct a common-source amplifier circuit with source degeneration like the one shown in Figure 1. Use an MPF-102 n-channel JFET for the active device, include the source bypass capacitor CS, and use a power supply voltage VDD of 12 V. Design the amplifier for a small- signal voltage gain of –10 and a quiescent output voltage of 6 V for the case when the source resistor is bypassed at AC. Use an initial load resistance RL of 100 k. Base your bias design upon the average values of IDSS and VP you measured in the FET biasing lab or upon the values given by the lab instructor. You should solve for the quiescent drain current first as described above. For each resistor in the circuit, use the closest standard value to the one you calculate. For all of the bypass and DC blocking capacitors use values of 10 F or higher (but no more than 100 F, or so). Calculate the reactance of all capacitors. In your lab notebook clearly outline the design procedure you use. The pin-out of the MPF-102 is shown in Figure 4.

Lead identification for MPF-102 in TO-92 package (top view)

D S G

Figure 4. Identification of terminals for MPF-102 n-channel JFET.

Set the function generator to produce a sinusoidal source voltage vg at a frequency of around 1 kHz, and apply the voltage to the input of the amplifier. Simultaneously monitor the input (vin) and output (vout) AC voltages on the oscilloscope. Initially set the amplitude of vg to 50 mVpp, and record the resulting input and output voltages. Calculate the small-signal voltage gain av. Increase vg in small steps, and at each one record vin, vout, and av. Continue to increase vg until the voltage gain begins to drop significantly in value. The value of av should have been nearly constant up to this point. Sketch or print out a plot of vout vs. vin. Include axis labels, units, legends, title, etc. as appropriate. Comment on the measured value of av compared to the design value, and offer an explanation for why the gain changes when vin rises above a certain point. Also comment on any output waveform distortion that you may notice.

6 Remove the bypass capacitor CS, and measure the voltage gain with the amplifier in the linear region. (You will need to check where the linear region is for the new circuit configuration.) Compare the new value of av with the old value (when RS was bypassed). How does the new measured value compare with the calculated value obtained using the gain formula for nonzero RS?

Reconnect the source bypass capacitor to the circuit. With the input voltage set to a value at which the amplifier operates well within its linear range, decrease the value of RL until the AC output voltage drops to half the value obtained with RL = 100 k. Record the resistor value. This is the output resistance (Thévenin equivalent resistance) of the amplifier. Do you notice anything special about this value?

7